# Jian-Jia Chen Editor

# A Journey of Embedded and Cyber-Physical Systems

Essays Dedicated to Peter Marwedel on the Occasion of His 70th Birthday

A Journey of Embedded and Cyber-Physical Systems

Jian-Jia Chen Editor

# A Journey of Embedded and Cyber-Physical Systems

Essays Dedicated to Peter Marwedel on the Occasion of His 70th Birthday

*Editor* Jian-Jia Chen Dortmund, Germany

#### ISBN 978-3-030-47486-7 ISBN 978-3-030-47487-4 (eBook) https://doi.org/10.1007/978-3-030-47487-4

© The Editor(s) (if applicable) and The Author(s) 2021. This book is an open access publication. **Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG. The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

Dedicated to Prof. Peter Marwedel

## Foreword

Professor Dr. Peter Marwedel has made many invaluable contributions to research in the Electronic Design Automation area and specifically to the field of Embedded System Design. Already in his young years, he placed a landmark in the field of high-level synthesis and hardware description languages. In the mid-1970s, he started to work on high-level synthesis-almost a decade before it became mainstream. Peter Marwedel also laid ground for the field of retargetable compilation, which he considered as a special case of high-level synthesis in which the architecture was fixed. He designed the very first approach for generating a compiler from a description of the processor architecture and published this work already in the early 1980s—long before compilers were an accepted topic at EDA conferences. In the early 1990s, Peter Marwedel realized that compilers for embedded processors will become a crucial element in the toolchain for designing efficient embedded systems. One of his most prominent activities in the area of compilers for embedded systems is that of energy-aware compilation where he considered the energy efficiency of compiled code. His work on exploiting scratchpad memories for improving energy efficiency is well-known throughout the world. His engagement in memory-architecture aware compilation is highly influential and can be seen as an early contribution towards green computing.

In addition to being an outstanding researcher, Peter Marwedel has also proven himself as a great educator and passionate teacher in the classroom. This is best evidenced by his textbook "Embedded System Design" which has become standard literature in higher-level education on Embedded Systems for over a decade now. His excellence in teaching is documented, e.g., by the invitation of the Advanced Institute of Information Technology (AIIT) to give a 1-week compact course on embedded system design to Korean professors in Seoul in 2008 or by an invited talk on embedded system education during the cyber-physical systems program at the annual meeting of the US National Science Foundation (NSF).

While this Festschrift features a variety of contributions from his peers in the professional community, we would like to take this opportunity to emphasize Peter Marwedel's role as an exemplary advisor for his students, all the way from freshmen studying for their BS and MS degrees to PhD graduates and rising university

professors. His dedicated mentorship and valuable advice has had a tremendous impact on many careers, as the following personal quotes show:

Back in July 1995, I was a student at the University of Dortmund, working hard to complete my diploma thesis. At that time, my advisor Prof. Marwedel left Dortmund for a sabbatical at the University of California. I vaguely remember the day when he sent me an email, asking me if I would be interested to study for PhD in the USA. It took me less than 5 min to respond with 'No, thank you!' as I had always envisioned to spend my life and work in Germany. Nine days later Peter Marwedel changed my life with a second email that essentially read 'Think twice!'. So I did. Long story short, I moved to California and live there since. I will be forever grateful for that second email which opened up a once-in-a-lifetime opportunity for my successful career. Thank you!

Rainer Dömer (Professor, University of California at Irvine, USA)

I got in touch with Peter Marwedel's chair for the first time in 1996 in the context of my student project work on HW/SW co-design and FPGA synthesis. With my successful graduation 1998, Peter offered me a PhD position in his group so that I had the chance to collaborate with the IMEC in Leuven on high-level source code optimization techniques. Having completed my PhD in 2004, Peter continued to support me so that I was able to establish a team working on compilers for real-time systems. Besides this excellent mentorship for more than a decade that finally led my to my current professorship at TUHH, I always appreciated Peter Marwedel's team spirit very much. Besides professional activities, team building was always very important for him, leading to countless memories of garden parties, barbecues with students in his chair's backyard, bicycle tours, workshops in the middle Rhine Valley, etc. This high degree of support and friendship is extraordinary and I am happy about the opportunity to say thank you to Peter Marwedel in this Festschrift.

Heiko Falk (Professor, Hamburg University of Technology, Germany)

Even though I started as a postdoc in Peter Marwedel's research group in 2010, I was able to learn a lot from his decades of experience in teaching, scientific writing, and designing research proposals. We were always eager to experiment with new approaches, such as flipped classroom teaching, and to explore new research topics. All of this has had a significant influence on my current work as professor at Coburg University. The extensive research on compilers in Peter's group also contributed to obtaining my new position at NTNU. An invaluable benefit when working in a large, well-funded research group was that I got to travel to so many interesting places and meet colleagues from all around the world. Traveling was also a common topic on the private level, since Peter loves to travel and to photograph. I fondly remember many hours of browsing through Peter's diligently prepared photo albums and listening to the stories of his trips. Going to Norway, I hope that I can provide an exciting destination for an upcoming trip. Thanks a lot for everything, Peter, and see you soon in Trondheim!

Michael Engel (Professor, NTNU, Trondheim, Norway).

Numerous anecdotes just like these could be added here, but that would fill an entire book by itself. So without further ado, we conclude this foreword here with a big THANK YOU to Peter Marwedel.

Workshop at TU Dortmund, July 2019

Rainer Dömer Heiko Falk Michael Engel

# Acknowledgements

The workshop on embedded systems, dedicated to Peter Marwedel on the occasion of his 70th birthday, and its festschrift have been partially supported by Deutsche Forschungsgemeinschaft (DFG), Collaborative Research Center SFB 876 (http://sfb876.tu-dortmund.de/), and Alumni der Informatik e.V. TU Dortmund.

# Contents

| 1 | Peter Marwedel and the Department of Computer Scienceof the TU Dortmund UniversityGernot Fink and Heinrich Müller                                                                                             | 1   |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | <b>Testing Implementation Soundness of a WCET Analysis Tool</b><br>Reinhard Wilhelm, Markus Pister, Gernot Gebhard,<br>and Daniel Kästner                                                                     | 5   |

| 3 | The Dynamic Random Access Memory Challengein Embedded Computing SystemsMatthias Jung, Christian Weis, and Norbert Wehn                                                                                        | 19  |

| 4 | On the Formalism and Properties of Timing Analyses<br>in Real-Time Embedded Systems                                                                                                                           | 37  |

| 5 | ASSISTECH: An Accidental Journey into Assistive Technology<br>M. Balakrishnan                                                                                                                                 | 57  |

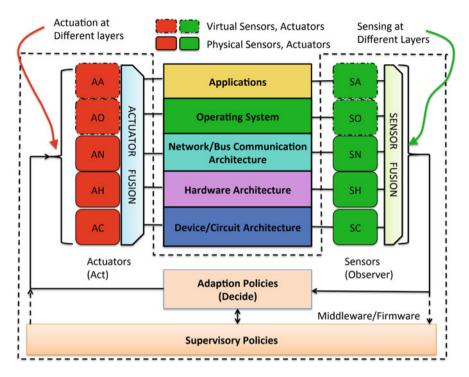

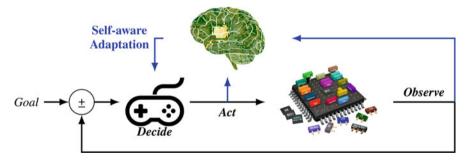

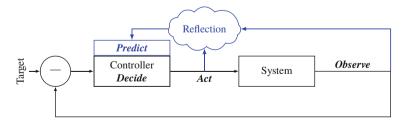

| 6 | <b>Reflecting on Self-Aware Systems-on-Chip</b><br>Bryan Donyanavard, Tiago Mück, Kasra Moazzemi, Biswadip<br>Maity, Caio Batista de Melo, Kenneth Stewart, Saehanseul Yi,<br>Amir M. Rahmani, and Nikil Dutt | 79  |

| 7 | Pushing the Limits of Parallel Discrete Event Simulationfor SystemCRainer Dömer, Zhongqi Cheng, Daniel Mendoza, and Emad Arasteh                                                                              | 97  |

| 8 | Impact of Negative Capacitance Field-Effect Transistor(NCFET) on Many-Core SystemsHussam Amrouch, Martin Rapp, Sami Salamin and Jörg Henkel                                                                   | 107 |

| 9   | Run-Time Enforcement of Non-functional Program Properties<br>on MPSoCs                                                                                                         | 125 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Jürgen Teich, Pouya Mahmoody, Behnaz Pourmohseni,                                                                                                                              |     |

|     | Sascha Roloff, Wolfgang Schröder-Preikschat,                                                                                                                                   |     |

|     | and Stefan Wildermann                                                                                                                                                          |     |

| 10  | <b>Compilation for Real-Time Systems a Decade After PREDATOR</b><br>Heiko Falk, Shashank Jadhav, Arno Luppold, Kateryna Muts,<br>Dominic Oehlert, Nina Piontek, and Mikko Roth | 151 |

| Ind | ex                                                                                                                                                                             | 171 |

## Contributors

Hussam Amrouch Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

**Emad Arasteh** Center for Embedded and Cyber-Physical Systems, University of California, Irvine, CA, USA

M. Balakrishnan Indian Institute of Technology Delhi, Delhi, India

Jian-Jia Chen TU Dortmund, Dortmund, Germany

Kuan-Hsun Chen TU Dortmund, Dortmund, Germany

**Zhongqi Cheng** Center for Embedded and Cyber-Physical Systems, University of California, Irvine, CA, USA

Bryan Donyanavard University of California, Irvine, CA, USA

**Rainer Dömer** Center for Embedded and Cyber-Physical Systems, University of California, Irvine, CA, USA

Caio Batista de Melo University of California, Irvine, CA, USA

Nikil Dutt University of California, Irvine, CA, USA

**Heiko Falk** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

Gernot Fink TU Dortmund, Dortmund, Germany

Gernot Gebhard AbsInt Angewandte Informatik GmbH, Saarbrücken, Germany

Jörg Henkel Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

Wen-Hung Huang TU Dortmund, Dortmund, Germany

**Shashank Jadhav** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

Matthias Jung Fraunhofer IESE, Kaiserslautern, Germany

Daniel Kästner AbsInt Angewandte Informatik GmbH, Saarbrücken, Germany

**Arno Luppold** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

**Pouya Mahmoody** Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Biswadip Maity University of California, Irvine, CA, USA

**Daniel Mendoza** Center for Embedded and Cyber-Physical Systems, University of California, Irvine, CA, USA

Kasra Moazzemi University of California, Irvine, CA, USA

**Kateryna Muts** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

Tiago Mück University of California, Irvine, CA, USA

Heinrich Müller TU Dortmund, Dortmund, Germany

**Dominic Oehlert** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

**Nina Piontek** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

Markus Pister AbsInt Angewandte Informatik GmbH, Saarbrücken, Germany

**Behnaz Pourmohseni** Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Martin Rapp Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

Amir M. Rahmani Technische Universität Wien, Vienna, Austria

Sascha Roloff Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

**Mikko Roth** Institute of Embedded Systems, Hamburg University of Technology (TUHH), Hamburg, Germany

Sami Salamin Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

**Wolfgang Schröder-Preikschat** Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Kenneth Stewart University of California, Irvine, CA, USA

Jürgen Teich Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Niklas Ueter TU Dortmund, Dortmund, Germany

Georg von der Brüggen TU Dortmund, Dortmund, Germany

Norbert Wehn TU Kaiserslautern, Kaiserslautern, Germany

Christian Weis TU Kaiserslautern, Kaiserslautern, Germany

**Stefan Wildermann** Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Reinhard Wilhelm Universität des Saarbrücken, Saarbrücken, Germany

Saehanseul Yi University of California, Irvine, CA, USA

# Chapter 1 Peter Marwedel and the Department of Computer Science of the TU Dortmund University

Gernot Fink and Heinrich Müller

#### 1.1 Introduction

Peter Marwedel was appointed Professor at the Department of Computer Science of the University of Dortmund in 1989. He represented the area "Computer Engineering and Embedded Systems" and headed the Chair of Computer Science 12 until his retirement in 2014. During this time, he has made a great contribution to the Department of Computer Science, which continues to have a lasting effect today. The following presentation is intended to give an idea of the extraordinary breadth and importance of his activities in teaching, academic self-government, basic research, and technology transfer.

#### 1.2 Teaching

A special passion of Professor Marwedel is teaching, which is not self-evident for a dedicated and successful researcher. In Dortmund, he was extremely involved in basic teaching, which is particularly challenging given the high number of students attending these courses. For many years he has held the introductory compulsory lecture "Computer Structures" and the elective lectures "Embedded Systems" and "Computer Architecture." Through these courses, he has substantially contributed to the basic training in technical computer science. His lectures were extremely well prepared. The material was thoughtfully selected in all details, didactically carefully prepared, and presented objectively and clearly. The courses have gained a high

TU Dortmund, Dortmund, Germany

G. Fink · H. Müller (⊠)

e-mail: Gernot.Fink@tu-dortmund.de; heinrich.mueller@cs.uni-dortmund.de

reputation among the students. This was reflected in consistently excellent student ratings and led to Professor Marwedel receiving the prestigious Teaching Award of TU Dortmund University in 2003.

From the course "Embedded Systems" the first edition of the English textbook "Embedded System Design" emerged in 2003. The book has established itself as an international textbook and is often cited. Professor Marwedel has adapted it over the years to current developments. The third edition has been published in 2018.

In addition to traditional teaching, Professor Marwedel has shown great interest in the possibilities of new media and has made strong use of it. On YouTube he has made available a significant number of educational videos that are particularly associated with his courses "computer structures" and "computer architecture." The design of the videos focuses on the essentials and avoids superfluous, distracting visual effects.

In his last active years at the department, Professor Marwedel experimented with the concept of the inverted classroom as a natural consequence. This form of teaching is still little used at German universities.

Particularly noteworthy is the fact that Professor Marwedel has conveyed his concept of education in the field of embedded systems beyond its actual implementation. It was the subject of the Workshop on Embedded and Cyber-Physical System Education (WESE) organized by him in Finland in 2012. In the same year, he was invited to the annual meeting of the cyber-physical systems program of the prestigious National Science Foundation (NSF) in Washington, USA, where he gave a talk focusing on the Dortmund education concept in the field of Embedded Systems.

Finally, it should be mentioned that Professor Marwedel contributed to the internationalized teaching of the Department by participating in the English Master's program "Automation and Robotics" of the TU Dortmund University and his contacts to Indian Institutes of Technology, which have led to internships of Indian students in Dortmund.

#### **1.3 Academic Self-Government**

Professor Marwedel has always been active in the Department's academic administration and beyond. He was Dean of Studies of the Department and member of the Academic Senate of TU Dortmund. But here, too, his commitment to teaching is particularly reflected. He was chairman of the teaching committee of the Department and chairman of the educational committee of the Academic Senate of the university. He was Dean of Studies of the Department from 2012 to 2014. Beyond the university, he has worked on standards for the accreditation of computer science curricula in the national organizations ASIIN and AVI.

#### 1.4 Basic Research and SFB 876

Professor Marwedel has contributed significantly to the international visibility of the Department of Computer Science through his research in embedded and cyberphysical systems. He has received several international honors, in particular the EDAA Lifetime Achievement Award (2013), the ESWEEK Lifetime Achievement Award (2014), and the ACM SIGDA Distinguished Service Award (2014). In 2010 he became an IEEE Fellow and a Fellow of the Design, Automation and Test Conference in Europe (DATE).

A very special contribution to research at the Department and the university was made by Professor Marwedel as co-initiator of the Collaborative Research Center (CRC/SFB) 876, together with the main initiator Prof. Dr. Katharina Morik, spokeswoman for the CRC. The CRC program of the Deutsche Forschungsgemeinschaft (DFG) enjoys a high reputation and is extremely competitive. The topic of the SFB 876 is "Providing Information by Resource-Constrained Data Analysis." The collaborative research center SFB 876 brings together data mining and embedded systems. On the one hand, embedded systems can be improved using machine learning. On the other hand, data mining algorithms can be realized in hardware, e.g. FPGAs, or run on GPGPUs. The restrictions of ubiquitous systems in computing power, memory, and energy demand new algorithms for known learning tasks. At the time of the application, merging data analysis and resource constraints was visionary-today it is highly relevant in many applications. In the SFB 876, about 20 research groups of the Department, of TU Dortmund University, and of neighboring universities are working together since 2011 for 12 years in an interdisciplinary manner.

#### 1.5 Technology Transfer and ICD

Professor Marwedel has not only been active in basic research, but has also dealt with applied research and the transfer of scientific results to the economy. For many years he is CEO of the "Informatik Centrum Dortmund e.V." (ICD) and head of the Embedded Systems Group at ICD. The ICD was founded in 1989 from the Department of Computer Science at the University of Dortmund. The ICD is available to companies from all sectors of the economy. Its goal is to accelerate the transfer of current research results in computer science and information technology into industrial products. Under Professor Marwedel's leadership, the ICD has become a well-established, successful, and economically stable association.

#### 1.6 Conclusion

The Department of Computer Science is extremely grateful to Professor Marwedel. On the occasion of his seventieth birthday, it wishes him all the best for the future. **Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

## Chapter 2 Testing Implementation Soundness of a WCET Analysis Tool

Reinhard Wilhelm, Markus Pister, Gernot Gebhard, and Daniel Kästner

#### 2.1 Introduction

*Timing verification* of a set of hard real-time tasks to be executed on a given hardware platform attempts to prove that all tasks in the set when executed on that platform always respect their deadlines, i.e., each task finishes its execution within its deadline. Traditionally, timing verification is split into two subtasks: a *timing analysis* also known as *WCET analysis*, which statically determines upper bounds on the execution times of the tasks, and a *schedulability analysis*, which takes these upper bounds and attempts to verify that all tasks in the given set, assuming these upper bounds on their execution times, will respect their deadlines.

A preliminary version of this paper appeared in [16].

R. Wilhelm (🖂)

M. Pister · G. Gebhard · D. Kästner

AbsInt Angewandte Informatik GmbH, Saarbrücken, Germany e-mail: pister@absint.com; gebhard@absint.com; kaestner@absint.com

Universität des Saarbrücken, Saarbrücken, Germany e-mail: wilhelm@cs.uni-saarland.de

#### 2.1.1 Tool Qualification

WCET analysis is applied to time-critical and safety-critical embedded-system software in problem-aware parts of the embedded-systems industry. Such systems have to be developed in accordance with international safety norms, e.g., DO-178B/C, DO-254, IEC 61508, and ISO 26262. While there are differences between these norms, in particular regarding prescriptiveness and required level of rigor, they have many aspects in common. All of them include guidance on the use of software tools as a part of the development and verification process of safety-critical software.

The criticality level (also known as the design assurance level (DAL) or safety integrity level (SIL)) of a component determines the effort to invest and the methods required or recommended to deliver assurance of the correct functioning of the component. The criticality level is derived from the impact of a failure of the component on the functioning of the system. Similarly, the required activities to provide confidence in the correct functioning of a software tool depend on its criticality with respect to the overall system. For example, DO-178C, the current international standard for avionics systems, defines five different *tool qualification levels (TQLs)*. The TQL is determined by the potential tool impact and the design assurance level of the software. There are three tool-impact categories; the most critical, *Category 1*, applies to tools whose output becomes part of the airborne software. Similar considerations are also made in other norms, e.g., the ISO 26262 defines a *tool confidence level (TCL)* in a very similar way.

The overall goal of tool qualification is to provide confidence that the tool operates correctly, i.e., according to its functional specification, in the operational context of the tool user. In the following, we will focus on the tool qualification requirements of the avionics industry, which are the most rigid of the safetycritical industries. Certification of avionics systems is regulated by the international standard DO-178C [1]. WCET analysis tools fare under verification tools. Verification tools have no overly rigid certification requirements, unlike development tools: their impact category is Category 2 or Category 3, mostly depending on whether the output of the tool is used to justify the elimination or reduction of other verification or development activities or not. A prerequisite for tool qualification is a specification of the tool functionality. The tool operational requirements (TOR) specify the tool functions and technical features, which are stated as low-level requirements on tool behavior under normal operating conditions. Another required input is the verification test plan (VTP), which defines test cases demonstrating the correct functioning of all specified requirements of the TOR. Test-case definitions include the overall test setup as well as a detailed structural and functional description of each test case, i.e., how the individual test case works and what the expected result is.

Certification becomes more challenging through DO-333, the formal-methods supplement to DO-178C. It asks for a statement that a formal method including the underlying theory is *adequate* for solving the corresponding verification problem. This introduces and enforces *soundness* of the methods and tools.

Since the required effort for tool qualification can be high, ideally the software qualification process is supported by a *qualification support kit (QSK)* supplied by the tool provider. It must include TOR and VTP and typically provides a validation suite, which allows users to execute the relevant test cases in the relevant operational context. TOR, VTP, and a test execution report become part of the certification package. Furthermore, it is typically required for a tool provider to supply *qualification software life cycle data* to demonstrate that the development process and the invested efforts to assure correctness, quality, and traceability are adequate for usage in a safety-critical system context. The qualification software life cycle is not covered in this article.

DO-178C exhales a test-based spirit: many verification activities are test based. Well-defined coverage criteria try to capture to which extent the behavior of the system under test has actually been exerted during testing. Note that in case of a static verification tool, test coverage does not apply to the code to be analyzed: a sound static-analysis tool provides full data and control coverage, i.e., it analyses all paths and takes into account all potential data values for its analyses. What is needed in case of the microarchitectural analysis, which is the focus of this article, is to demonstrate the correctness of the microarchitecture model used by the analyzer. To this end it is the instruction set architecture (ISA) and the set of paths through the execution platform that need to be covered. Huge sets of test traces in qualification suites are used at tool-qualification time to cover the sets of paths through the execution platform.

Note the difference to measurement-based WCET analyses. It is known that they are in general unsound. In order to provide a sufficient level of confidence in the real-time behavior of industrial-size code they need an unacceptably huge set of traces and accordingly an excessive effort at verification time. In the case of a static WCET analysis tool, the testing effort is applied at tool-qualification time when ample time is available.

#### 2.1.2 Predictability

Timing predictability [3, 15] has long been recognized as essential for achieving precise results of timing estimation at reduced analysis effort. In the context of the current article, it is worth mentioning that it also reduces the number of test cases for the validation of an abstract architectural model. In general, an increase in the timing predictability of the underlying architecture leads to a decreasing number of different instruction flow paths through the processor pipeline since they feature less average-case performance-enhancing micro-optimizations like instruction and data queues and buffers, data forwards, etc. Such architectures show a more regular hardware design.

#### 2.1.3 WCET Analysis

Performance-enhancing architectural components such as caches, pipelines, and speculation have made WCET analysis difficult. Execution times of consecutively executed instructions do not compose easily because instruction execution times are now dependent on the execution state in which they are executed. In the composition A;B the execution time of statement B depends on the execution state produced by executing statement A. The variability of execution times grows with several architectural parameters, e.g., the cache-miss penalty and the costs for pipeline stalls and for control-flow mispredictions. As approaches using exhaustive measurements are infeasible due to the size of the search space, abstraction is applied leading to an over-approximation of the set of potential executions. This over-approximation introduces remaining uncertainty in the results of the microarchitectural analysis, which grows with the same architectural parameters mentioned above unless the architectural platform is predictable [18], see Sect. 2.1.2.

#### 2.1.4 The Central Idea: Proving Safety Properties

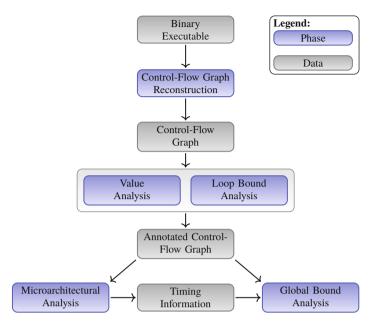

We needed to solve the WCET problem for architectures with state-dependent execution times. Figure 2.1 shows that this problem could be decomposed into many subproblems. The main problem, specific for WCET analysis, was the *microarchitectural analysis*, a combined cache and pipeline analysis. Let us describe the central idea behind this phase in our WCET analysis method [17], first in a conceptual way, i.e., not quite like it is implemented, later closer to how it is implemented:

• We define any architectural effect that causes an instruction to execute longer than its fastest execution time to be a *timing accident*. Typical such timing accidents are cache misses, pipeline stalls, bus-access conflicts, or branch mispredictions. Each timing accident is associated with a *timing penalty*. Timing penalties may be constant, but may also be execution-state dependent. A cachemiss penalty may be constant if the bus is always guaranteed to be free for the cache reload. If this guarantee cannot be given, however, its size depends on the execution state, namely whether the bus happens to be free.

The property that the execution of an instruction at some program point will not cause a particular timing accident is then a safety property. The occurrence of a timing accident thus violates a corresponding safety property.

• We then use an appropriate method for the verification of safety properties to prove that for the instructions in the program some of the potential timing accidents will never happen. The goal is to prove as many of such safety properties as possible. Conceptually, the safety properties shown to hold could be used to reduce the worst-case execution-time bound for an instruction, which a naive, sound WCET analysis would have to assume, by the cost for the excluded

Fig. 2.1 The architecture of the aiT tool

timing accidents. In practice, pipeline analysis drives a cycle-wise transition, which considers the abstract execution state, e.g., makes no transition under a cache miss if a cache miss can be excluded.

• We then prove these safety properties by abstract interpretation (AI) [4] in the following way: Compute invariants at each program point, in our case an overapproximation of the set of execution states that are possible when execution reaches this program point. Derive the above mentioned safety properties, that certain timing accidents will not happen, from these invariants. For example, AI computes an abstract cache state at each program point, which overapproximates the sets of concrete cache states that may reach this program point. The abstract cache states are used to classify some memory accesses as definite hits. Another cache analysis that underapproximates the set of possible concrete cache states is able to predict definite misses. Predicted cache hits are then used to prove that the timing accident, this memory access will miss the cache, will never happen [8, 10].

This method for the microarchitectural analysis was the main innovation that made our WCET analysis work for real-life architectures and scale to industrial-size software [6].

Now follows the description of the microarchitectural analysis that is closer to the implementation. Driver of this analysis is the pipeline analysis [14]. It goes through the instruction stream, instruction by instruction, and executes the current instruction in the current abstract execution state. This abstract execution state contains uncertainty, i.e., it lacks information about some state components. Transitions to all potential successor states are performed whenever the transition to the next state depends on such a missing part of the state. The timing contributions of these transitions are accumulated until an instruction can be retired. In the end, upper bounds on the execution times of basic blocks are obtained that are coefficients in an integer linear program representing the control flow of the program [17]. Another type of result is described below.

#### 2.1.5 Terminology

We consider only sound WCET analysis methods. Soundness means that a method and associated tool will always produce conservative WCET estimates, i.e., estimates that will never be exceeded in any execution. Being conservative is a Boolean property. Unfortunately, conservative is often used as a metric property, more conservative meaning less precise. However, calling results of an unsound method conservative is a misnomer. The really meant, other dimension, in addition to soundness, is accuracy. Accuracy of some WCET estimate, obtained by a sound method, expresses the degree of over-estimation, the difference between a WCET estimate and the real WCET. It does not make sense to talk about the accuracy of an unsafe estimate or an unsound method. In case of an unsound method it is not even clear whether a "more conservative" estimate moves towards the real WCET from below or is larger than the real WCET and moves further away from it. In general, WCET estimates are below, i.e., underestimate the real WCET, if endto-end measurements are used. On the other hand, if piecewise measurements are applied whose results are combined to an estimate of the overall execution times, this often results in over-estimation of the real WCET.

WCET analysis can be seen as the search for a longest path in the state space spanned by the program under analysis and by the architectural platform. Most realtime software is written as to guarantee termination. Its state space can thus be easily abstracted to a finite abstract state space, which is still too large to be exhaustively explored. We can, therefore, not expect to identify the real WCET, but only safe upper bounds to all execution times, which we will call WCET estimates. (Safe) over-approximation is used in several places. In particular, an abstraction of the execution platform is employed by the WCET analysis. How to convince oneself (or the certification authorities) of the correctness of this architectural model is the main subject of the next section.

#### 2.2 Validation of Our WCET Analysis Tool

The claim that our WCET analysis tools produce safe results is a strong one and often disputed by some proponents of unsound WCET analysis methods. Their

argument is, to develop an error-free instantiation of the, in principle, sound WCET analysis technology is so difficult, that one might use a simpler unsound method in the first place. The main complaint is the complexity of the abstract architectural models. So, what is the basis for our claims?

Several analyses in the tools are instances of abstract interpretation [4], a scientific method with a strong underlying theory, relating analysis results to semantic properties of analyzed programs. Value and loop bound analysis, c.f. Fig. 2.1, are more or less standard abstract interpretations. The difference is that these analyses are performed on the binary level and not on the source level. Still, adequacy of these analyses is easily accepted. The instantiation of the abstract-interpretation framework for the microarchitectural analysis of a given execution platform, however, is far from trivial. In particular, it contains an abstraction of the execution platform. How does one make sure that such an abstraction is conservative? This will be explained in Sect. 2.2.3.

Let us give short descriptions of the different component analyses alongside the particular validation activities before we come to the validation of the central component.

#### 2.2.1 Control-Flow Graph Reconstruction

The reconstruction of the control-flow graph (CFG) from a binary executable means to compute a safe approximation of the inter-procedural control flow of the executable [13]. This is achieved by the following two steps after having loaded the executable:

- Classification of the loaded byte stream to identify individual assembly instructions and

- 2. Recursive reconstruction of the control flow based on this assembly-instruction classifications.

For Step 1, a specification of the instruction encoding is required. Instructionset-architecture manuals provide this information, which is then used to implement instruction identification in the binary decoder of the aiT tool chain. To validate the implementation, we perform the so-called *decode* tests. For each supported instruction (in each supported addressing mode) we write a test case providing a reference as the expected result of the decoding. The decoding result is then compared to this reference.

In Step 2, the decoder uses the identified instruction stream to compose a safe control-flow approximation. To validate this, we compile a representative set of control structures (in a high-level language like C) and decode the resulting executable to compare the reconstructed control flow with a reference result.

#### 2.2.2 Value Analysis

The value analysis determines safe approximations of the values in processor registers and memory cells for every program point. These approximations are used to determine bounds on the iteration number of loops and information about the addresses of memory accesses. The value analysis is based on the instruction semantics of the underlying target architecture. Like the instruction encoding, architecture manuals provide this information.

To validate the instruction-semantics implementation, we create a test case for each instruction and define pre- and post-conditions according to the expected effect of the particular instruction. These conditions are expressed by user annotations, which are read by the value analyzer. Pre-conditions are used to generate the machine state needed to execute the tested instruction. The post-conditions define the expected state after having executed the instruction under test.

#### 2.2.3 Microarchitectural Analysis: Trace Validation

The microarchitectural analysis combines a cache and a pipeline analysis. It is an abstract interpretation of the program's execution on the underlying cache and pipeline architecture. The execution of a program is abstractly executed by feeding instruction sequences from the control-flow graph to the timing model, which then computes the changes of the abstract execution state at cycle granularity and keeps track of the elapsing clock cycles. The correctness proofs of the method have been conducted by Thesing [14] based on the theory of abstract interpretation.

The cache analysis described in [2, 5, 7] is incorporated into the pipeline analysis. At each memory access, where the concrete hardware would query and update the contents of the cache(s), the cache analysis applies the corresponding abstract cache effects to the abstract cache state.

The result of the microarchitectural analysis is either an upper execution-time bound for every basic block or a *prediction graph*. In the first case, these upper bounds are the coefficients in an integer linear program that represents the control flow of the program. This is the version usually described in publications about static WCET analysis, as it presents a clean work distribution. However, it has the disadvantage that too much information is lost at basic-block boundaries, namely the precise matching of final states at predecessor blocks to initial states at successor blocks. This loss of information entails a loss in precision. The prediction graph avoids this loss of precision. It consists of abstract states as nodes and edges for the transition between states and represents the evolution of the abstract execution states at processor-clock granularity and beyond basic-block boundaries. Note that in the description of trace validation a prediction event graph appears, which is the prediction graph extended by event annotations at its edges.

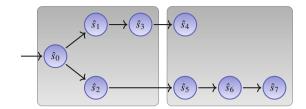

Fig. 2.2 Evolution of abstract hardware states  $\hat{s}_i$ . Each edge denotes a single cycle transition in the abstract state space. The gray boxes span the set of states that belong to the same basic block

As an example consider the prediction graph of Fig. 2.2, where the longest path is four transitions long, i.e., it takes four processor cycles to complete the program. Adding up the length of each longest path per basic block (denoted by the gray boxes) would neglect that there is no connection between the abstract states  $\hat{s}_3$  and  $\hat{s}_5$  and thus yield a worst-case estimate of five processor cycles.

Due to the complexity of the abstract architectural model, validation of the pipeline analysis cannot be done solely by testing the abstract implementation of individual instructions as we do it for CFG reconstruction and value analysis.

#### 2.2.3.1 Semi-Automatic Derivation of the Abstract Architecture Model

Nowadays, hardware circuits are automatically synthesized from formal hardware specifications like VHDL or Verilog. Besides a formalization of the functional details, such specifications implicitly contain an execution model that also reflects the timing behavior of the whole system. It was a tempting idea to derive a pipeline analysis from the formal hardware model such that analysis and synthesized circuit share the same basis [11, 12].

However, the semi-automatic derivation of a timing model approach has not proven effective in the industrial context. Even if the hardware manufacturers grant access to their formal models (which is often not the case), the derivation process requires to fully understand the design, which might be a complex task for a complete processor including peripheral devices. Additionally, the quality of the resulting analysis depends on the coding style of the hardware model [11]. Results are excellent if the code features minimal dependencies between processes, a clear logical separation of different functionality into different processes/subprograms and a sequential logic design. Ideally, the code reflects the structural composition of the processor pipeline with explicit control signals to steer the flow of instructions and data. Models not adhering to those design principles complicate state abstractions and thus result in prohibitively resource-consuming analyses.

#### 2.2.3.2 Trace Validation

For the reasons given above, the abstract architectural models are *hand-crafted* by human experts based on the available hardware reference documentation, which sometimes contains errors and usually lacks relevant details. Reverse engineering based on specific runtime measurements needs to fill this gap. Even if it were semi-automatically derived from a specification, the implementation of the microarchitectural analysis would still need to be validated. *Trace validation* checks for safe over-approximations of the predictions by matching observable hardware events recorded during concrete executions of instruction sequences against predictions of those events produced by the microarchitectural analysis. This is done for a sufficiently large set of instruction sequences that structurally covers the possible instruction flows (wrt. the different functional units, instructions, dependencies between instructions, etc.) of the processor pipeline.

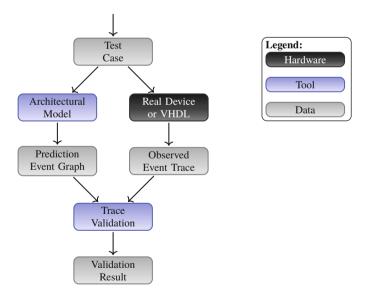

Figure 2.3 shows the trace-validation workflow. An instruction sequence is executed on the actual hardware, or its execution is simulated using a VHDL model, to obtain an *observed event trace*. The microarchitectural analysis is modified to predict those events and annotate them to the edges of the generated prediction graph. In this fashion the microarchitectural analysis of an instruction sequence generates a *prediction event graph* that describes an over-approximation of all possible event traces that could occur while executing the instruction sequence. The observed trace of events, the reached execution state, and the consumed time are

**Fig. 2.3** Trace validation according to [9]. The instruction sequences together with the generated prediction graphs annotated by state and timing information are part of the Qualification Support Kit

checked for containment in the prediction graph. Trace validation is successful if the sequence of traced events is found in the prediction graph, and their predicted execution time does not underestimate the observed execution time.

The granularity at which the comparison takes place strongly depends on the debug facilities provided by the hardware. At best, timer interrupts are used to stop execution after each execution cycle. This way, the execution of instruction sequences is extended cycle by cycle to observe actual execution states and execution times.

The behavior of some components of the architectural state, such as the cache state, is unfortunately not directly observable. These need to be indirectly observed through executions that are forced to lead to cache hits and cache misses.

Thus a tremendous effort is required to cover both all instructions and all architectural components. This is essentially achieved by triggering many different architectural states through the execution of dedicated test cases.

The validation suite of the AbsInt static WCET tool aiT may contain several hundred individual test cases, even for a simple DLX-like architecture like the ARM Cortex-M4. For multi-core architectures, such as the TriCore TC275, which features three different cores, several thousand test cases are necessary to cover all architectural features.

How many test cases are required to cover the whole architectural behavior correlates to the complexity of the analyzed hardware, i.e., with the number of available instructions of the instruction set architecture, the number of components of the pipeline architecture like functional units, internal buffers, queues, memories, buses, and their states. Often unexpected (undocumented) hardware behavior is exposed while trying to understand existing test cases. This leads to additional test cases. Hence, the number of test cases that are sufficient in order to cover the (timing) relevant hardware behavior cannot be easily quantified in advance.

#### 2.3 Conclusion

The AbsInt WCET analyzer aiT uses a combination of sound methods to derive safe upper bounds on execution times. Their implementation is quite complex, such that it is natural to query the soundness of the implementation of the technology. We describe the validation efforts employed to convince ourselves, the customers, and the certification authorities of the soundness of the implementation. The European Aviation Safety Agency (EASA), obliged to follow the strictest certification rules, those of DO178-C, has accepted AbsInt's aiT as a validated WCET analysis tool for several time-critical subsystems in the Airbus A380 and A350 planes.

#### References

- 1. Rtca/do-178c software considerations in airborne systems and equipment certification (2013)

- M. Alt, C. Ferdinand, F. Martin, R. Wilhelm, Cache behavior prediction by abstract interpretation. in *Proceedings of the Third International Symposium on Static Analysis, SAS'96*, ed. by R. Cousot, D.A. Schmidt. Aachen, September 24–26, 1996. Lecture Notes in Computer Science, vol. 1145 (Springer, Berlin, 1996), pp. 52–66. https://doi.org/10.1007/3-540-61739-6\_33

- P. Axer, R. Ernst, H. Falk, A. Girault, D. Grund, N. Guan, B. Jonsson, P. Marwedel, J. Reineke, C. Rochange, M. Sebastian, R. von Hanxleden, R. Wilhelm, W. Yi, Building timing predictable embedded systems. ACM Trans. Embedded Comput. Syst. 13(4), 82:1–82:37 (2014). https:// doi.org/10.1145/2560033

- 4. P. Cousot, R. Cousot, Abstract interpretation: a unified lattice model for static analysis of programs by construction or approximation of fixpoints, in *Conference Record of the Fourth ACM Symposium on Principles of Programming Languages*, ed. by R.M. Graham, M.A. Harrison, R. Sethi, Los Angeles, January 1977 (ACM, New York, 1977), pp. 238–252. https:// doi.org/10.1145/512950.512973

- 5. C. Ferdinand, Cache behaviour prediction for real-time systems. Ph.D. thesis, Saarland University, Saarbrücken (1997)

- C. Ferdinand, R. Heckmann, M. Langenbach, F. Martin, M. Schmidt, H. Theiling, S. Thesing, R. Wilhelm, Reliable and precise WCET determination for a real-life processor, in *International Workshop on Embedded Software*. Lecture Notes in Computer Science, vol. 2211 (2001), pp. 469–485

- C. Ferdinand, R. Wilhelm, On predicting data cache behavior for real-time systems, in *Proceedings of the Workshop on Languages, Compilers, and Tools for Embedded Systems* (*LCTES*), ed. by F. Mueller, A. Bestavros. Lecture Notes In Computer Science: Languages, Compilers, And Tools For Embedded Systems, vol. 1474 (Springer, Montréal, 1998), pp. 16– 30. https://doi.org/10.1007/BFb0057777

- C. Ferdinand, R. Wilhelm, Efficient and precise cache behavior prediction for real-time systems. Real-Time Syst. 17(2–3), 131–181 (1999)

- G. Gebhard, Static timing analysis tool validation in the presence of timing anomalies. Ph.D. thesis, Saarland University (2013). http://scidok.sulb.uni-saarland.de/volltexte/2013/5558/

- M. Lv, N. Guan, J. Reineke, R. Wilhelm, W. Yi, A survey on static cache analysis for realtime systems. Leibniz Trans. Embedded Syst. 3(1), 5:1–5:48 (2016). https://doi.org/10.4230/ LITES-v003-i001-a005

- 11. M. Pister, Timing model derivation—pipeline analyzer generation from hardware description languages. Ph.D. thesis, Saarland University (2012)

- 12. M. Schlickling, Timing model derivation—static analysis of hardware description languages. Ph.D. thesis, Saarland University (2013)

- 13. H. Theiling, Control flow graphs for real-time systems analysis. Ph.D. thesis, Universität des Saarlandes, Saarbrücken (2002)

- 14. S. Thesing, Safe and precise WCET determinations by abstract interpretation of pipeline models. Ph.D. thesis, Saarland University (2004)

- L. Thiele, R. Wilhelm, Design for timing predictability. Real-Time Syst. 28(2–3), 157–177 (2004). https://doi.org/10.1023/B:TIME.0000045316.66276.6e

- 16. R. Wilhelm, Mixed feelings about mixed criticality (invited paper), in *Proceedings of the* 18th International Workshop on Worst-Case Execution Time Analysis, WCET 2018, ed. by F. Brandner, July 3, 2018, Barcelona. OASICS, vol. 63 (Schloss Dagstuhl—Leibniz-Zentrum fuer Informatik, 2018), pp. 1:1–1:9. https://doi.org/10.4230/OASIcs.WCET.2018.1

- R. Wilhelm, S. Altmeyer, C. Burguière, D. Grund, J. Herter, J. Reineke, B. Wachter, S. Wilhelm, Static timing analysis for hard real-time systems, in *Proceedings of the 11th International Conference Verification, Model Checking, and Abstract Interpretation, VMCAI 2010*, ed. by G. Barthe, M.V. Hermenegildo, Madrid, January 17–19, 2010. Lecture Notes in Computer Science, vol. 5944 (Springer, Berlin, 2010), pp. 3–22. https://doi.org/10.1007/978-3-642-11319-2 3

- R. Wilhelm, D. Grund, J. Reineke, M. Schlickling, M. Pister, C. Ferdinand, Memory hierarchies, pipelines, and buses for future architectures in time-critical embedded systems. IEEE Trans. CAD Integr. Circuits Syst. 28(7), 966–978 (2009). https://doi.org/10.1109/TCAD. 2009.2013287

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

# Chapter 3 The Dynamic Random Access Memory Challenge in Embedded Computing Systems

Matthias Jung, Christian Weis, and Norbert Wehn

#### 3.1 Introduction

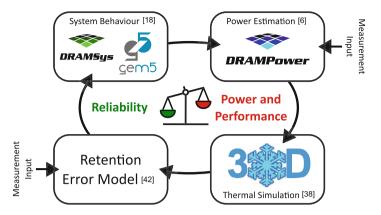

Dynamic random access memories (DRAMs) are key components in all computing systems that require large working memory. Due to the strong increase in data volume in many embedded applications, such as machine learning, image processing, autonomous systems, etc., DRAMs largely impact the overall system performance and power consumption. In many of these applications, the overall system performance is often limited by the memory bandwidth or latency and not by the computation itself. Due to the dynamic storage scheme of DRAMs and shrinking technology nodes, reliability is also a major concern in current and future DRAMs.

Therefore, new challenges arise, which we will discuss in this chapter. The most important metrics, which are typically considered for DRAM subsystems (especially in the *high-performance computing* (HPC) domain), are *bandwidth*, *latency*, and *capacity*. However, in the context of embedded systems it requires to consider further metrics, such as *power*, *temperature*, *reliability*, *safety*, and *security*. In the following we will highlight these challenges and refer to some of our recent contributions, which tackle these challenges.

M. Jung

Fraunhofer IESE, Kaiserslautern, Germany e-mail: Matthias.Jung@iese.fraunhofer.de

C. Weis · N. Wehn (⊠) TU Kaiserslautern, Kaiserslautern, Germany e-mail: weis@eit.uni-kl.de; wehn@eit.uni-klde

#### 3.2 Bandwidth and Latency

*Bandwidth* is the amount of data that can be transferred between DRAM and a computational unit within 1 s. The maximum DRAM bandwidth is limited to the number of data pins times the interface frequency. *Latency* is the access time that it takes to complete an access. In fact, latency helps bandwidth, but not vice versa [33]. For instance, lower DRAM latency results in more accesses per second, and therefore higher bandwidth, whereas increasing the number of data pins increases the bandwidth without decreasing latency. A fast execution of applications on embedded systems must not only be supported by the computational units, but the memory subsystem must be designed to avoid hitting the *memory wall* [43]. For example, embedded applications for autonomous driving will require between 400 and 1024 GB/s of memory bandwidth [16], which is hard to realize with the current DRAM technologies. To put the problem in perspective, we survey current memory architectures.

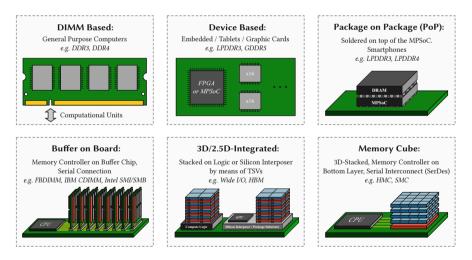

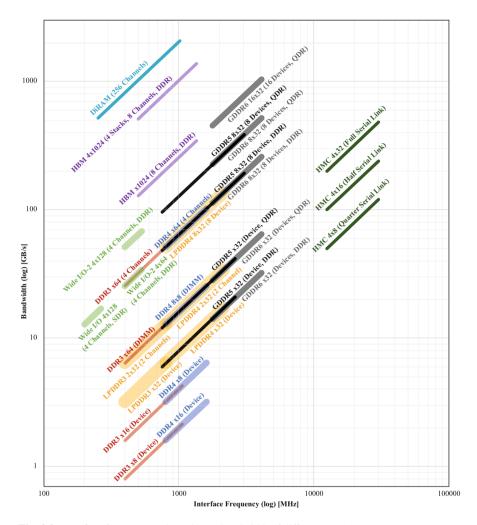

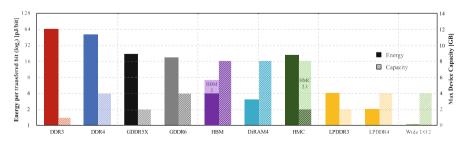

Figure 3.1 shows different DRAM-based memory subsystems, and Figs. 3.2 and 3.3 show their properties with respect to interface frequency, maximum theoretical bandwidth, and energy consumption per transferred bit.<sup>1</sup> The maximum bandwidth of conventional DIMM-based DDR solutions is limited by the I/O count and interface speed. This limitation arises due to the package, power considerations, and costs on both the memory and processing sides.

Fig. 3.1 DRAM-based memory subsystems

<sup>&</sup>lt;sup>1</sup>Note that the latency, actual sustainable bandwidth, and the total energy consumption of a DRAM strongly depend on the application being executed. Reaching the maximum theoretical bandwidths in Fig. 3.2 is practically impossible on general-purpose systems.

Fig. 3.2 Interface frequency and maximum bandwidth of different DRAM types

Fig. 3.3 Properties of today's DRAMs (Sources: Micron, Hynix, Nvidia, Xilinx, JEDEC)

To avoid pin limitations, designers and vendors are using *Buffer on Board* (BoB) organizations [7], in which an additional logic component is interposed between the CPU and DRAM to control the memory and to communicate with the CPU over a narrow, high-speed, serial interface. This technique is mainly used in server applications where several terabytes of DRAM are required. The required storage capacity in embedded systems is much smaller than in the high-performance systems BoB targets, and thus this organization is inappropriate. All the other following DRAM devices can achieve easily several GB capacity, which is enough for most of the embedded applications.

*Package on Package* (PoP) organizations reduce the distance between the DRAM and the MPSoC (from centimeters to millimeters), providing higher bandwidth, lower latency, better power efficiency, and smaller form factors, all of which are especially important for smartphones and tablets. Low power DDR DRAMs (e.g., LPDDR4) can be used either as a device on a PCB or mounted directly as PoP. The latter organization permits only one device to be connected, requiring DRAM commands to be serialized due to the resulting low pin count. For example, if eight LPDDR4 devices are used on a PCB, they deliver a theoretical bandwidth of 137 GB/s.

To address the huge memory demand of highly parallel GPUs, graphic DDR DRAMs (e.g., GDDR5X or GDDR6) use techniques like *quad data rate* (QDR) to deliver high bandwidth compared to conventional DDR DRAM. While LPDDR4 devices are designed and optimized for ultra-low power consumption with aggressive power gating and higher-threshold transistors, GDDR5X/6 devices focus on delivering the highest achievable bandwidth. Both use an architecture with distributed banks (heavy sub-banking) due to the wider data I/O widths of  $\times 16/\times 32$  and the larger data prefetch of up to 16 bit per data I/O. However, GDDR5X/6 devices improve the column-to-column cycle time ( $t_{CCD}$ ) by reducing data path delays from primary sense amplifiers to the global sense amplifiers. Furthermore, GDDR5X/6 chips use an on-die *phase lock loop* (PLL) to achieve very high I/O performance in QDR mode. In contrast, LPDDR4 devices in QDR mode yields a theoretical bandwidth of 1 TB/s, as shown in Fig. 3.2.

Another way of achieving high bandwidth is 3D stacking: examples include WIDE I/O, Micron's *Hybrid Memory Cube* (HMC), and Samsung's *High Bandwidth Memory* (HBM). These memories reduce the distance between CPU and external RAM from centimeters to micrometers by means of *through-silicon via* (TSV) technology. The available bandwidth increases due to more pins provided by the TSVs, but, more importantly, this technology provides a major boost in energy efficiency compared to standard off-chip (G)DDR devices.

The combination of high bandwidth communication and the lower power consumption of 3D integrated memory is an ideal fit for embedded systems. For example, four parallel HBM2 devices on a 2.5D silicon interposer can provide up to 1 TB/s [16]. However, 3D memories suffer from thermal issues, which we discuss in Sect. 3.4.

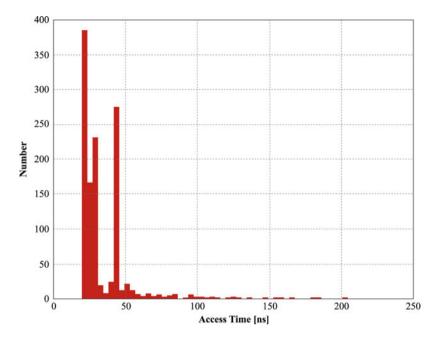

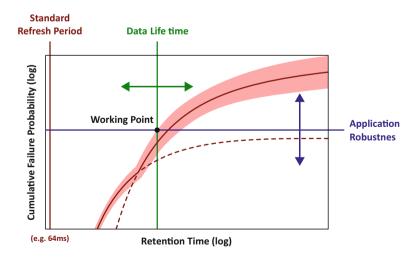

Fig. 3.4 Latency for an application running on DDR3 DRAM

From an application point of view, the DRAM subsystem has non-deterministic timing behavior [8] due to its complex protocol (i.e., the latency of a DRAM request depends on previous issued commands) and the runtime optimization of the memory controller; this makes it difficult to provide predictable performance and thus to guarantee real-time task predictability [1]. Figure 3.4 shows a histogram of the CHStone ADPCM benchmark [11] simulated on the DRAMSys framework [18].<sup>2</sup> Although the average latency is concentrated around 40 ns, the memory latency can easily vary by an order of magnitude.

As with the bandwidth issues discussed above, the memory controller plays an integral role in this non-deterministic timing behavior. The memory controller has to manage, on one side, accesses to the DRAM memory from the compute fabric and, on the other side, the complex interface protocol of the DRAMs. In the following we discuss the main contributions to the DRAM latency that origin from the complex internal memory architecture and the memory controller.

• **Row Misses:** The latency of a bank access varies depending on the state of its row buffer. If a memory access targets the same row as the row currently cached in the buffer (a row hit), it results in lower latency and lower energy memory

<sup>&</sup>lt;sup>2</sup>The simulated DRAM is a DDR3 with a RBC address mapping and disabled scheduler.

accesses. On the other hand, if a memory access targets a different row from that currently in the buffer (a row miss), it results in higher latency and energy consumption.

- Close vs. Open Page Policy: *Commercial off-the-shelf* (COTS) DRAM controllers usually support two major modes: an *open page policy* (OPP) and *closed page policy* (CPP). The OPP keeps the current row active after a read or write, whereas the CPP precharges the row automatically after each access. The latter makes the latency for each access more predictable, but it also decreases performance for access patterns with high row-hit potential.

- **Refresh:** DRAMs must be refreshed regularly due to their charge-based bit storage architecture. The memory controller has to issue this refresh operation periodically (e.g., every 64 ms). Normal accesses to the DRAM have to be blocked for the duration of the refresh operation  $t_{RFC}$  (350 ns for DDR4), degrading performance with respect to both bandwidth and latency and increasing energy consumption.<sup>3</sup> If a memory access arrives at the same time that a refresh happens it will experience unpredictable latency.

- Scheduling: COTS memory controllers are optimized for average case performance and therefore employ runtime scheduling of requests (c.f. Sect. 3.2) for online optimization. For example, with schedulers that attempt to maximize row hits it is possible that a request that misses the row could starve, which again results in a hardly predictable latency.

- Arbitration: A major challenge arises when several computational units are issuing read and write requests to the memory controller. The different applications running on these compute units will place their requests in different input buffers, and arbitration must be performed. This leads to interference that can cause high unpredictability.

- **Command/Address and Data bus Contention:** All banks in a DRAM share the same command/address and data buses, which can limit overall performance. If the data bus utilization is 100%, the maximum bandwidth is reached. On the other hand if the command bus utilization is 100%, WR and RD commands must be issued in later cycles that negatively impacts the bandwidth and the latency.

- Current Limiting and Power Supply Network: In order to limit peak currents there exists a rolling time-frame, in which a maximum of four banks can be activated, called *four activate window* ( $t_{FAW}$ ). There is also a minimum time interval between two ACT commands to different banks, ( $t_{RRD}$ ). Also these constraints can influence bandwidth, latency, and predictability in specific scenarios.

- **Further Effects:** Bank-Groups in DDR4 or GDDR or rank-to-rank switching constraints in DDR memories also impact the predictability.

$<sup>^{3}</sup>$ In fact, the degradation grows linearly with the capacity, which means it grows exponentially with each density generation. Liu et al. [27] and Bhati et al. [3] predicted that 40–50% of the power consumption of future DRAM devices will be caused by refresh commands, and the maximum DRAM bandwidth will be significantly reduced.

Due to this unpredictable timing behavior, processors for embedded applications with real-time and strict latency constraints have thus far largely avoided using DRAM. For example, Infineon's Aurix CPU, which is widely used for safety-critical applications, does not provide a DRAM controller.

In past years there were many investigations with respect to DRAM controllers for real-time and mixed-criticality applications in embedded systems. A detailed book which summarizes those approaches has been presented by Goossens et al. [8]. Most of these approaches concentrate operating the DRAM with statically precomputed command patterns which guarantee a predictable behavior. However, this predictability often comes with a degradation of sustainable bandwidth. Moreover, the bandwidth numbers presented in Fig. 3.2 are theoretical maxima: the sustainable memory bandwidth is much less, and it strongly depends on how the data is stored in the memories, i.e., the memory access pattern [12]. Therefore, it is not only important to choose a memory that provides high bandwidth, it is also important to design a DRAM controller that can bring the sustainable bandwidth closer to the theoretical maximum.

As already mentioned, general-purpose DRAM controllers use online scheduling techniques to improve the sustainable bandwidth, e.g., by reducing the number of row misses or read/write transitions. In order to reduce the number of read/write transitions, DRAM controllers buffer read and write commands in two distinct queues. An arbiter switches between read and write mode to diminish the  $t_{WTR}$  penalty, the minimum time interval between the end of a WR burst and a RD command.

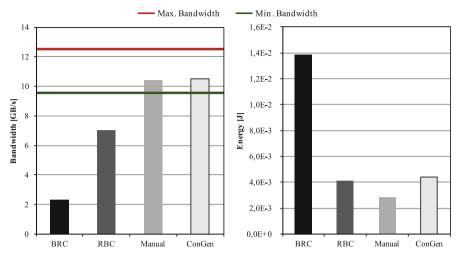

However, in embedded systems, many applications (e.g., signal, image, or neural network processing) have regular, fixed, and deterministic memory access patterns. On the compute side, inherent application-specific knowledge has been heavily exploited for efficient compute architectures. However, on the memory side there is limited research that exploits application knowledge to improve the memory access behavior. In [12] we presented an application-specific memory controller (ASMC). Key of this controller is an optimized mapping of the logical addresses to physical DRAM addresses such that the row misses in the access pattern stream are minimized. The corresponding mathematical optimization problem is an *integer* linear programming problem. The solution of this problem maximizes the number of row buffer hits and exploits the bank-level parallelism of the DRAM device in order to reduce the latency and therefore to keep up the sustainable bandwidth near to the maximum. Therefore, such an ASMC can outperform online schedulers because it was designed with a *global* application view. Furthermore, for real-time embedded systems with this method we can easily determine WCET bounds, since no non-deterministic online scheduling is involved.

The efficiency of this approach is demonstrated on an industrial embedded image processing application that consists of image rotation and FFT. Due to realtime requirements this application requires a minimum bandwidth of 9.57 GB/s. Figure 3.5 shows the bandwidth and energy for the standard address mappings of a standard memory controller with standard row-bank-column (RBC) mapping and bank-row-column (BRC) mapping, a manual optimization of the mapping of an

Fig. 3.5 Industrial image processing application

experienced engineer and the ASMC approach. The ASMC approach has a runtime of  $\sim$ 50 min, whereas the manual approach requires  $\sim$ 1 week for an engineer to fully understand the application and analyze the behavior. Furthermore, by using the generated address mapping, all the online scheduling capabilities of the memory controller could be removed, which reduced the required area of the memory controller by 35%.

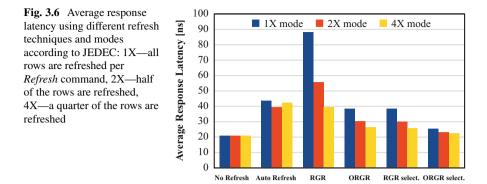

As mentioned already in Sect. 3.2 the refresh has a large impact on DRAM's bandwidth and latency. The overhead of refreshes can be reduced by only refreshing the memory cells inside the DRAM that hold data that are still alive. A large body of research exists developing schemes that manually refresh the DRAM row-by-row, characterizing each row's ability to retain data and eliminating unnecessary Refresh operations on rows that can be refreshed less often. These schemes have been shown to be extremely efficient. Since eliminating refresh improves both energy and performance of the memory system, these schemes offer the potential for significant gains in DRAM-system efficiency. However, these schemes are incompatible with the modern *auto-refresh* mechanism that is widely used: *auto-refresh* operates on multiple rows at once and not on a row-by-row basis. In addition, auto-refresh cannot skip any row, whether that row needs to be refreshed or not. Thus, the manual schemes use explicit row-level Activate (ACT) and Precharge (PRE) commands to refresh row-by-row, called row granular refresh (RGR). However, it was shown in [4] that techniques based on RGR could never be as effective as the DRAM's internal auto-refresh.

In [28] we presented a technique called optimized RGR which allows a rowby-row refresh with the same efficiency as the auto-refresh. Here, we investigated the timings that are relevant to *Activate* and *Precharge* commands and showed that these DRAM timing parameters can be reduced for performing the *Refresh*

operation row-by-row. We could demonstrate a reduction of latency and increase of bandwidth compared to standard *auto-refresh*, as shown in Fig. 3.6. The results can be even improved if only alive data is refreshed (ORGR select). Additionally, ORGR improved the energy efficiency compared to RGR.

It is becoming clear that embedded applications must concentrate on DRAM solutions like GDDR and HBM in combination with ASMCs and sophisticated refresh mechanisms in order to cope with their high bandwidth and low latency requirements.

#### **3.3** Power Consumption

Power is one of the major challenges in today's embedded system development. According to Fig. 3.3, the preliminary choice for low power designs is LPDDR4 and Wide I/O2 due to their very low energy consumption. However, when aiming at high memory bandwidth, e.g., 1 TB/s these devices are not optimal. For example, to achieve the aforementioned bandwidth with LPDDR4, 64 devices ( $\times$ 32) are required. Although the average power would be only  $\sim$ 17 W at a peak frequency of 2000 MHz, the high number of resulting I/O pins (2048) becomes unfeasible. Hence, the only alternative candidates for high bandwidth are HBM2 and GDDR5X/6. According to Figs. 3.2 and 3.3 the average power consumed<sup>4</sup> by the HBM (4 stack  $\times$ 1024) and GDDR6 (16 devices, QDR,  $\times$ 32) devices are  $\sim$ 60 W and  $\sim$ 150 W, respectively. These numbers show that DRAM will be a significant power contributor to embedded systems which require a high memory bandwidth. Therefore, it is mandatory to efficiently use DRAM's power-down modes in order to reduce power consumption.

In state-of-the-art memory controllers the entry to a power-down mode is scheduled when there was no activity in a period of time called timeout. DRAMs

<sup>&</sup>lt;sup>4</sup>Operated at respective peak frequency.

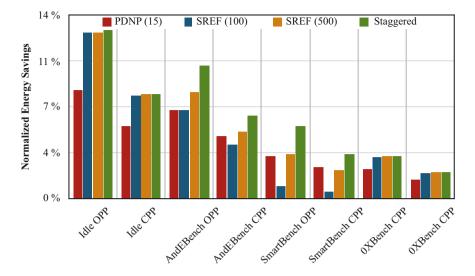

Fig. 3.7 Comparison of energy savings normalized to power-down disabled

offer three power-down modes, called *active power-down* (PDNA), *precharge power-down* (PDNP), and *self-refresh* (SREF). In [35] we showed that a highly opportunistic SREF entry results in an increased power consumption, since the SREF will always execute an internal refresh in the beginning. Therefore, the timeout for a SREF entry should be at least 500 clock cycles for a Wide I/O DRAM.

In [19] we presented an optimized power-down policy, called *staggered power-down*, which considers all three available DRAM power-down modes to achieve the maximum saving in energy and the minimum in slow-down on the execution of the applications. The basic idea is to change to the next more efficient power-down state on a refresh event. With this method, unnecessary SREF entries will be avoided and the hardware timeout counters, as used in state-of-the-art controllers, are not required anymore. As shown in Fig. 3.7 for Wide I/O DRAMs an energy reduction up to 10% in high activity periods and up to 13% in idle phases is feasible.

A high power consumption also fosters a high thermal dissipation that largely impacts the reliability of a DRAM. This challenge is discussed in more detail in the next paragraph.

#### **3.4** Temperature vs. Reliability

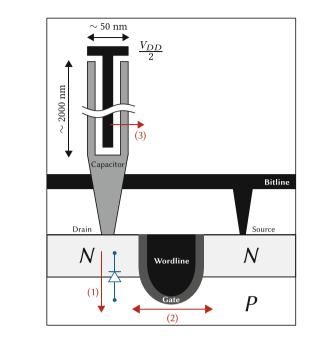

DRAMs are very sensitive to high temperature, which increases the leakage in the memory cells. Figure 3.8 shows the different leakage paths in a DRAM cell:

**Fig. 3.8** Leakage paths in modern buried wordline DRAM architecture [23, 34]

- **Drain Leakage** (1), which includes the P-N junction leakage as well as *gate induced drain leakage* (GIDL). GIDL is mainly caused by *trap assisted tunneling* (TAT), and it is influenced by the number and distribution of traps in the band-gap region as well as the electric field. Since the negative wordline voltage and the positive charge stored in the cell capacitor (when a 1 is stored in the cell) increase the electric field in the band-gap region (gate-drain overlap region), GIDL is the major source of leakage for a stored 1 in the DRAM cell [31].

- Sub-threshold Leakage (2), which is the drain-source leakage of the cell transistor when it is in the OFF state. This current depends on various factors such as negative wordline voltage, bulk voltage, etc. When the bitlines are in precharged state  $(V_{DD}/2)$  this can slightly charge the cell capacitor and therefore cause the degradation of a 0 stored in the cell. It can also degrade a 1 stored in the cell by discharging to the bitline, but the leakage will be very small due to the increased threshold voltage of the access transistor when a 1 is stored (body-bias effect).

- Cell Capacitor Leakage (3), which is the leakage through the cell capacitor dielectric. With the technology scaling, also the capacitor area is decreasing. Therefore, to maintain the cell capacitance at the previous value, dielectric thickness has to be reduced, which increases the leakage. The use of new *metal insulator metal* (MIM) structure with high-k dielectric materials has helped to reduce this leakage. Capacitor leakage influences both stored 0's and stored 1's.

In order to avoid data corruption by retention errors due to leakage, the refresh frequency needs to be increased. The general rule of thumb is to double the refresh

rate for every 10 °C increase over 85 °C [20]. For example, the refresh period must be decreased from 64 ms to 4–8 ms for 125 °C, which leads to a serious collapse of the sustainable bandwidth [16].

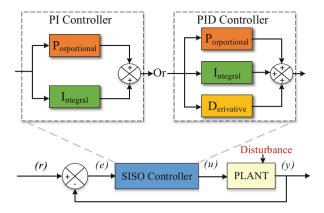

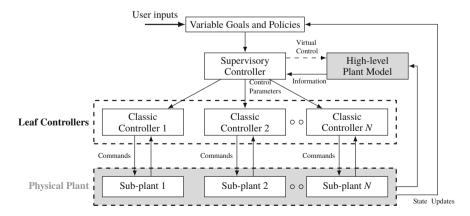

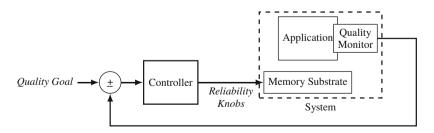

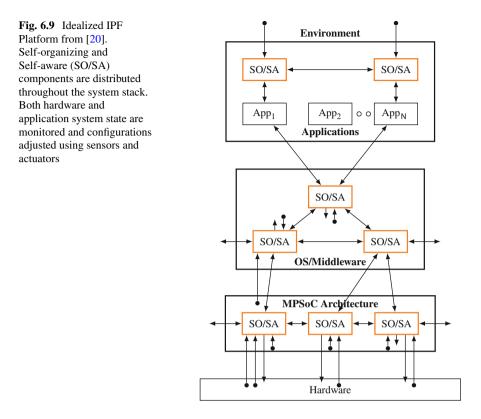

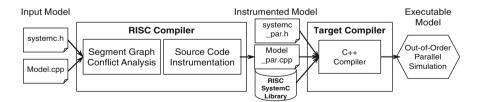

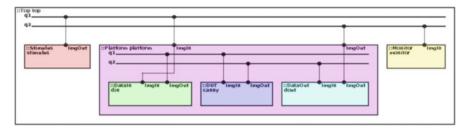

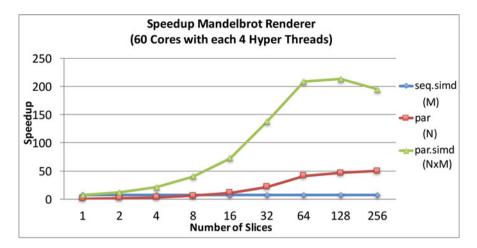

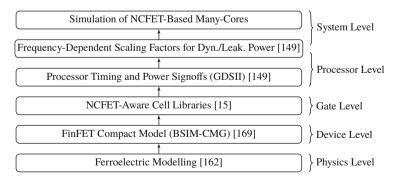

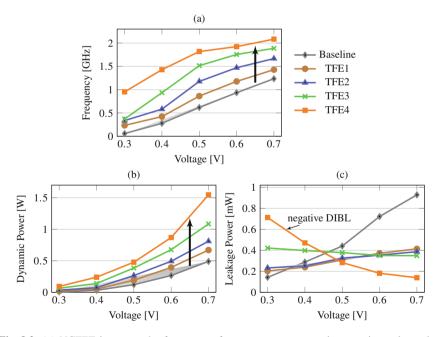

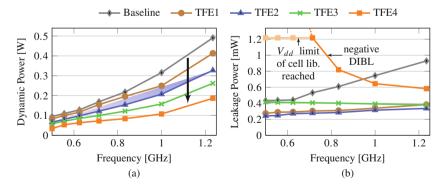

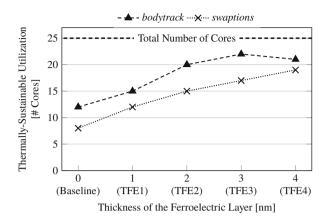

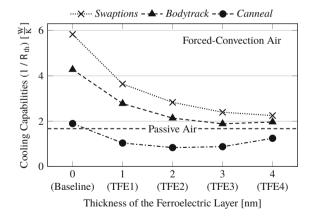

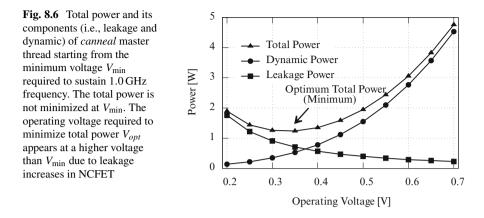

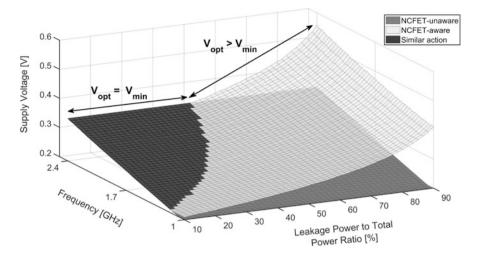

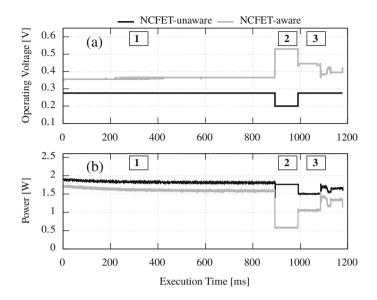

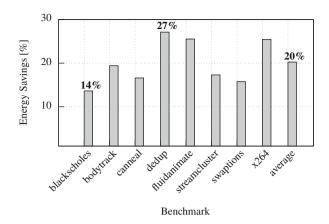

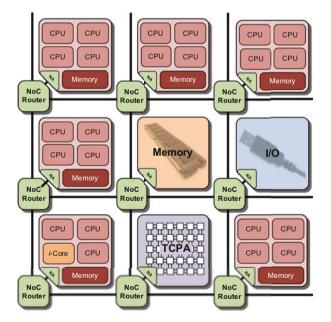

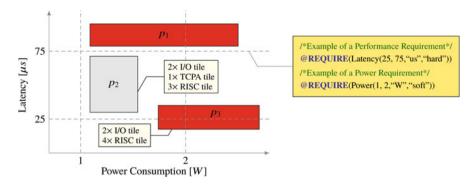

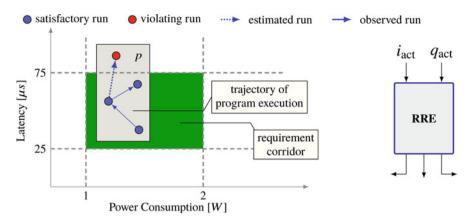

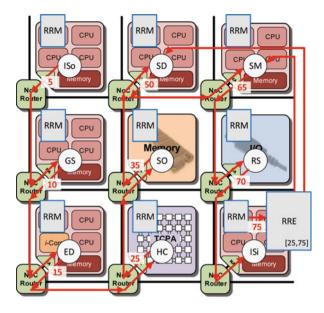

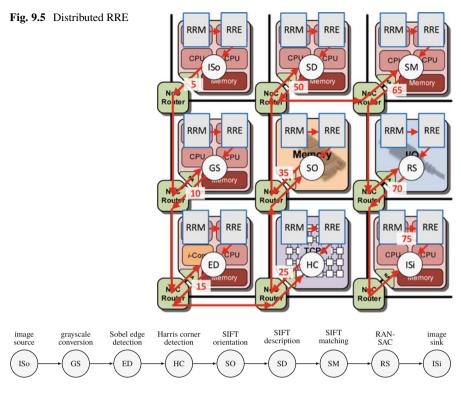

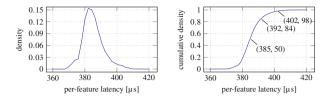

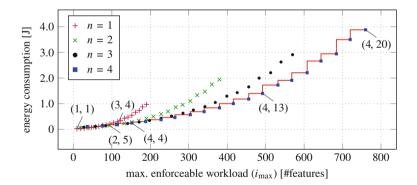

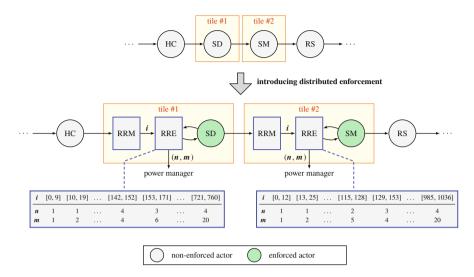

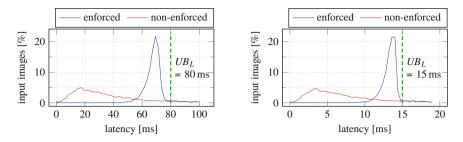

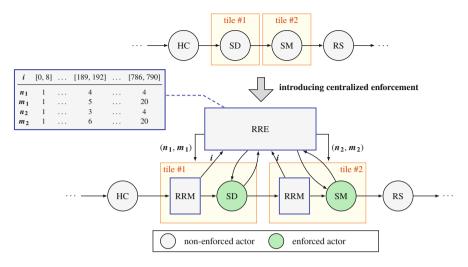

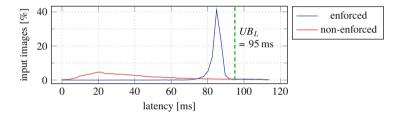

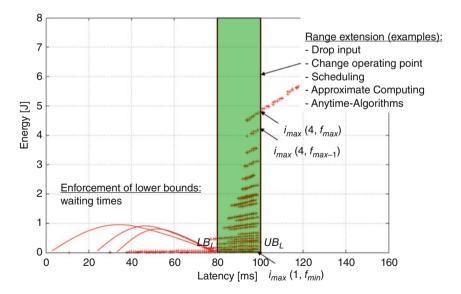

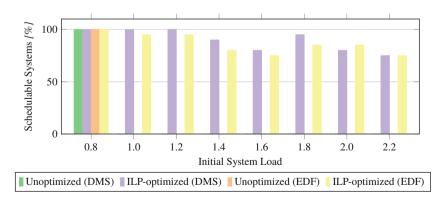

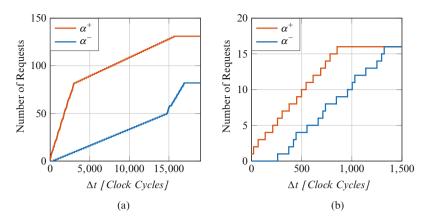

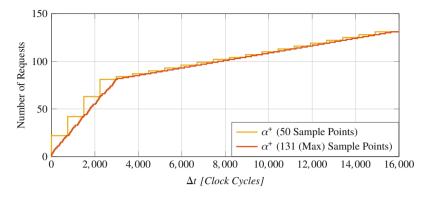

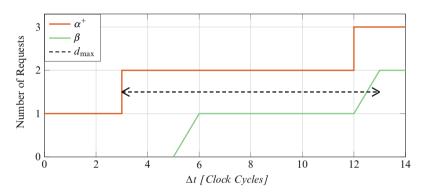

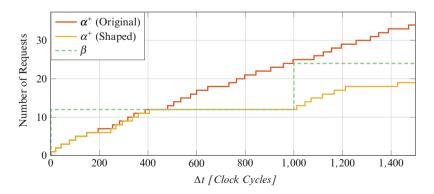

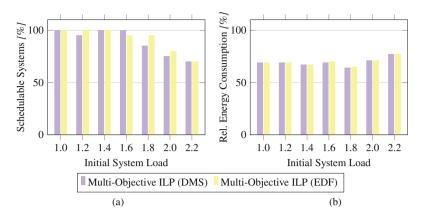

This situation is even worse for today's 3D stacked DRAM systems (e.g., Wide I/O, HBM, HMC, etc.), which aggravate the thermal crisis: i.e., these DRAMs are even more sensitive to temperature changes because of the stacked thin dies. Additionally, when aiming for highest bandwidths with HBM or HMC, these devices will consume, as mentioned before, a significant amount of power on a small area compared to their commodity counterparts. Thus, the self-heating of 3D-DRAMs is even more accelerated. Besides the leakage currents, crosstalk on bitlines and wordlines can also disturb the data stored in the cells or disturb their sensing. Due to the aforementioned effects and shrinking technology nodes, reliability is a major concern in DRAMs. Many techniques exist to improve the reliability, e.g., using *error correcting codes* (ECC) and/or spatial redundancy.