Alexander Nadel / Kristin Yvonne Rozier (Eds.)

# PROCEEDINGS OF THE 23RD CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2023

Alexander Nadel / Kristin Yvonne Rozier (Eds.)

PROCEEDINGS OF THE 23RD CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2023

# Conference Series: Formal Methods in Computer-Aided Design Volume 4

Conference Series: Formal Methods in Computer-Aided Design

Series edited by: Warren A. Hunt, Jr., The University of Texas at Austin Austin, TX 78705 | hunt@cs.utexas.edu Georg Weissenbacher, TU Wien

Karlsplatz 13, 1040 Vienna, Austria | georg.weissenbacher@tuwien.ac.at

The Conference on Formal Methods in Computer-Aided Design (FMCAD) is an annual conference on the theory and applications of formal methods in hardware and system verification. FMCAD provides a leading forum to researchers in academia and industry for presenting and discussing groundbreaking methods, technologies, theoretical results, and tools for reasoning formally about computing systems. FMCAD covers formal aspects of computer-aided system design including verification, synthesis, and testing.

Information on this publication series and the volumes published therein is available at www.tuwien.ac.at/academicpress.

Volume 4 edited by:

Alexander Nadel, Intel and Technion - Israel Institute of Technology

Technion City, Haifa, Israel | alexander.nadel@cs.tau.ac.il

Kristin Yvonne Rozier, Iowa State University of Science and Technology

Ames, Iowa, USA | kyrozier@iastate.edu

# PROCEEDINGS OF THE 23RD CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2023

Cite as:

Nadel, A. & Rozier, K. Y. (Eds.). (2023). Proceedings of the 23rd Conference on Formal Methods in Computer-Aided Design – FMCAD 2023. TU Wien Academic Press. https://doi.org/10.34727/2023/isbn.978-3-85448-060-0

### TU Wien Academic Press, 2023

c/o TU Wien Bibliothek TU Wien Resselgasse 4, 1040 Wien academicpress@tuwien.ac.at www.tuwien.at/academicpress

This work is licensed under a Creative Commons attribution 4.0 international license (CC BY 4.0). https://creativecommons.org/licenses/by/4.0/

ISBN (online): 978-3-85448-060-0 ISSN (online): 2708-7824

Available online: https://doi.org/10.34727/2023/isbn.978-3-85448-060-0

Media proprietor: TU Wien, Karlsplatz 13, 1040 Wien Publisher: TU Wien Academic Press Publication series editor: Warren A. Hunt, Jr. and Georg Weissenbacher Editors (responsible for the content): Alexander Nadel and Kristin Yvonne Rozier

## **Preface**

These are the proceedings of the twenty-third International Conference on Formal Methods in Computer-Aided Design (FMCAD), which was held in Ames, Iowa, USA from October 24 – October 27, 2023. FMCAD was first held in 1996, and was a bi-annual conference until 2006, when the FMCAD and CHARME conferences merged into a single FMCAD conference, and since then has been held annually. FMCAD 2023 is the twenty-third edition in the series, covering formal aspects of computer-aided system design including verification, specification, synthesis, and testing. It provides a leading forum to researchers in academia and industry to present and discuss groundbreaking methods, technologies, theoretical results, and tools for reasoning formally about computing systems.

The program of FMCAD 2023 consists of four tutorials, three invited talks, a student forum, and the main program consisting of presentations of 31 accepted peer-reviewed papers.

The tutorial day featured four presentations:

- Developing an Open-Source, State-of-the-Art Symbolic Model-Checking Framework for the Model-Checking Research Community by The NSF:CCRI Project Investigators (Kristin Y. Rozier, Natarajan Shankar, Cesare Tinelli, Moshe Vardi)

- MiniZinc for Formal Methods by Peter J. Stuckey

- Local Search and Its Application in CDCL/CDCL(T) solvers for SAT/SMT by Shaowei Cai

- NASA's core Flight System Framework Overview/Tutorial by David Swartwout

and the main conference featured three invited talks:

- Reasoning about quantifiers in SMT: the QSMA algorithm by Maria Paola Bonacina

- Distribution Testing: The New Frontier for Formal Methods by Kuldeep Meel

- Formal Methods for Trusted AI by Bettina Könighofer

FMCAD 2023 received 73 submissions out of which the committee decided to accept 31 for publication. Each submission received at least four reviews, except for two submissions which received three reviews. The topics of the accepted papers include machine learning, model checking, hardware validation, SAT & SMT solving, avionics, security, synthesis and others. Among the accepted papers, there are 23 regular papers (20 long and 3 short) and 8 tool/case study papers (all long).

FMCAD 2023 hosted the eleventh edition of the Student Forum, which has been held annually since 2013 and provides a platform for graduate students at any career stage to introduce their research to the FMCAD community. The FMCAD Student Forum 2023 was organized by Mikoláš Janota and Nina Narodytska and featured short presentations of 16 accepted contributions. The proceedings provide a detailed description of the Student Forum and lists all accepted contributions.

Organizing this event was made possible by the support of a large number of people and our sponsors. The program committee members and additional reviewers, listed on the following pages, did an excellent job providing detailed and insightful reviews. The reviews helped us build a strong program and helped the authors improve their submissions. We thank each and everyone of them for dedicating their time and providing their expertise. We thank our web master Yogev Shalmon, our sponsorship chair Yoni Zohar and the Student Forum organizers Mikoláš Janota and Nina Narodytska. We thank Georg Weissenbacher both for his exceptional assistance in organizing the event, communicating to us the decisions of the steering committee, as well as being the publication chair.

Holding a conference like FMCAD would not be feasible without the financial support of our sponsors. We would like to express our gratitude to our sponsors (in alphabetical order): AWS, Cadence, Futurewei, GE Aerospace, Siemens, Synopsys and Toyota.

The conference proceedings are available as Open Access Proceedings published by TU Wien Academic Press, and through the IEEE Xplore Digital Library. Last but not least, we thank all authors who submitted their papers to FMCAD 2023 (accepted or not), and whose contributions and presentations form the core of the conference.

We are grateful to everyone who presented their paper, gave a keynote or gave a tutorial. We thank all attendees of FMCAD for supporting the conference and making FMCAD an engaging and enjoyable event.

October 2023

Kristin Y. Rozier Iowa State University, IA, USA Alexander Nadel Intel Corporation and Technion, Israel

## Organizing Committee

## **Program Co-Chairs**

Kristin Y. Rozier Iowa State University, IA, USA

Alexander Nadel Intel Corporation and Technion, Israel

**Student Forum Chairs**

Mikoláš Janota Czech Technical University, Czechia

Nina Narodytska VMware Research, CA, USA

Sponsorship Chair

Yoni Zohar Bar Ilan University, Israel

Web Chair

Yogev Shalmon Intel Corporation and Open University, Israel

**Publication Chair**

Georg Weissenbacher TU Wien, Austria

**FMCAD Steering Committee**

Clark Barrett Stanford University, CA, USA

Armin Biere University of Freiburg, Germany

Ruzica Piskac Yale University, CT, USA Anna Slobodova Intel Corporation, TX, USA

Georg Weissenbacher TU Wien, Austria

## **Program Committees**

## FMCAD 2023 Program Committee

Alessandro Abate Oxford

Guy Amir Hebrew University

Clark Barrett Stanford University

Per Bjesse Synopsys Inc.

Roderick Bloem Graz University of Technology

Ivana Cerna Masaryk University

Supratik Chakraborty IIT Bombay

Sylvain Conchon Universite Paris-Sud

Rayna Dimitrova CISPA Helmholtz Center for Information Security

Rohit Dureja IBM

Grigory Fedyukovich Florida State University

Mathias Fleury University of Freiburg

Amit Goel Amazon

Alberto Griggio Fondazione Bruno Kessler

Arie Gurfinkel University of Waterloo

Liana Hadarean Amazon Web Services

Ziyad Hanna Cadence Design Systems

William Harrison Two Six Technologies

Bo-Yuan Huang Intel

Alan Jović University of Zagreb

Daniela Kaufmann TU Wien Tim King Google

Stepan Kochemazov ISDCT SB RAS, ITMO University

Rebekah Leslie-Hurd Rain

Andreas Lööw Imperial College London Kuldeep Meel University of Toronto

Baoluo Meng GE Research

Naoko Okubo Japan Aerospace Exploration Agency (JAXA)

Andrew Reynolds University of Iowa

Philipp Ruemmer University of Regensburg Cristoph Scholl University of Freiburg Roberto Sebastiani University of Trento

Shaowei Cai Chinese Academy of Sciences

Natasha Sharygina Università della Svizzera Italiana (USI Lugano)

Christoph Sticksel The Mathworks

Christoph Torens DLR (German Aerospace Center)

Nestan Tsikaridze Stanford University

Yakir Vizel Technion Georg Weissenbacher TU Wien

Michael Whalen Amazon Web Services, Inc.

Shufang Zhu Oxford

## FMCAD 2023 Student Forum Committee

Haniel Barbosa Universidade Federal de Minas Gerais

Jaroslav Bendik Certora

Armin Biere University of Freiburg

Martin Blicha University of Lugano

Nikolaj Bjørner Microsoft Research

Martin Nyx Brain University of London

Isabel Garcia Contreras University of Waterloo

Rayna Dimitrova CISPA Helmholtz Center for Information Security

Katalin Fazekas TU Wien

Mathias Fleury University of Freiburg Arie Gurfinkel University of Waterloo

Antti Hyvärinen Università della Svizzera Italiana (USI Lugano)

Martin Jonáš Fondazione Bruno Kessler

Daniela Kaufmann TU Wien

Konstantin Korovin The University of Manchester

Giles Reger AWS and The University of Manchester

Andrew Reynolds University of Iowa

Corina Pasareanu NASA and Carnegie Mellon University

Mathias Preiner Stanford

Karem Sakallah University of Michigan

Mark Santolucito Barnard College

Carsten Sinz Karlsruhe Institute of Technology

Nestan Tsiskaridze Stanford University

Tom van Dijk University of Twente

Florian Zuleger TU Wien

## Additional Reviewers

Ahlbrecht, Alexander Athavale, Anagha

Bayless, Samuel Blicha, Martin Blumensath, Achim Bombardelli, Alberto Britikov, Konstantin

Ernst, Gidon Esen, Zafer

Fraer, Ranan

Gacek, Andrew Gajavelly, Raj Kumar

Hader, Thomas Hamza, Ameer Hjort, Håkan

Isac, Omri

Justino, Daniel Jünger, Franz

Kiesl-Reiter, Benjamin Kobayashi, Tsutomu

Le, Nham Leslie-Hurd, Joe Liang, Chencheng Lukina, Anna Lundgren, Lars

Mann, Makai Masina, Gabriele Meggendorfer, Tobias Micheli, Andrea Möhle, Sibylle Morettin, Paolo

Neider, Daniel Noetzli, Andres Oertel, Andy Otoni, Rodrigo

Paul, Saswata Prabhu, Sumanth Preiner, Mathias Priya, Siddharth

Rappoport, Omer Rath, Jakob Redondi, Gianluca Riley, Daniel Roveri, Marco

S, Akshay Schirmer, Sebastian Sharma, Vaibhav Singhania, Nimit Somech, Nir Spallitta, Giuseppe Temel, Mertcan Tiemeyer, Andreas

Ueda, Yasushi

Varanasi, Sarat Chandra

Westphal, Bernd Wilson, Amalee Wolfovitz, Guy Wu, Haoze

Zelazny, Tom Zavalia, Lucas Zohar, Yoni

# Table of Contents

| Invited Talks                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------|----|

| Reasoning about Quantifiers in SMT: The QSMA Algorithm                                                                  | 1  |

| Distribution Testing: The New Frontier for Formal Methods                                                               | 2  |

| Formal Methods for Trusted AI                                                                                           | 3  |

| Tutorials                                                                                                               |    |

| Developing an Open-Source, State-of-the-Art Symbolic Model-Checking Framework for the Model-Checking Research Community | 4  |

| MiniZinc for Formal Methods                                                                                             | 5  |

| Local Search and Its Application in CDCL/CDCL(T) solvers for SAT/SMT                                                    | 6  |

| NASA's core Flight System Framework Overview                                                                            | 7  |

| Student Forum                                                                                                           |    |

| The FMCAD 2022 Student Forum                                                                                            | 8  |

| Neural Networks and Machine Learning                                                                                    |    |

| Formally Explaining Neural Networks within Reactive Systems                                                             | 10 |

| Lightweight Online Learning for Sets of Related Problems in Automated Reasoning                                         | 23 |

| DelBugV: Delta-Debugging Neural Network Verifiers                                                                       | 34 |

| Model Checking                                                                                                          |    |

| Towards Compositional Hardware Model Checking Certification                                                             | 44 |

| Btor2MLIR: A Format and Toolchain for Hardware Verification                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data-Driven Learning of Strong Conjunctive Invariants                                                                                                                                   |

| Automating Cutoff-based Verification of Distributed Protocols                                                                                                                           |

| Optimal Bounded Partial Order Reduction                                                                                                                                                 |

| Hardware                                                                                                                                                                                |

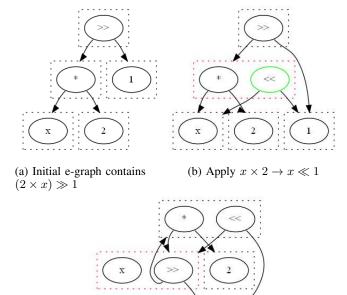

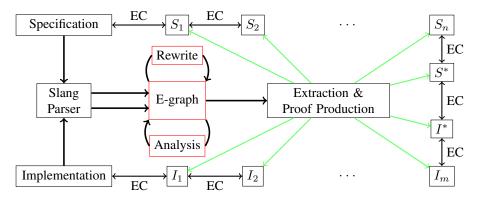

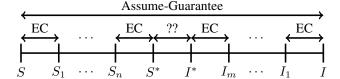

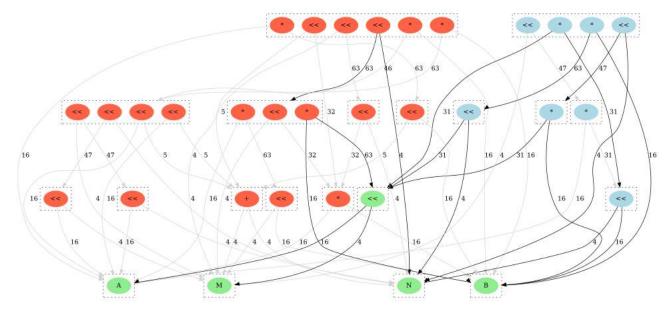

| Datapath Verification via Word-Level E-Graph Rewriting                                                                                                                                  |

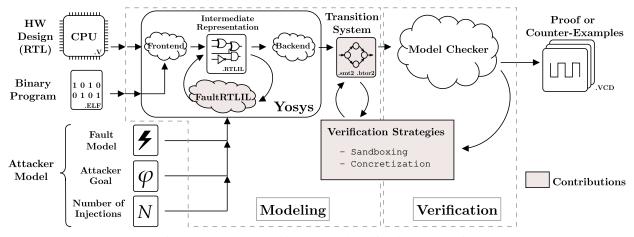

| $\mu$ ArchiFI: Formal Modeling and Verification Strategies for Microarchitetural Fault Injections 101 Simon Tollec, Mihail Asavoae, Damien Couroussé, Karine Heydemann, and Mathieu Jan |

| Sylvia: Countering the Path Explosion Problem in the Symbolic Execution of Hardware Designs 110 Kaki Ryan and Cynthia Sturton                                                           |

| Binary decision diagrams on modern hardware                                                                                                                                             |

| SAT                                                                                                                                                                                     |

| Proofs for Incremental SAT with Inprocessing                                                                                                                                            |

| Verified Encodings for SAT Solvers                                                                                                                                                      |

| SAT-Based Quantified Symmetric Minimization of the Reachable States of Distributed Protocols 152 <i>Katalin Fazekas, Aman Goel, and Karem A. Sakallah</i>                               |

| BIG Backbones                                                                                                                                                                           |

| SMT                                                                                                                                                                                     |

| Local Search For SMT On Linear and Multilinear Real Arithmetic                                                                                                                          |

| Mariposa: Measuring SMT Instability in Automated Program Verification                                                                                                                   |

| A Procedure for SyGuS Solution Fitting via Matching and Rewrite Rule Discovery                                                                                                          |

| Partitioning Strategies for Distributed SMT Solving                                                                                                                                     |

## Avionics

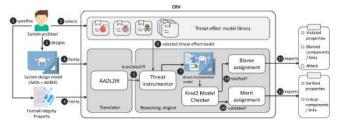

| CRV: An Automated Resiliency Reasoner for System Design Models                                       | 209 |

|------------------------------------------------------------------------------------------------------|-----|

| Towards a Correct-by-Construction Design of Integrated Modular Avionics                              | 221 |

| Fortis: A Tool for Analysis and Repair of Robust Software Systems                                    | 228 |

| A provably correct floating-point implementation of Well Clear Avionics Concepts                     | 237 |

| Security and Synthesis                                                                               |     |

| Formal Verification of Correctness and Information Flow Security for an In-Order Pipelined Processor | 247 |

| Modular System Synthesis                                                                             | 257 |

| Modelling and Verification of Security-Oriented Resource Partitioning Schemes                        | 268 |

| Cyber-Physical Systems                                                                               |     |

| Lift-off: Trustworthy ARMv8 semantics from formal specifications                                     | 274 |

| Cycle and Commute: Rare-Event Probability Verification for Chemical Reaction Networks                | 284 |

| Conformance Testing for Stochastic Cyber-Physical Systems                                            | 294 |

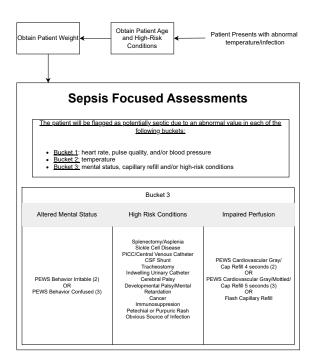

| MediK: Towards Safe Guideline-based Clinical Decision Support                                        | 306 |

# Reasoning about Quantifiers in SMT: The QSMA algorithm

Maria Paola Bonacina Università degli Studi di Verona Verona, Italy mariapaola.bonacina@univr.it

Abstract—Automated reasoning is a key enabling technology for formal methods. Automated theorem provers (ATP) for firstorder and lately higher-order logic and solvers for satisfiability modulo theories (SMT) showcase impressive power and amazing sophistication. However, ATP systems reason well about formulas with arbitrary quantification and free symbols, while SMT solvers reason well about ground formulas with defined symbols. Since formulas from applications involve both quantifiers and defined symbols, a hiatus remains open. QSMA is a new algorithm for quantifiers in SMT [4]. QSMA stands for Quantified Satisfiability Modulo theory and Assignment. Currently, QSMA works for one theory with a unique intended model, so that models differ only in the assignment of values to variables. QSMA accepts arbitrary formulas, viewing all quantifiers as existential by double negation. Since QSMA operates a recursive descent over the tree structure of the formula, peeling off quantifiers and instantiating variables, each call works modulo an assignment. By building under- and over- approximations of the formula, QSMA zooms in on a model or finds that none exists. The implementation of OSMA in the YicesOS solver [6] built on top of the Yices 2 solver [5] exhibited excellent performances in linear rational arithmetic and nonlinear arithmetic [4]. Integrating QSMA in the CDSAT framework for conflict-driven satisfiability in a union of theories [1]-[3] is the next challenge.

#### REFERENCES

- [1] Maria Paola Bonacina, Stéphane Graham-Lengrand, and Natarajan Shankar. Conflict-driven satisfiability for theory combination: transition system and completeness. J. Autom. Reason., 64(3):579-609, March 2020.

- [2] Maria Paola Bonacina, Stéphane Graham-Lengrand, and Natarajan Shankar. CDSAT for nondisjoint theories with shared predicates; arrays with abstract length. In Antti Hyvärinen and David Déharbe, editors, Proc. SMT-20, volume 3185 of CEUR Proceedings, pages 18-37. CEUR WS-org, August 2022.

- [3] Maria Paola Bonacina, Stéphane Graham-Lengrand, and Natarajan Shankar. Conflict-driven satisfiability for theory combination: lemmas, modules, and proofs. J. Autom. Reason., 66(1):43-91, February 2022.

- [4] Maria Paola Bonacina, Stéphane Graham-Lengrand, and Christophe Vauthier. QSMA: a new algorithm for quantified satisfiability modulo theory and assignment. In Brigitte Pientka and Cesare Tinelli, editors, Proceedings of the 29th International Conference on Automated Deduction (CADE), volume 14132 of Lecture Notes in Artificial Intelligence, pages 78-95. Springer, 2023.

- [5] Bruno Dutertre. Yices 2.2. In Armin Biere and Roderick Bloem, editors, Proceedings of the 26th International Conference on Computer Aided Verification (CAV), volume 8559 of Lecture Notes in Computer Science, pages 737-744. Springer, 2014.

- [6] Stéphane Graham-Lengrand. The yicesQS solver web page. https://github.com/disteph/yicesQS, 2023. Last seen on September 14, 2023.

# Distribution Testing: The New Frontier for Formal Methods

Kuldeep Meel University of Toronto Toronto, Canada meel@cs.toronto.edu

Abstract—The dominant guiding philosophy in the first sixty years of Computer Science was for designers to design systems that were always correct, and to accept nothing less as users. But times have changed: Users and designers are accustomed to systems with statistical components and behaviors. What does it mean for the formal methods community?

In this talk, we argue that such a dramatic change in the acceptance and design of systems presents exciting opportunities to make fundamental contributions: we need to rethink the notions and techniques for the design of specifications and verification methodologies. In particular, we will focus on the systems whose behaviors are not naturally captured by symbolic relations but rather require reliance on probability distributions. We will discuss our recent efforts in designing formal methodologies for testing whether a sampling subroutine generates a desired distribution. We will showcase the challenges, opportunities, and rewards in our journey.

## Formal Methods for Trused AI

Bettina Könighofer Graz University of Technology Graz, Austria bettina.koenighofer@tugraz.at

Abstract—The enormous influence of systems deploying AI is contrasted by the growing concerns about their safety and the relative lack of trust by the society. This talk will focus on a few aspects of trustworthy AI: safety, accountability, and explainability. First, we will discuss recent work on evaluating safety for systems deploying deep learning, and correct-by-construction runtime assurance methods to enforce safety during runtime (aka shielding). For accountability, we outline the potential of formal computing tools to analyse the decisions of autonomous agents and to assign responsibility. Finally, we approach explainability from the automata learning perspective. We will discuss recent automata learning approaches which are able to learn compact probabilistic models for high-dimensional environments and outline how learned environmental models can effectively be used to understand and to evaluate the decisions of the agent.

# Developing an Open-Source, State-of-the-Art Symbolic Model-Checking Framework for the Model-Checking Research Community

Kristin Y. Rozier Iowa State University Ames, IA, USA kyrozier@iastate.edu

Natarajan Shankar SRI Menlo Park, CA, USA shankar@csl.sri.com

Cesare Tinelli University of Iowa Iowa City, IA, USA cesare-tinelli@uiowa.edu

Moshe Vardi Rice University Houston, TX, USA vardi@cs.rice.edu

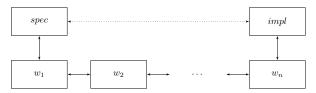

Abstract—As model checking becomes more integrated into the standard design and verification process for safety-critical systems, the platforms for model checking research have become more limited. Previous options have become closed-source or industry tools; current research platforms don't have support for expressive specification languages needed for verifying real systems. Our goal is to fill the current gap in model checking research platforms: building a freely-available, open-source, scalable model checking infrastructure that accepts expressive models and efficiently interfaces with the currently-maintained state-of-the-art back-end algorithms to provide an extensible research and verification tool. With extensive involvement from the research community, we have been creating a community resource with a well-documented intermediate representation to enable extensibility, and a web portal, facilitating new modeling languages and back-end algorithmic advances. To add new modeling languages or algorithms, researchers need only to develop a translator to/from the new intermediate language, and will then be able to integrate each advance with the full state-of-the-art in model checking. This tutorial will include an overview of the model checking intermediate language semantics and demonstrations of (provably correct) translators to and from that representation.

## MiniZinc for Formal Methods

Peter J. Stuckey Monash University Melbourne, Australia Peter.Stuckey@monash.edu

Abstract-MiniZinc is a free and open-source constraint modeling language, designed for solving discrete optimisation problems. You can use MiniZinc to model constraint satisfaction and optimization problems in a high-level, solver-independent way, taking advantage of a large library of pre-defined constraints encapsulting different combinatorial substructures of the problem. Your model is then compiled into FlatZinc, a solver input language that is understood by a wide range of solvers including leading CP solvers such as OR-tools from Google, and CP-optimiser from IBM, and leading MIP solvers such as Gurobi and Cplex. MiniZinc is useful for Formal Reasoning problems where we reason about a bounded size problem on discrete objects (including integers). In this tutorial we will give an introduction to MiniZinc focusing, at least in the latter part, on where it can be applied

to Formal Methods problems. Formal methods modelling through MiniZinc leads to different ways to model things such as state progression, and can take advantage of combinatorial substructures that occur in such problems, such as injective mappings. Overall MiniZinc gives an alternate, and often highly competitive, approach to using SMT for answering some kinds of formal reasoning

questions.

# Local Search and Its Application in CDCL/CDCL(T) solvers for SAT/SMT

Shaowei Cai Chinese Academy of Sciences Beijing, China caisw@ios.ac.cn

Abstract—Modern SAT solvers are based on a paradigm named conflict driven clause learning (CDCL), and CDCL(T) remains the main method for SMT. Local search is an important alternative for satisfiable instances, which has witnessed significant progress in SAT, and has begun to show promising results in SMT. Furthermore, recent techniques integrating local search into CDCL have brought significant improvements, and local search is widely used in state of the art CDCL solvers as an important component. Similar results have also been observed in CDCL(T). This talk will introduce state of the art local search methods for SAT and SMT, and also present the recent techniques of combining local search and CDCL/CDCL(T).

## NASA's core Flight System Framework Overview

David Swartwout NASA Houston, TX, USA dave.c.swartwout@nasa.gov

Abstract—The core Flight System (cFS) is a platform and project independent reusable software framework and set of reusable software applications. There are three key aspects to the cFS architecture: a dynamic run-time environment, layered software, and a component-based design. It is the combination of these key aspects that makes it suitable for reuse on any number of flight projects and/or embedded software systems at a significant cost and schedule savings. This tutorial will give a brief overview of the architecture and demonstrate a simple app development and deployment.

## The FMCAD 2023 Student Forum

Mikolas Janota (1) Czech Technical University Prague, Czechia mikolas.janota@gmail.com

Nina Narodytska 🕞 VMware Research Palo Alto, USA n.narodytska@gmail.com

Abstract-The Student Forum at the International Conference on Formal Methods in Computer-Aided Design (FMCAD) gives undergraduate and graduate students the opportunity to introduce their research to the Formal Methods community and receive feedback. In 2023, the event took place in Ames, Iowa, USA. Eighteen students were invited to give a short talk and present a poster of their work.

Since 2013, the FMCAD Student Forum provides a platform for undergraduate and graduate students at any career stage to present their research to the audience of the FMCAD conference. The 2023 edition of the FMCAD Student Forum follows the tradition of its predecessors, which took place in:

- Portland, Oregon, USA in 2013 [1]

- Lausanne, Switzerland in 2014 [2]

- Austin, Texas in 2015 [3] and 2018 [4]

- Mountain View, California, USA in 2016 [5]

- Vienna, Austria in 2017 [6]

- San Jose, California, USA in 2019 [7]

- Virtual in 2020 [8] and 2021 [9]

- Trento, Italy in 2022 [10]

FMCAD 2023 hosted the eleventh edition of the Student Forum. Graduate and undergraduate students were invited to submit two-page reports of their current research and ongoing work in the scope of the FMCAD conference. There were 16 submissions to the forum and all of them were accepted. The Student Forum program committee reviews were based on the overall quality, novelty of the work, its potential impact on the Formal Methods community, as well as the potential positive impact on the student to have the opportunity to participate in the forum. The accepted submissions covered a wide range of topics relevant to the FMCAD community, from foundational aspects of automated reasoning, to analysis and verification of software, hardware, and neural networks, as well as applications of formal methods to confidential computing, security and chemistry. Each submission received at least 2 reviews. The following contributions have been accepted<sup>1</sup>:

- Arijit Shaw: Towards Building A Scalable Bit-vector Model Counter

- Rachel Cleaveland: MemGlue: An Update-Based Cache Coherence Protocol for Heterogeneous Hardware

- Guy Amir: Finding Formal Explanations of Reactive **DNNs**

<sup>1</sup>Only student authors listed for brevity.

- Landon Taylor: Enhancing Property-Directed Reachability for Chemical Reaction Networks

- Benjamin Valpey: Formal Analysis of Tensor Core Math via SMT

- Samuel Coward: Datapath Optimization, Analysis and Verification: E-Graphs Can Do It All

- Joseph Tafese: Btor2MLIR: A Format for Hardware Verification

- Sophie Andrews and Matthew Sotoudeh: Incremental Bounded Model Checking as Program Source Changes

- Cayden Codel: Modifying the DDFW Local Search Algo-

- Viansa Schmulbach: Ordering Interventions for Hardware Security

- Áron Ricardo Perez-Lopez and Akshay Srivatsan: Mixed-Signal Verification via Digital Simulation

- Raya Elsaleh: On Facilitating the Development of Neural Networks Verifiers

- Muhammad Usama Sardar: Formal Specification and Verification of Attestation in Confidential Computing

- Charles Pert: Synthesizing Omega-Regular Expressions from Omega-automata

- Tephilla Prince: Two-dimensional Bounded Model Checking for Petri Nets

- Ankit Shukla: Simplifying Dependency Quantified Boolean Formulas with Biclique Cover Transformations

We formed a program committee to cover a wide range of topics so students could receive expert feedback on their work. The 2023 FMCAD Student Forum program committee consisted of Mikolas Janota (co-chair), Nina Narodytska (cochair), Haniel Barbosa, Jaroslav Bendík, Armin Biere, Nikolaj Bjørner, Martin Blicha, Martin Brain, Rayna Dimitrova, Katalin Fazekas, Mathias Fleury, Isabel Garcia, Arie Gurfinkel, Martin Jonas, Daniela Kaufmann, Konstantin Korovin, Corina Pasareanu, Mathias Preiner, Giles Reger, Andrew Reynolds, Karem Sakallah, Mark Santolucito, Carsten Sinz, Nestan Tsiskaridze, and Florian Zuleger.

We would like to thank the organizers of FMCAD, as well as the FMCAD Student Forum program committee, who have made the FMCAD Student Forum possible. We would like to thank FMCAD and NSF for providing travel support to students. Additionally, we are grateful to the student authors and their research mentors who have contributed their excellent work to the program.

#### REFERENCES

- [1] T. Wahl, "The FMCAD graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2013, Portland, OR, USA, October 20-23, 2013. IEEE, 2013, pp. 16–17. [Online]. Available: https://doi.org/10.1109/FMCAD.2013.7035523

- [2] R. Piskac, "The FMCAD 2014 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2014, Lausanne, Switzerland, October 21-24, 2014. IEEE, 2014, p. 13. [Online]. Available: https://doi.org/10.1109/FMCAD.2014.6987589

- [3] G. Weissenbacher, "The FMCAD 2015 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2015, Austin, Texas, USA, September 27-30, 2015, R. Kaivola and T. Wahl, Eds. IEEE, 2015, p. 8. [Online]. Available: https://doi.org/10.1109/FMCAD.2015.7542246

- [4] D. Jovanović and A. Reynolds, "The FMCAD 2018 graduate student forum," in 2018 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2018, pp. 1–1, https://www.cs.utexas.edu/users/hunt/FMCAD/ FMCAD18/student-forum/.

- [5] H. Hojjat, "The FMCAD 2016 graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD), 2016. IEEE, 2016, pp. 8–8, https://fmcad.forsyte.at/FMCAD16/student-forum.html.

- [6] K. Heljanko, "The FMCAD 2017 graduate student forum," in *Proceedings of the 17th Conference on Formal Methods in Computer-Aided Design*. FMCAD Inc, 2017, pp. 10–10, https://fmcad.org/FMCAD17/student-forum/.

- [7] G. Fedyukovich, "The FMCAD 2019 student forum," in 2019 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2019, pp. 1–1, https://fmcad.forsyte.at/FMCAD19/student-forum/.

- [8] P. Schrammel, "The FMCAD 2020 student forum," in 2020 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2020, pp. 1–1, https://fmcad.forsyte.at/FMCAD20/student-forum/.

- [9] M. Santolucito, "The FMCAD 2021 student forum," in 2021 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2021, pp. 1–1, https://fmcad.org/FMCAD21/student\_forum/.

- [10] M. Preiner, "The FMCAD 2023 student forum," in 2022 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2022, pp. 1–1, https://fmcad.org/FMCAD22/student\_forum/.

# Formally Explaining Neural Networks within Reactive Systems

Shahaf Bassan<sup>1,\*</sup>, Guy Amir<sup>1,\*</sup>, Davide Corsi<sup>2</sup>, Idan Refaeli<sup>1</sup>, and Guy Katz<sup>1</sup> <sup>1</sup>The Hebrew University of Jerusalem, Jerusalem, Israel, {shahaf, quyam, idan0610, quykatz}@cs.huji.ac.il <sup>2</sup>University of Verona, Verona, Italy, davide.corsi@univr.it

Abstract—Deep neural networks (DNNs) are increasingly being used as controllers in reactive systems. However, DNNs are highly opaque, which renders it difficult to explain and justify their actions. To mitigate this issue, there has been a surge of interest in explainable AI (XAI) techniques, capable of pinpointing the input features that caused the DNN to act as it did. Existing XAI techniques typically face two limitations: (i) they are heuristic, and do not provide formal guarantees that the explanations are correct; and (ii) they often apply to "one-shot" systems, where the DNN is invoked independently of past invocations, as opposed to reactive systems. Here, we begin bridging this gap, and propose a formal DNN-verification-based XAI technique for reasoning about multi-step, reactive systems. We suggest methods for efficiently calculating succinct explanations, by exploiting the system's transition constraints in order to curtail the search space explored by the underlying verifier. We evaluate our approach on two popular benchmarks from the domain of automated navigation; and observe that our methods allow the efficient computation of minimal and minimum explanations, significantly outperforming the state of the art. We also demonstrate that our methods produce formal explanations that are more reliable than competing, non-verification-based XAI techniques.

### I. Introduction

Deep neural networks (DNNs) [56] are used in numerous key domains, such as computer vision [54], natural language processing [24], computational biology [9], and more [23]. However, despite their tremendous success, DNNs remain "black boxes", uninterpretable by humans. This issue is concerning, as DNNs are prone to critical errors [19], [96] and unexpected behaviors [10], [28].

DNN opacity has prompted significant research on explainable AI (XAI) techniques [62], [77], [78], aimed at explaining the decisions made by DNNs, in order to increase their trustworthiness and reliability. Modern XAI methods are useful and scalable, but they are typically heuristic; i.e., there is no provable guarantee that the produced explanation is correct [20], [45]. This hinders the applicability of these approaches to critical systems, where regulatory bars are high [66].

These limitations provide ample motivation for formally explaining DNN decisions [20], [33], [39], [66]. And indeed, the formal verification community has suggested harnessing recent developments in DNN verification [13], [22], [26], [29], [36], [67], [69]–[71], [81], [86], [91], [92] to produce

\* Both authors contributed equally.

provable explanations for DNNs [17], [39], [44]. Typically, such approaches consider a particular input to the DNN, and return a subset of its features that caused the DNN to classify the input as it did. These subsets are called abductive explanations, prime implicants or PI-explanations [17], [44], [84]. This line of work constitutes a promising step towards more reliable XAI; but so far, existing work has focused on explaining decisions of "one-shot" DNNs, such as image and tabular data classifiers [17], [43], [44], and has not addressed more complex systems.

Modern DNNs are often used as controllers within elaborate reactive systems, where a DNN's decisions affect its future invocations. A prime example is deep reinforcement learning (DRL) [59], where DNNs learn control policies for complex systems [11], [18], [57], [63], [72], [85], [95]. Explaining the decisions of DRL agents (XRL) [32], [50], [64], [74] is an important domain within XAI; but here too, modern XRL techniques are heuristic, and do not provide formally correct explanations.

In this work, we make a first attempt at formally defining abductive explanations for multi-step decision processes. We propose novel methods for computing such explanations and supply the theoretical groundwork for justifying the soundness of these methods. Our framework is model-agnostic, and could be applied to diverse kinds of models; but here, we focus on DNNs, where producing abductive explanations is known to be quite challenging [14], [17], [44]. With DNNs, our technique allows us to reduce the number of times a network has to be unrolled, circumventing a potential exponential blow-up in runtime; and also allows us to exploit the reactive system's transition constraints, as well as the DNN's sensitivity to small input perturbations, to curtail the search space even further.

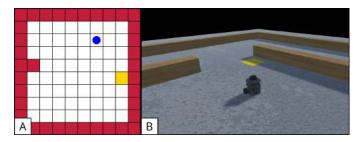

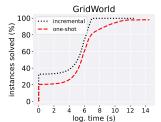

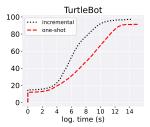

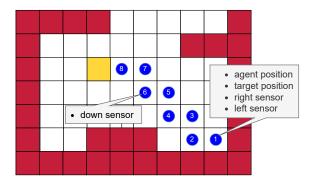

For evaluation purposes, we implemented our approach as a proof-of-concept tool, which is publicly available as an artifact accompanying this paper [16]. We used this tool to automatically generate explanations for two popular DRL benchmarks: a navigation system on an abstract, twodimensional grid, and a real-world robotic navigation system. Our evaluation demonstrates that our methods significantly outperform state-of-the-art, rigorous methods for generating abductive explanations, both in terms of efficiency and in the size of the explanation generated. When comparing our approach to modern, heuristic-based XAI approaches, our explanations were found to be significantly more precise. We regard these results as strong evidence of the usefulness of applying verification in the context of XAI.

The rest of this paper is organized as follows: Sec. II contains background on DNNs, their verification, and their formal explainability. Sec. III contains our definitions for formal abductive explanations and contrastive examples for reactive systems. In Sec. IV we propose different methods for computing such abductive explanations. We then evaluate these approaches in Sec. V, followed by a discussion of related work in Sec. VI; and we conclude in Sec. VII.

#### II. BACKGROUND

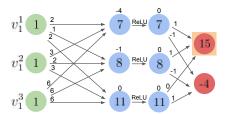

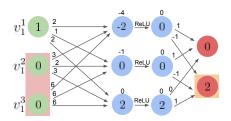

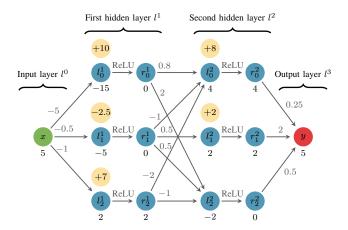

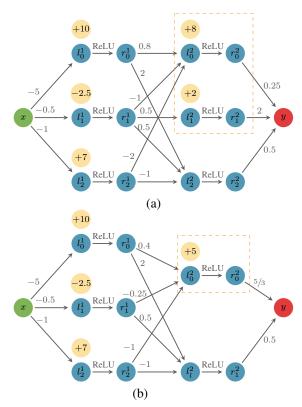

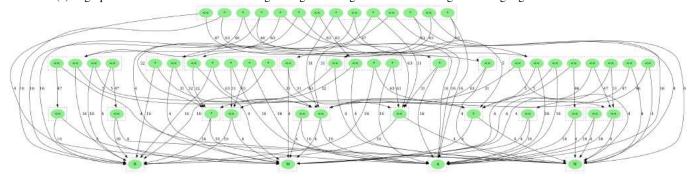

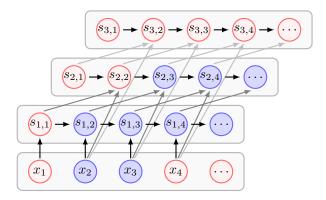

**DNNs.** Deep neural networks (DNNs) [56] are directed, layered graphs, whose nodes are referred to as neurons. They propagate data from the first (input) layer, through intermediate (hidden) layers, and finally onto an output layer. A DNN's output is calculated by assigning values (representing input features) to the input layer, and then iteratively calculating the neurons' values in subsequent layers. In classification, each output neuron corresponds to a class, and the input is classified as the class matching the greatest output. Fig. 1 depicts a toy DNN. The input layer has three neurons and is followed by a weighted-sum layer that calculates an affine transformation of the input values. For example, given input  $V_1 = [1, 1, 1]^T$ , the second layer evaluates to  $V_2 = [7, 8, 11]^T$ . This is followed by a ReLU layer, which applies the ReLU(x) = max(0, x)function to each value in the previous layer, resulting in  $V_3 = [7, 8, 11]^T$ . The output layer computes the weighted sum  $V_4 = \begin{bmatrix} 15, -4 \end{bmatrix}^T$ . Because the first output neuron has the greatest value,  $V_1$  is classified as the output class corresponding to that neuron.

Fig. 1: A toy DNN.

**DNN Verification.** We define a DNN verification query as a tuple  $\langle P, N, Q \rangle$ , where N is a DNN that maps an input vector x to an output vector y = N(x), P is a predicate over x, and Q is a predicate over y [51]. A DNN verifier needs to answer whether there exists some input x' that satisfies  $P(x') \wedge Q(N(x'))$  (a SAT result) or not (an UNSAT result). It is common to express P and Q in the logic of real arithmetic [61]. The problem of verifying DNNs is known to be NP-Complete [51].

Formal Explanations for Classification DNNs. A classification problem is a tuple  $\langle F, D, K, N \rangle$ , where (i)  $F = \{1, \dots, m\}$

is the feature set; (ii)  $D = \{D_1, D_2, \dots, D_m\}$  are the domains of individual features, and the entire feature space is  $\mathbb{F} = (D_1 \times D_2 \times \dots \times D_m)$ ; (iii)  $K = \{c_1, c_2, \dots, c_n\}$  represents the set of all classes; and (iv)  $N : \mathbb{F} \to K$  is the classification function, represented by a neural network. A *classification instance* is a pair (v, c), where  $v \in \mathbb{F}$ ,  $c \in K$ , and c = N(v). Intuitively, this means that N maps the input v to class c.

Formally explaining the instance (v,c) entails determining why v is classified as c. An explanation (also known as an abductive explanation) is defined as a subset of features,  $E \subseteq F$ , such that fixing these features to their values in v guarantees that the input is classified as c, regardless of features in  $F \setminus E$ . The features not part of the explanation are "free" to take on any arbitrary value, but cannot affect the classification. Formally, given an input  $v = (v_1, \ldots, v_m) \in \mathbb{F}$  classified by the neural network to N(v) = c, we define an explanation as a subset of features  $E \subseteq F$ , such that:

$$\forall x \in \mathbb{F}. \quad \bigwedge_{i \in E} (x_i = v_i) \to (N(x) = c) \tag{1}$$

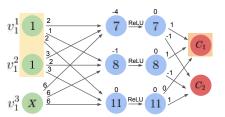

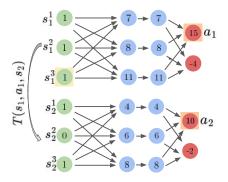

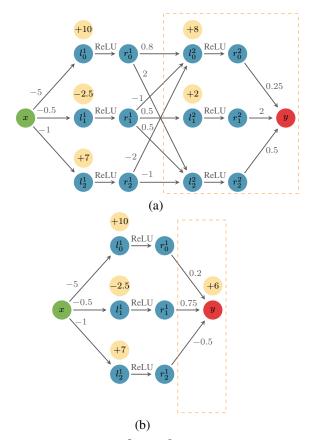

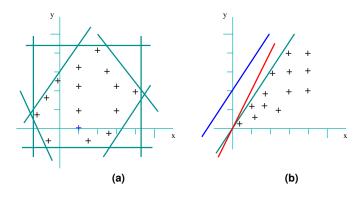

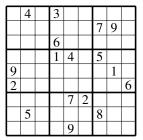

We demonstrate formal explanations using the running example from Fig. 1. For simplicity, assume that each input can only take the values 0 or 1. Fig. 2 shows that the set  $\{v_1^1, v_1^2\}$  is an explanation for the input vector  $V_1 = [1, 1, 1]^T$ : setting the first two features in  $V_1$  to 1 ensures that the classification is unchanged, regardless of the values the third feature takes.

Fig. 2:  $\{v_1^1, v_1^2\}$  is an explanation for input  $V_1 = [1, 1, 1]^T$ .

A candidate explanation E can be verified through a verification query  $\langle P, N, Q \rangle = \langle E = v, N, Q_{\neg c} \rangle$ , where E = v means that all of the features in E are set to their corresponding values in v, and  $Q_{\neg c}$  implies that the classification of this query is *not* c. If this query is UNSAT, then E is a valid explanation for the instance (v, c).

It is straightforward to show that the set of all features is a trivial explanation. However, smaller explanations typically provide more meaningful information regarding the decision of the classifier; and we thus focus on finding *minimal* and *minimum* explanations. A *minimal explanation* is an explanation  $E \subseteq F$  that ceases to be an explanation if any of its features are removed:

$$(\forall x \in \mathbb{F}. \quad \bigwedge_{i \in E} (x_i = v_i) \to (N(x) = c)) \land$$

$$(\forall j \in E. \ \exists y \in \mathbb{F}. \quad \bigwedge_{i \in E \setminus j} (y_i = v_i) \land (N(y) \neq c))$$

(2)

A minimal explanation for our running example,  $\{v_1^1, v_1^2\}$ , is depicted in Fig. 15 in the extended version of this paper [15].

A minimum explanation is a subset  $E \subseteq F$  which is a minimal explanation of minimum size; i.e., there is no other minimal explanation  $E' \neq E$  such that |E'| < |E|. Fig. 16 in the extended version of this paper [15] shows that  $\{v_1^3\}$  is a minimal explanation of minimal cardinality, and is hence a minimum explanation in our example.

Contrastive Examples. We define a contrastive example (also known as a *contrastive explanation (CXP)*) as a subset of features  $C \subseteq F$ , whose alteration may cause the classification of v to change. More formally:

$$\exists x \in \mathbb{F}. \quad \bigwedge_{i \in F \setminus C} (x_i = v_i) \land (N(x) \neq c)$$

(3)

A contrastive example for our running example appears in Fig. 3.

Fig. 3:  $\{v_1^2, v_1^3\}$  is a contrastive example for  $V_1 = [1, 1, 1]^T$ .

Checking whether C is a contrastive example can be performed using the query  $\langle P,N,Q\rangle = \langle (F \setminus C) = v,N,Q_{\neg c}\rangle$ : C is contrastive iff the quest is SAT. Any set containing a contrastive example is contrastive, and so we consider only contrastive examples that are minimal, i.e., which do not contain any smaller contrastive examples.

Contrastive examples have an important property: every explanation contains at least one element from every contrastive example [17], [43]. This can be used for showing that a minimum hitting set (MHS; see [15]) of all contrastive examples is a minimum explanation [41], [76]. In addition, there exists a duality between contrastive examples and explanations [43], [47]: minimal hitting sets of all contrastive examples are minimal explanations, and minimal hitting sets of all explanations are minimal contrastive examples. This relation can be proved by reducing explanations and contrastive examples to minimal unsatisfiable sets and minimal correction sets, respectively, where this duality is known to hold [43]. Calculating an MHS is NP-hard, but can be performed in practice using modern MaxSAT or MILP solvers [38], [58]. The duality is thus useful since computing contrastive examples and calculating their MHS is often more efficient than directly computing minimum explanations [17], [43], [44].

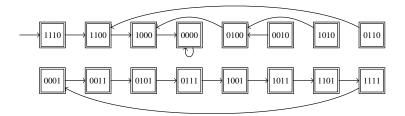

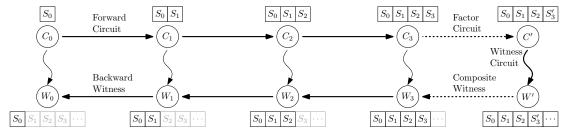

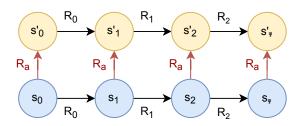

### III. K-STEP FORMAL EXPLANATIONS

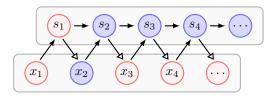

A reactive system is a tuple  $R = \langle S, A, I, T \rangle$ , where S is a set of states, A is a set of actions, I is a predicate over the states of S that indicates initial states, and  $T \subseteq S \times A \times S$  is a transition relation. In our context, a reactive system has an associated neural network  $N: S \to A$ . A k-step execution  $\mathcal{E}$  of

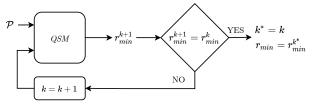

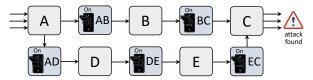

Fig. 4:  $(\{s^3\},\varnothing)$  is a (minimum) multi-step explanation for  $\mathcal E$

R is a sequence of k states  $(s_1,\ldots,s_k)$ , such that  $I(s_1)$  holds, and for all  $1 \le i \le k-1$  it holds that  $T(s_i,N(s_i),s_{i+1})$ . We use  $\mathcal{E}_S = (s_1,\ldots,s_k)$  to denote the sequence of k states visited in  $\mathcal{E}$ , and  $\mathcal{E}_A = (a_1,\ldots,a_k)$  to denote the sequence of k actions selected in these states. More broadly, a reactive system can be considered as a deterministic, finite-state transducer Mealy automaton [82]. Our goal is to better understand  $\mathcal{E}$ , by finding abductive explanations and contrastive examples that explain why N selected the actions in  $\mathcal{E}_A$ .

**K-Step Abductive Explanations.** Informally, we define an explanation E for a k-step execution  $\mathcal{E}$  as a subset of features of each of the visited states in  $\mathcal{E}_S$ , such that fixing these features (while freeing all other features) is sufficient for forcing the DNN to select the actions in  $\mathcal{E}_A$ . More formally,  $E = (E_1, \dots, E_k)$ , such that  $\forall x_1, x_2, \dots, x_k \in \mathbb{F}$ ,

$$\left(\bigwedge_{i=1}^{k-1} T(x_i, N(x_i), x_{i+1}) \wedge \bigwedge_{i=1}^{k} \bigwedge_{j \in E_i} (x_i^j = s_i^j)\right) \to \bigwedge_{i=1}^{k} N(x_i) = a_i$$

$$\tag{4}$$

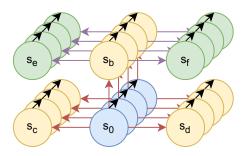

We continue with our running example. Consider the transition relation  $T = \{(s, a, s') \mid s^3 = s'^3\}$ ; i.e., we can transition from state s to state s' provided that the third input neuron has the same value in both states, regardless of the action selected in s. Observe the 2-step execution  $\mathcal{E}: s_1 = (1,1,1) \stackrel{c_1}{\to} s_2 = (1,0,1) \stackrel{c_1}{\to}$ , depicted in Fig. 4 (for simplicity, we omit the network's hidden neurons), and suppose we wish to explain  $\mathcal{E}_A = \{c_1,c_1\}$ . Because  $\{s^3\}$  is an explanation for the first step, and because fixing  $s_1^3$  also fixes the value of  $s_2^3$ , it follows that fixing  $s_1^3$  is sufficient to guarantee that action  $c_1$  is selected twice — i.e.,  $(\{s^3\},\varnothing)$  is a multi-step explanation for  $\mathcal{E}$ .

Given a candidate k-step explanation, we can check its validity by encoding Eq. 4 as a DNN verification query. This is achieved by unrolling the network N for k subsequent steps; i.e., by encoding a network that is k times larger than N, with input and output vectors that are k times larger than the original. We must also encode the transition relation T as a set of constraints involving the input values, to mimic k timesteps within a single feed-forward pass. We use  $N_{[i]}$  to denote an unrolling of the neural network N for i steps, for  $1 \le i \le k$ .

Using the unrolled network  $N_{[k]}$ , we encode the negation of Eq. 4 as the query  $\langle P, N, Q \rangle = \langle E = \mathcal{E}_S, N_{[k]}, Q_{\neg \mathcal{E}_A} \rangle$ , where  $E = \mathcal{E}_S$  means that we restrict the features in each subset  $E_i \in E$  to their corresponding values in  $s_i$ ; and  $Q_{\neg \mathcal{E}_A}$  indicates

Fig. 5:  $(\{s^3\}, \{s^3\})$  is a multi-step contrastive example for  $\mathcal{E}$ .

that in some step i, an action that is not  $a_i$  was selected by the DNN. An UNSAT result for this query indicates that E is an explanation for  $\mathcal{E}$ , because fixing E's features to their values forces the given sequence of actions to occur.

We can naturally define a *minimal* k-step explanation as a k-step explanation that ceases to be a k-step explanation when we remove any of its features. A *minimum* k-step explanation is a minimal k-step explanation of the lowest possible cardinality; i.e., there does not exist a k-step explanation  $E' = (E'_1, E'_2, \dots, E'_k)$  such that  $\sum_{i=1}^k |E'_i| < \sum_{i=1}^k |E_i|$ .

**K-Step Contrastive Examples.** A contrastive example C for an execution  $\mathcal E$  is a subset of features whose alteration can cause the selection of an action not in  $\mathcal E_A$ . A k-step contrastive example is depicted in Fig. 5: altering the features  $s_1^3$  and  $s_2^3$  may cause action  $c_2$  to be chosen instead of  $c_1$  in the second step. Formally, C is an ordered set of (possibly empty) subsets  $C = (C_1, C_2, \ldots, C_k)$ , such that  $C_i \subseteq F$ , and for which  $\exists x_1, x_2, \ldots, x_k \in \mathbb F$  such that

$$\left(\bigwedge_{i=1}^{k-1} T(x_i, N(x_i), x_{i+1})\right) \wedge \left(\bigwedge_{i=1}^{k} \bigwedge_{j \in F \setminus C_i} (x_i^j = s_i^j)\right) \wedge \left(\bigvee_{i=1}^{k} N(x_i) \neq a_i\right)$$

(5)

Similarly to multi-step explanations, C is a multi-step contrastive example iff the verification query:  $\langle P, N, Q \rangle = \langle (F \setminus C_1, F \setminus C_2, \dots, F \setminus C_k) = \mathcal{E}_S, N_{[k]}, Q_{\neg \mathcal{E}_A} \rangle$  is SAT.

## IV. COMPUTING FORMAL K-STEP EXPLANATIONS

We now propose four different methods for computing formal *k*-step explanations, focusing on *minimal* and *minimum* explanations. All four methods use an underlying DNN verifier to check candidate explanations, but differ in how they enumerate different explanation candidates until ultimately converging to an answer. We begin with the more straightforward methods.

**Method 1: A Single, K-Sized Step.** The first method is to encode the negation of Eq. 4 by unrolling all k steps of the network, as described in Sec. III. This transforms the problem into explaining a non-reactive, single-step system (e.g., a "one-shot" classifier). We can then use any existing abductive explanation algorithm for explaining the unrolled DNN (e.g., [17], [43], [44]).

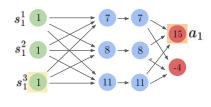

This method is likely to produce small explanation sets but is extremely inefficient. Encoding  $N_{\lceil k \rceil}$  results in an input

space roughly k times the size of any single-step encoding. Such an unrolling for our running example is depicted in Fig. 6. Due to the NP-completeness of DNN verification, this may cause an exponential growth in the verification time of each query. Since finding minimal explanations requires a linear number of queries (and for minimum explanations — a worst-case exponential number), this may cause a substantial increase in runtime.

Fig. 6: Finding explanations using a 2-step unrolling.

Method 2: Combining Independent, Single-Step Explanations. Here, we dismantle any k-step execution into k individual steps. Then, we *independently* compute an explanation for each step, using any existing algorithm, and without taking the transition relation into account. Finally, we concatenate these explanations to form a multi-step explanation. Fixing the features of the explanation in each step ensures that the ensuing action remains the same, guaranteeing the soundness of the combined explanation.

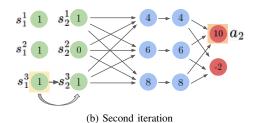

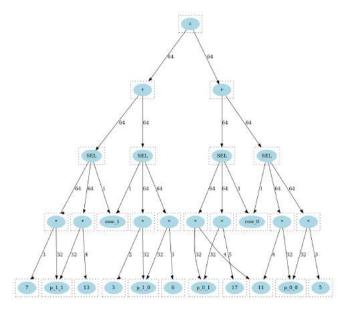

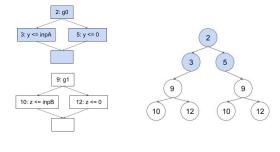

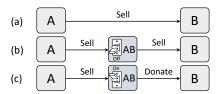

The downside of this method is that the resulting E need not be minimal or minimum, even if its constituent  $E_i$  explanations are minimal or minimum themselves; see Fig. 7. In this instance, finding a minimum explanation for each step results in the 2-step explanation ( $\{s^3\}, \{s^3\}$ ), which is not minimal—even though its components are minimum explanations for their respective steps. The reason for this phenomenon is that this method ignores the transition constraints and information flow across time-steps. This can result in larger and less meaningful explanations, as we later show in Sec. V.

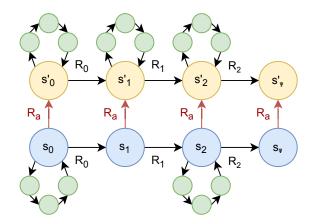

Method 3: Incremental Explanation Enumeration. We now suggest a scheme that takes into consideration the transition

Fig. 7: Explaining each step individually.

constraints between steps (unlike Method 2), but which encodes the verification queries for validating explanations in a more efficient manner than Method 1. The scheme relies on the following lemma:

**Lemma 1.** Let  $E = (E_1, E_2, ..., E_k)$  be a k-step explanation for execution  $\mathcal{E}$ , and let  $1 \le i \le k$  such that  $\forall j > i$  it holds that  $E_j = F$ . Let E' be the set obtained by removing a set of features  $F' \subseteq E_i$  from  $E_i$ , i.e.,  $E' = (E_1, ..., E_{i-1}, E_i \setminus F', E_{i+1}, ..., E_k)$ . In this case, fixing the features in E' prevents any changes in the first i-1 actions  $(a_1, ..., a_{i-1})$ ; and if any of the last k-i+1 actions  $(a_i, ..., a_k)$  change, then  $a_i$  must also change.

A proof appears in the extended version of this paper [15]. The lemma states that "breaking" an explanation E of  $\mathcal{E}$  at some step i (by removing features from the i'th step), given that the features in steps  $i+1,\ldots,k$  are fixed, causes  $a_i$  to change before any other action. In this scenario, we can determine whether E explains  $\mathcal{E}$  using a simplified verification query: we can check whether  $(E_1,\ldots,E_i)$  explains the first i steps of  $\mathcal{E}$ , regardless of steps  $i+1,\ldots,k$ . If so, then  $a_i$  cannot change; and from Lemma 1, no action in  $\mathcal{E}_A$  can change, and  $(E_1,\ldots,E_k)$  is an explanation for  $\mathcal{E}$ . Otherwise, E allows an action in  $\mathcal{E}_A$  to change, and it does not explain  $\mathcal{E}$ . We can leverage this property to efficiently enumerate candidates as part of a search for a minimal/minimum explanation for  $\mathcal{E}$ , as explained next.

Finding Minimal Explanations with Method 3. A common approach for finding minimal explanations for a "one-shot" classification instance is via a greedy algorithm, which dispatches a linear number of queries to the underlying verifier [44]. Such an algorithm can start with the explanation set to be the entire feature space, and then iteratively attempt to remove features. If removing a feature allows misclassification, the algorithm keeps it as part of the explanation; otherwise, it removes the feature and continues. A pseudo-code for this approach appears in Alg. 1.

**Algorithm 1** Greedy-Minimal-Explanation

**Input** N (DNN), F (N's features), v (values), c (predicted class)

- 1: Explanation  $\leftarrow F$

- 2: for each  $f \in F$  do

- 3: **if** verify ((Explanation $\setminus$ {f})=v,N, $Q_{\neg c}$ ) is UNSAT **then**

- Explanation  $\leftarrow$  Explanation  $\setminus \{f\}$

- 5: return Explanation

We suggest performing a similar process for explaining  $\mathcal{E}$ . We start by fixing all features in all states of  $\mathcal{E}$  to their values; i.e., we start with  $E = (E_1, \dots, E_k)$  where  $E_i = F$  for all i, and then perform the following steps:

First, we iteratively remove individual features from  $E_1$ , each time checking whether the modified E remains an explanation for  $\mathcal{E}$ . Since all features in steps  $2, \ldots, k$  are fixed,

it follows from Lemma 1 that checking whether the modified E explains  $\mathcal{E}$  is equivalent to checking whether the modified  $E_1$  explains the selection of  $a_1$ . Thus, we perform a process that is identical to the one in the greedy Alg. 1 for finding a minimal explanation for a "one-shot" classification DNN. At the end of this phase, we are left with  $E = (E_1, \ldots, E_k)$  where  $E_i = F$  for all i > 1 and  $E_1$  was reduced by removing features from it. We keep all current features in E fixed for the following steps.

Second, we begin to iteratively remove features from  $E_2$ , each time checking whether the modified E still explains  $\mathcal{E}$ . Since the features in steps  $3, \ldots, k$  are entirely fixed, it suffices (from Lemma 1) to check whether the modified  $(E_1, E_2)$  explains the selection of the first two actions  $(a_1, a_2)$  of  $\mathcal{E}_A$ . This is performed by checking whether

$$(\forall x_1, x_2 \in \mathbb{F}. \quad T(x_1, a_1, x_2) \land \bigwedge_{j \in E_1} (x_1^j = s_1^j) \land$$

$$\bigwedge_{j \in E_2} (x_2^j = s_2^j)) \to N(x_2) = a_2$$

(6)

We do not need to require that  $N(x_1) = a_1$  (as in Method 1) — this is guaranteed by Lemma 1. This is significant, because it exempts us from encoding the neural network twice as part of the verification query. We denote the negation of Eq. 6 for validating  $(E_1, E_2)$  as:  $\langle P, N, Q \rangle = \langle (E_1, E_2) = \mathcal{E}_{S_{[2]}}, N, Q_{\neg a_2} \rangle$ .

Third, we continue this iterative process for all k steps of  $\mathcal{E}$ , and find the minimal explanation for each step separately. In step i, for each query we encode i transitions and check whether the modified E still explains the first i steps of  $\mathcal{E}$  (by encoding  $\langle (E_1, \ldots, E_i) = \mathcal{E}_{S[i]}, N, Q_{\neg a_i} \rangle$ ), which does not require encoding the DNN i times. The correctness of each step follows directly from Lemma 1.

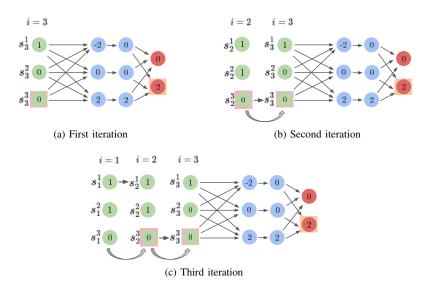

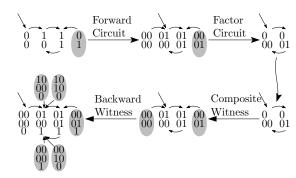

The pseudo-code for this process appears in Alg. 2. The minimality of the resulting explanation holds because removing any feature from this explanation would allow the action in that step to change (since minimality is maintained in each step of the algorithm). An example of the first two iterations of this process on our running example appears in Fig. 8: in the first iteration, we attempt to remove features from the first step, until converging to an explanation  $E_1$ . In the second iteration, while the features in  $E_1$  remain fixed to their values, we encode the constraints of the transition relation  $T(s_1, a_1, s_2)$ between the first two steps, and dispatch queries to verify candidate explanations for the second step — until converging to a minimal explanation  $(E_1, E_2)$ . In this case,  $E_2 = \emptyset$ , and  $(\{s^3\},\emptyset)$  is a valid explanation for the 2-step execution, since fixing the value of  $s_1^3$  determines the value of  $s_2^3$  — which forces the selection of  $a_2$  in the second step.

We emphasize that incrementally enumerating candidate explanations for a k-step execution in this way is preferable to simply finding a minimal explanation by encoding verification queries that encompass all k-steps, à la Method 1: (i) in each iteration, we dispatch a verification query involving only a single invocation of the DNN, thus circumventing the linear growth in the network's size — which causes an exponential worst-case increase in verification times; and (ii) in each

(a) First iteration

Fig. 8: Running Method 3 for finding minimal explanations, for two iterations.

iteration, we do not need to encode the entire set of k disjuncts (from the negation of Eq. 4), since we only need to validate  $a_i$  on the i'th iteration, and not all actions of  $\mathcal{E}_A$ .

Algorithm 2 Incremental-Minimal-Explanation -Enumeration

**Input** N (DNN), F (N's features),  $\mathcal{E}$  (execution of length k to explain)

- 1: Explanation  $\leftarrow (E_1, \dots, E_k)$  where  $E_i = F$  for all  $1 \le i \le k$

- 2: for each  $i \in \{1,...,k\}$  and  $f \in E_i$  do

- 3: if verify  $((E_1,\ldots,E_i\smallsetminus f)=\mathcal{E}_{S_{[i]}},N,Q_{\neg a_i})$  is UNSAT then

- 4:  $E_i \leftarrow E_i \setminus f$

- 5: return Explanation

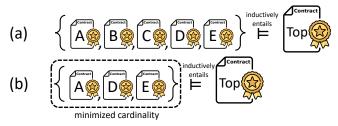

Finding Minimum Explanations with Method 3. We can also use our proposed enumeration to efficiently find *minimum* explanations, using a recursive approach. In each step  $i=1,\ldots,k$ , we iterate over all the possible explanations, each time considering a candidate explanation and recursively invoking the procedure for step i+1. In this way, we iterate over all the possible multi-step explanation candidates and can return the smallest one that we find. This process is described in Alg. 3.

Finding a minimum explanation in this manner is superior to using Method 1, for the same reasons noted before. In addition, the exponential blowup here is in the number of explanations in each step, and not in the entire number of features in each step — which is substantially smaller in many cases. Nevertheless, as the method advances through steps, it is expected to be significantly harder to iterate over all the candidate explanations. We discuss more efficient ways for finding global minimum explanations in Method 4.

**Algorithm 3** Incremental-Minimum-Explanation-Enumeration

Input N (DNN), F (N's features),  $\mathcal{E}$  (execution to explain)  $\triangleright$  Global Variables

- 1: AllExplanations ← ALL-EXPLANATION-

- 2: RECURSIVE-SEARCH( $\emptyset$ , 1)

- 3: **return**  $E \in AllExplanations such that <math>E$  is with minimum cardinality

## Algorithm 4 All-Explanation-Recursive-Search

**Input** E (explanation), i (step number)

- 1: if i = k then

- 2: **return** E

- 3: AllExplanations  $\leftarrow \emptyset$

- 4: for each subset F' of F do

- 5: **if** verify  $(E \cdot (F') = \mathcal{E}_{S_{[i]}}, N, Q_{\neg a_i})$  is UNSAT **then**

- 6: Explanations ← All-Explanation-

- 7: Recursive-Search (E  $\cdot$  (F'), i+1)

- 8: AllExplanations ← AllExplanations ∪ Explanations

- 9: return AllExplanations

## Method 4: Multi-Step Contrastive Example Enumeration.

As mentioned earlier, a common approach for finding minimum explanations is to find all contrastive examples, and then calculate their minimum hitting set (MHS). Because DNNs tend to be sensitive to small input perturbations [87], small contrastive examples are often easy to find, and this can expedite the process significantly [17]. When performing this procedure on a multi-step execution  $\mathcal{E}$ , we show that it is possible to enumerate contrastive example candidates in a more efficient manner than simply using the encoding from Method 1.

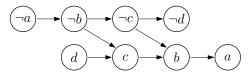

**Lemma 2.** Let  $\mathcal{E}$  be a k-step execution, and let  $C = (C_1, \ldots, C_k)$  be a minimal contrastive example for  $\mathcal{E}$ ; i.e., altering the features in C can cause at least one action in  $\mathcal{E}_A$  to change. Let  $1 \le i \le k$  denote the index of the first action  $a_i$  that can be changed by features in C. It holds that:  $C_i \ne \emptyset$ ;  $C_j = \emptyset$  for all j > i; and if there exists some l < i such that  $C_l \ne \emptyset$ , then all sets  $\{C_l, C_{l+1}, \ldots, C_i\}$  are not empty.

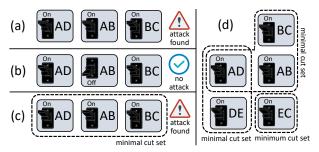

The lemma gives rise to the following scheme. We examine some contrastive example C' of a set of subsequent steps of  $\mathcal{E}$ . For simplicity, we discuss the case where  $C' = (C'_i)$  involves only a single step i; but the technique generalizes to subsets of steps, as well. Such a  $C'_i$  can be found using a "one-shot" verification query on step i, without encoding the transition relation or unrolling the network. Our goal is to use C' to find many contrastive examples for  $\mathcal{E}$ , and use them in computing the MHS. We observe that there are three possible cases:

- 1)  $C = (\emptyset, ..., \emptyset, C'_i, \emptyset, ..., \emptyset)$  already constitutes a contrastive example for  $\mathcal{E}$ . In this case, we say that  $C' = (C'_i)$  is an *independent contrastive example*.

- 2) The features in  $C_i'$  can cause a skew from  $\mathcal E$  only

when features from preceding steps  $l, \ldots, i-1$  (for some l < i) are also altered. In this case, we say that C' is a *dependent contrastive example*, and that it depends on steps  $l, \ldots, i-1$ ; and together, the features from all these steps form the contrastive example  $C = (\varnothing, \ldots, \varnothing, C_l, \ldots, C_{i-1}, C'_i, \varnothing, \ldots, \varnothing)$  for  $\mathcal{E}$ .

3) C' is a *spurious contrastive example*: the first i-1 steps in  $\mathcal{E}$ , and the constraints that the transition relation imposes, prevent the features freed by  $C'_i$  from causing any action besides  $a_i$  to be selected in step i.

Fig. 9 illustrates the three cases. The first case is identical to the one from Fig. 5, where  $(\{s^3\})$  is a dependent contrastive example of the second step, which depends on the previous step and is part of a larger contrastive example:  $(\{s^3\}, \{s^3\})$ . In the second case, assume that T requires that  $s_3^1 + s_3^2 \neq 1$  for any feasible transition. Thus, the assignment for  $s_3^2$  which may cause the second action in the sequence to change is not reachable from the previous step, and hence  $(\{s^3\})$  is a spurious contrastive example of the second step. In the third case, assume that T allows all transitions, and hence  $(\{s^3\})$  is an independent contrastive example for the second step; and so  $(\varnothing, \{s^3\})$  is a contrastive example of the entire execution.

It follows from Lemma 2 that one of these three cases must always apply. We next explain how verification can be used to classify each contrastive example of a subset of steps into one of these three categories. If C' is independent, it can be used as-is in computing the MHS; and if it is spurious, it should be ignored. In the case where C' is dependent, our goal is to find all multi-step contrastive examples that contain it, for the purpose of computing the MHS. We next describe a recursive algorithm, termed *reverse incremental enumeration* (RIE), that achieves this.

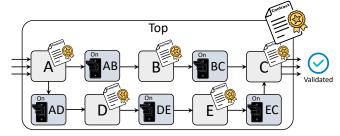

Reverse Incremental Enumeration. Given a contrastive example C' containing features from a set of subsequent steps of  $\mathcal{E}$ , we propose to classify it into one of the three categories by iteratively dispatching queries that check the reachability of C' from the previous steps of the sequence. We execute this procedure by recursively enumerating contrastive examples in previous steps. For simplicity, we assume again that  $C' = (C'_i)$  is a single-step contrastive example of step i.

1) For checking whether C' is an independent contrastive example of  $\mathcal{E}$ , we set  $C_{i-1} = \emptyset$  and  $C_i = C'_i$ , and check whether  $C = (C_{i-1}, C_i)$  is a contrastive example for steps i-1 and i. This is achieved by dispatching the following query:  $\exists x_{i-1}, x_i \in \mathbb{F}$  such that:

$$T(x_{i-1}, N(x_{i-1}), x_i) \wedge \left( \bigwedge_{l=i-1}^{i} \bigwedge_{j \in F \setminus C_l} (x_l^j = s_l^j) \right) \wedge (N(x_i) \neq a_i)$$

(7)

If the verifier returns SAT,  $C'_i$  is independent of step i-1, and hence independent of all steps  $1, \ldots, i-1$ . Hence, C' is an independent contrastive example of  $\mathcal{E}$ .

2) If the query from Eq. 7 returns UNSAT, we now attempt to decide whether C' is dependent. We achieve this through additional verification queries, again setting  $C_i = C'_i$ , but

now setting  $C_{i-1}$  to a *non empty* set of features — once for every possible set of features, separately. We again generate a query using the encoding from Eq. 7, and if the verifier returns SAT it follows that C' is dependent on step i-1, and that  $C''=(C_{i-1},C_i)$  is a contrastive example for steps i-1 and i. We recursively continue with this enumeration process, to determine whether C'' is independent, dependent of step i-2, or a spurious contrastive example.

3) In case the previous phases determine that C' is neither independent nor part of a larger contrastive example, we conclude that it is spurious.

An example of a single reverse incremental enumeration step on a contrastive example C' in our running example is depicted in Fig. 10, and its recursive call is shown in Alg. 5 (Cxps denotes the set of all multi-step contrastive examples containing the initial C').

Algorithm 5 Reverse Incremental Enumeration (RIE)

**Input** i (starting index), j (reversed index),  $C' = (C'_i, \dots, C'_i)$

- 1: **if** j=1 then

- 2: **return** C'  $\triangleright$  C' is trivially independent of steps j < 1

- 3: **if**  $(\emptyset, C'_j, \dots, C'_i)$  is a contrastive example of steps  $j 1 \dots i$  **then**

- 4: **return**  $(C_l \mid \forall 1 \le l \le j-1, C_l = \emptyset) \cdot C'$   $\triangleright$  C' is independent of step j-1

- 5: Cxps ← Ø

- 6: for each subset  $C_f$  of F do

- 7: **if**  $(C_f, C'_j, \dots, C'_i)$  is a contrastive example of steps  $j-1 \dots i$  **then**

- 8:  $\operatorname{Cxps} \leftarrow \operatorname{Cxps} \cup \operatorname{RIE}(i, j 1, C_f) \qquad \triangleright C'$  is dependent of step j 1

Using reverse incremental enumeration, we can find all multi-step contrastive examples of  $\mathcal{E}$ :

- 1) First, we find all contrastive examples for the first step of  $\mathcal{E}$ . This is again the same as finding contrastive examples of a "one-shot" classification problem, and can be performed efficiently [17], via Alg. 7. We first enumerate all contrastive examples of size 1 (i.e., contrastive *singletons*); then all contrastive examples of size 2 that do not contain contrastive singletons within them; and then continue this process for all  $1 \le i \le |F|$  ("skipping" all non-minimal cases).

- 2) Next, we search for all contrastive examples for the second step of  $\mathcal{E}$ , in the same manner. We perform a reverse incremental enumeration on each contrastive example found, obtaining all contrastive examples for steps 1 and 2.

- 3) We continue iteratively, each time visiting a new step i and reversely enumerating all contrastive examples that affect steps  $1, \ldots, i$ . We stop when we reach the final step, i = k.

Fig. 9:  $(\{s^3\})$  as a dependent, spurious and independent contrastive example.

Fig. 10: An illustration of reverse incremental enumeration. We start with a single-step contrastive example,  $C_3' = \{s^3\}$  for the third step of the execution. In the second iteration, we find that  $(C_3')$  is dependent on the previous step, and that  $(\{s^3\}, \{s^3\})$  constitutes a contrastive example for steps 2 and 3. In the third iteration,  $(\{s^3\}, \{s^3\})$  is found to be independent of the first step, and hence  $(\emptyset, \{s^3\}, \{s^3\})$  is a contrastive example for  $\mathcal{E}$ .

The full enumeration process for finding all contrastive examples of  $\mathcal{E}$  is described fully in Alg. 6, which invokes Alg. 7.

```

Algorithm 6 Enumerate-All-Cxps

```

7: return Cxps

Input N (DNN), F (N's features),  $\mathcal{E}$  (execution to explain)  $\triangleright$  Global Variables

```

1: Cxps \leftarrow \emptyset

2: for each i \in \{1, ..., k\} do

3: CxpCandidates \leftarrow Enumerate-All-Cxps-In-4: Single-Step(i)

5: for each Cxp \in CxpCandidates do

6: Cxps \leftarrow Cxps \cup Rie((Cxp), i, i)

```

We also make the following observation: we can further expedite the enumeration process by discarding sets that contain contrastive examples within them since we are specifically searching for minimal contrastive examples. For instance, in the given example in Fig. 10, if we find  $(\emptyset, s^1, \emptyset)$  as a contrastive example for the entire multi-step instance, we no longer need to consider sets in step 2 that contain  $s^1$  when

Algorithm 7 Enumerate-All-Cxps-In-Single-Step Input N (DNN), F (N's features),  $\mathcal E$  (execution to explain), i (step number)

- 1: Cxps  $\leftarrow \emptyset$   $\triangleright$  denotes the set of all contrastive examples

- 2: for each  $1 \le i \le |F|$  do

- 3: **for each** subset c of F of length i not containing sets from Cxps **do**

- 4: **if** verify  $(F \setminus c = s_i, N, Q_{\neg a_i})$  is SAT **then**

- 5:  $Cxps \leftarrow Cxps \cup c$

- 6: **return** Cxps

iterating in reverse from step 3 to step 2. Our evaluation shows that this approach can significantly improve performance as the increasing number of contrastive examples found in previous steps greatly reduces the search space.

Of course, our approach's worst-case complexity is still exponential in the number of steps, k, because each dependent contrastive example requires a recursive call that potentially enumerates all contrastive examples for the previous step. However, the number of recursive iterations is limited by

the dependency between steps. For instance, if contrastive examples in step i are only dependent on step i-1 and not on step i-2, the recursive iterations will be limited to 2. Additionally, skipping the verification of candidates containing contrastive examples found in previous steps can also significantly reduce runtime.

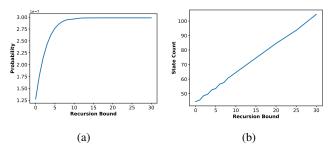

#### V. EVALUATION

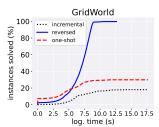

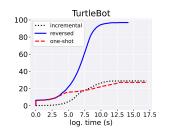

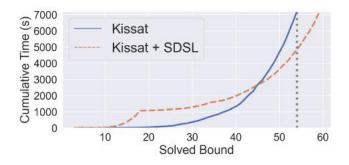

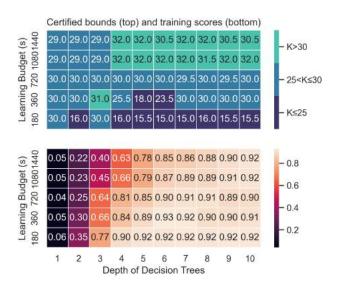

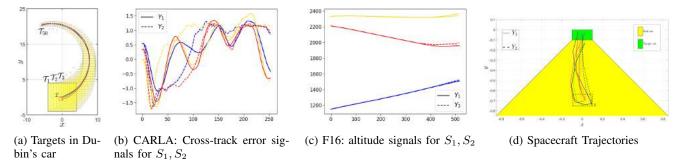

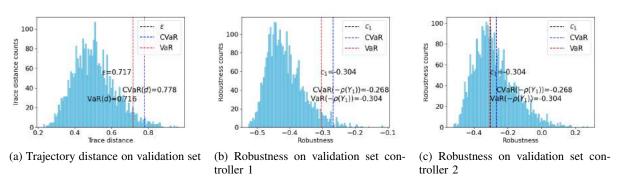

Implementation and Setup. We created a proof-of-concept implementation of all aforementioned approaches and benchmarks [16]. To search for explanations, our tool [16] dispatches verification queries using a backend DNN verifier (we use *Marabou* [52], previously employed in additional studies [2]–[7], [21], [75], although other engines may also be used). The queries encode the architecture of the DNN in question, the transition constraints between consecutive steps of the reactive system, and the candidate explanation or contrastive example being checked. Calculating the MHS, when relevant, was done using RC-2, a MaxSAT-based tool of the PySat toolkit [42].