Bernd Finkbeiner Laura Kovács (Eds.)

# Tools and Algorithms for the Construction and Analysis of Systems

30th International Conference, TACAS 2024 Held as Part of the European Joint Conferences on Theory and Practice of Software, ETAPS 2024 Luxembourg City, Luxembourg, April 6–11, 2024 Proceedings, Part III

# **Lecture Notes in Computer Science**

14572

# Founding Editors

Gerhard Goos, Germany Juris Hartmanis, USA

## **Editorial Board Members**

Elisa Bertino, USA Bernhard Steffen D, Germany Wen Gao, China Moti Yung D, USA

# Advanced Research in Computing and Software Science Subline of Lecture Notes in Computer Science

# Subline Series Editors

Giorgio Ausiello, *University of Rome 'La Sapienza', Italy* Vladimiro Sassone, *University of Southampton, UK*

# Subline Advisory Board

Susanne Albers, *TU Munich, Germany*Benjamin C. Pierce, *University of Pennsylvania, USA*Bernhard Steffen , *University of Dortmund, Germany*Deng Xiaotie, *Peking University, Beijing, China*Jeannette M. Wing, *Microsoft Research, Redmond, WA, USA*

More information about this series at https://link.springer.com/bookseries/558

Bernd Finkbeiner · Laura Kovács Editors

# Tools and Algorithms for the Construction and Analysis of Systems

30th International Conference, TACAS 2024 Held as Part of the European Joint Conferences on Theory and Practice of Software, ETAPS 2024 Luxembourg City, Luxembourg, April 6–11, 2024 Proceedings, Part III

Editors

Bernd Finkbeiner

CISPA Helmholtz Center for Information

Security

Saarbrücken, Germany

Laura Kovács D TU Wien Vienna, Austria

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-031-57255-5 ISBN 978-3-031-57256-2 (eBook) https://doi.org/10.1007/978-3-031-57256-2

© The Editor(s) (if applicable) and The Author(s) 2024. This book is an open access publication.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (<a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

Paper in this product is recyclable.

# ETAPS Foreword

Welcome to the 27th ETAPS! ETAPS 2024 took place in Luxembourg City, the beautiful capital of Luxembourg.

ETAPS 2024 is the 27th instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference established in 1998, and consists of four conferences: ESOP, FASE, FoSSaCS, and TACAS. Each conference has its own Program Committee (PC) and its own Steering Committee (SC). The conferences cover various aspects of software systems, ranging from theoretical computer science to foundations of programming languages, analysis tools, and formal approaches to software engineering. Organising these conferences in a coherent, highly synchronized conference programme enables researchers to participate in an exciting event, having the possibility to meet many colleagues working in different directions in the field, and to easily attend talks of different conferences. On the weekend before the main conference, numerous satellite workshops took place that attracted many researchers from all over the globe.

ETAPS 2024 received 352 submissions in total, 117 of which were accepted, yielding an overall acceptance rate of 33%. I thank all the authors for their interest in ETAPS, all the reviewers for their reviewing efforts, the PC members for their contributions, and in particular the PC (co-)chairs for their hard work in running this entire intensive process. Last but not least, my congratulations to all authors of the accepted papers!

ETAPS 2024 featured the unifying invited speakers Sandrine Blazy (University of Rennes, France) and Lars Birkedal (Aarhus University, Denmark), and the invited speakers Ruzica Piskac (Yale University, USA) for TACAS and Jérôme Leroux (Laboratoire Bordelais de Recherche en Informatique, France) for FoSSaCS. Invited tutorials were provided by Tamar Sharon (Radboud University, the Netherlands) on computer ethics and David Monniaux (Verimag, France) on abstract interpretation.

As part of the programme we had the first ETAPS industry day. The goal of this day was to bring industrial practitioners into the heart of the research community and to catalyze the interaction between industry and academia. The day was organized by Nikolai Kosmatov (Thales Research and Technology, France) and Andrzej Wasowski (IT University of Copenhagen, Denmark).

ETAPS 2024 was organized by the SnT - Interdisciplinary Centre for Security, Reliability and Trust, University of Luxembourg. The University of Luxembourg was founded in 2003. The university is one of the best and most international young universities with 6,000 students from 130 countries and 1,500 academics from all over the globe. The local organisation team consisted of Peter Y.A. Ryan (general chair), Peter B. Roenne (organisation chair), Maxime Cordy and Renzo Gaston Degiovanni (workshop chairs), Magali Martin and Isana Nascimento (event manager), Marjan Skrobot (publicity chair), and Afonso Arriaga (local proceedings chair). This team also

organised the online edition of ETAPS 2021, and now we are happy that they agreed to also organise a physical edition of ETAPS.

ETAPS 2024 is further supported by the following associations and societies: ETAPS e.V., EATCS (European Association for Theoretical Computer Science), EAPLS (European Association for Programming Languages and Systems), and EASST (European Association of Software Science and Technology).

The ETAPS Steering Committee consists of an Executive Board, and representatives of the individual ETAPS conferences, as well as representatives of EATCS, EAPLS, and EASST. The Executive Board consists of Marieke Huisman (Twente, chair), Andrzej Wasowski (Copenhagen), Thomas Noll (Aachen), Jan Kofroň (Prague), Barbara König (Duisburg), Arnd Hartmanns (Twente), Caterina Urban (Inria), Jan Křetínský (Munich), Elizabeth Polgreen (Edinburgh), and Lenore Zuck (Chicago).

Other members of the steering committee are: Maurice ter Beek (Pisa), Dirk Beyer (Munich), Artur Boronat (Leicester), Luís Caires (Lisboa), Ana Cavalcanti (York), Ferruccio Damiani (Torino), Bernd Finkbeiner (Saarland), Gordon Fraser (Passau), Arie Gurfinkel (Waterloo), Reiner Hähnle (Darmstadt), Reiko Heckel (Leicester), Marijn Heule (Pittsburgh), Joost-Pieter Katoen (Aachen and Twente), Delia Kesner (Paris), Naoki Kobayashi (Tokyo), Fabrice Kordon (Paris), Laura Kovács (Vienna), Mark Lawford (Hamilton), Tiziana Margaria (Limerick), Claudio Menghi (Hamilton and Bergamo), Andrzej Murawski (Oxford), Laure Petrucci (Paris), Peter Y.A. Ryan (Luxembourg), Don Sannella (Edinburgh), Viktor Vafeiadis (Kaiserslautern), Stephanie Weirich (Pennsylvania), Anton Wijs (Eindhoven), and James Worrell (Oxford).

I would like to take this opportunity to thank all authors, keynote speakers, attendees, organizers of the satellite workshops, and Springer Nature for their support. ETAPS 2024 was also generously supported by a RESCOM grant from the Luxembourg National Research Foundation (project 18015543). I hope you all enjoyed ETAPS 2024.

Finally, a big thanks to both Peters, Magali and Isana and their local organization team for all their enormous efforts to make ETAPS a fantastic event.

April 2024

Marieke Huisman ETAPS SC Chair ETAPS e.V. President

# **Preface**

This three-volume proceedings contains the papers presented at the 30th International Conference on Tools and Algorithms for the Construction and Analysis of Systems (TACAS 2024). TACAS 2024 was part of the 27th European Joint Conferences on Theory and Practice of Software (ETAPS 2024), which was held between April 6–11, 2024, in Luxembourg City, Luxembourg.

TACAS is a forum for researchers, developers and users interested in rigorous tools and algorithms for the construction and analysis of systems. The conference aims to bridge the gaps between different communities with this common interest and to support them in their quest to improve the utility, reliability, flexibility, and efficiency of tools and algorithms for building systems. TACAS 2024 interleaves and integrates various disciplines, including formal verification of software and hardware systems, static analysis, probabilistic programming, program synthesis, concurrency, testing, simulations, verification of machine learning/autonomous systems, Cyber-Physical Systems, SAT/SMT solving, automated and interactive theorem proving, and proof checking.

There were four submission categories for TACAS 2024:

- 1. **Regular research papers** identifying and justifying a principled advance to the theoretical foundations for the construction and analysis of systems.

- 2. **Case study papers** describing the application of techniques developed by the community to a single problem or a set of problems of practical importance, preferably in a real-world setting.

- 3. **Regular tool papers** presenting a novel tool or a new version of an existing tool built using novel algorithmic and engineering techniques.

- 4. **Tool demonstration papers** demonstrating a new tool or application of an existing tool on a significant case-study.

Regular research, case study, and regular tool paper submissions were restricted to 16 pages, whereas tool demonstration papers to 6 pages, excluding the bibliography and appendices.

TACAS 2024 received 159 submissions, consisting of 114 regular research papers, 10 case study papers, 28 regular tool papers, and 7 tool demonstration papers. Each submission was assigned for review to at least three Program Committee (PC) members, who made use of subreviewers. Regular research papers were reviewed in doubleblind mode, whereas case study, regular tool, and tool-demonstration papers were reviewed using a single-blind reviewing process.

Similarly to previous years, it was possible to submit an artifact alongside a paper. Artifact submission was mandatory for regular tool and tool demo papers, and voluntary for regular research and case study papers at TACAS 2024. An artifact might consist of a tool, models, proofs, or other data required for validation of the results of the paper. The Artifact Evaluation Committee (AEC) was tasked with reviewing the

artifacts, based on their documentation, ease of use, and, most importantly, whether the results presented in the corresponding paper could be accurately reproduced. Most of the evaluation was carried out using a standardized virtual machine to ensure consistency of the results, except for those artifacts that had special hardware or software requirements. Artifact evaluation at TACAS 2024 consisted of two rounds. The first round implemented the mandatory artifact evaluation of regular tool and tool demonstration papers; this round was carried out in parallel with the work of the PC. The judgment of the AEC was communicated to the PC and weighed in their discussion. The second round of artifact evaluation carried out the voluntary artifact evaluation of regular research and case study papers, and took place after paper acceptance notifications were sent out; authors of accepted regular research and case study papers were able to update and revise their respective artifacts before artifact evaluation started. In both rounds, the AEC provided 3 reviews per artifact and anonymously communicated with the authors to resolve apparent technical issues. In total, 104 artifacts were submitted and the AEC evaluated a total of 62 artifacts regarding their availability, functionality, and/or reusability. Papers with an artifact that were successfully evaluated include one or more badges on the first page, certifying the respective properties.

Selected papers were requested to provide a rebuttal in case a PC review gave rise to questions. Using the review reports and rebuttals, the PC had a thorough discussion on each paper. For regular tool and tool demonstration papers, the PC also discussed the corresponding artifact, using the AEC recommendations. As a result, the PC decided to accept 53 papers, out of which there were 35 regular research papers, 11 regular tool papers, 3 case study papers, and 4 tool demonstration papers. This corresponds to an overall acceptance rate of 33%. Each accepted paper at TACAS 2024 had either all positive reviews and/or a "championing" PC member who argued in favor of accepting the paper. All accepted papers at TACAS 2024 had a positive average review score.

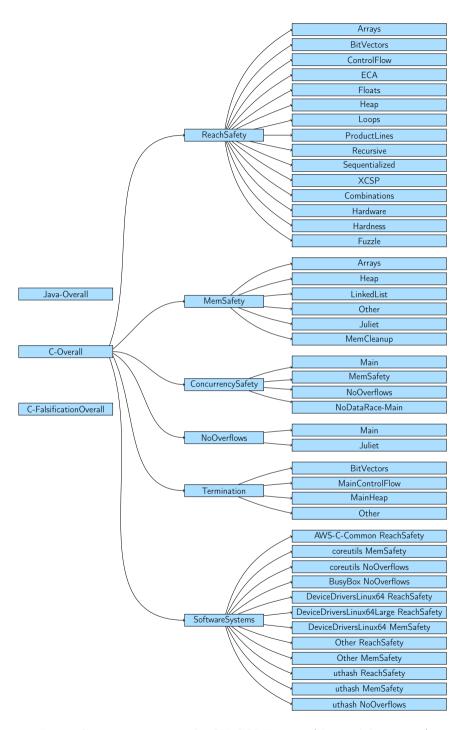

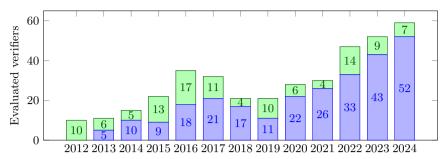

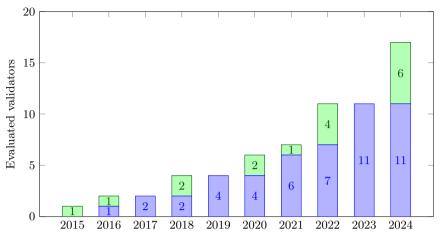

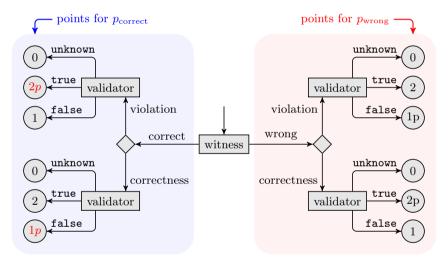

TACAS 2024 also hosted SV-COMP 2024, the 13th International Competition on Software Verification. This event to compare tools evaluated 59 software systems for automatic verification of C and Java programs and 17 software systems for witness validation. The TACAS 2024 proceedings contains a competition report by the SV-Comp chair and organizer. From the 46 actively participating teams, the SV-Comp jury selected 16 short papers that describe the participating verification and validation systems. These 16 short papers are also published in the proceedings and were reviewed by a separate program committee (jury); each of these short papers was assessed by at least four jury members. Two sessions in the TACAS 2024 program were reserved for the presentation of the results: (1) a presentation session with a report by the competition chair and summaries by the developer teams of participating tools, and (2) an open community meeting in the second session.

We would like to thank everyone who helped to make TACAS 2024 successful. We thank the authors for submitting their papers to TACAS 2024. The PC members and additional reviewers did an excellent job in reviewing papers: they provided detailed reports and engaged in the PC discussions. We thank the TACAS steering committee, and especially its chair, Joost-Pieter Katoen, for his valuable advice. We are grateful to the ETAPS steering committee, and in particular its chair, Marieke Huisman, for supporting our changes and suggestions on the TACAS 2024 review process and final

Preface

program. We also acknowledge the invaluable support provided by the EasyChair developers. Lastly, we would like to thank the overall organization team of ETAPS 2024.

April 2024

Bernd Finkbeiner Laura Kovács PC Chairs

Hadar Frenkel Michael Rawson AEC Chairs

Dirk Beyer SV-Comp Chair

# **Organization**

# **Program Committee Chairs**

Bernd Finkbeiner CISPA Helmholtz Center for Information Security,

Germany

Laura Kovács TU Wien, Austria

# **Program Committee**

Alessandro Abate University of Oxford, UK

Erika Ábrahám RWTH Aachen University, Germany

S. Akshay IIT Bombay, India

Elvira Albert Universidad Complutense de Madrid, Spain

Leonardo Alt Ethereum Foundation

Suguman Bansal Georgia Institute of Technology, USA

Nikolaj Bjørner Microsoft Research, USA

Ahmed Bouajjani IRIF, Université Paris Cité, France Claudia Cauli Amazon Web Services, UK Rance Cleaveland University of Maryland, USA Mila Dalla Preda University of Verona, Italy

Rayna Dimitrova CISPA Helmholtz Center for Information Security,

Germany

Madalina Erascu West University of Timişoara, Romania Javier Esparza Technical University of Munich, Germany

Carlo A. Furia USI - Università della Svizzera Italiana, Switzerland

Alberto Griggio Fondazione Bruno Kessler, Italy

Arie Gurfinkel University of Waterloo, Canada

Holger Hermanns Saarland University, Germany

Marijn Heule Carnegie Mellon University, USA

Hossein Hojjat Tehran Institute for Advanced Studies, Iran

Nils Jansen Ruhr-University Bochum, Germany and Radboud

University, Netherlands

Sebastian Junges Radboud University, Netherlands

Amir Kafshdar Goharshady Hong Kong University of Science and Technology,

China

Benjamin Lucien Kaminski Saarland University, Germany and University College

London, UK

Guy Katz The Hebrew University of Jerusalem, Israel

Gergely Kovásznai Eszterházy Károly University, Eger, Hungary

Tamás Kozsik Eötvös Loránd University, Budapest, Hungary

Anthony Widjaja Lin TU Kaiserslautern, Germany

Dorel Lucanu Alexandru Ioan Cuza University, Romania

Filip Maric University of Belgrade, Serbia

Laura Nenzi University of Trieste, Italy

Aina Niemetz Stanford University, USA

Elizabeth Polgreen University of Edinburgh, UK

Kristin Yvonne Rozier Iowa State University, USA

Cesar Sanchez IMDEA Software Institute, Spain

Mark Santolucito Barnard College, USA

Anne-Kathrin Schmuck Max-Planck-Institute for Software Systems, Germany

Sharon Shoham Tel Aviv University, Israel

Mihaela Sighireanu University Paris-Saclay, ENS Paris-Saclay, CNRS,

LMF, France

Martin Suda Czech Technical University in Prague, Czech Republic

Silvia Lizeth Tapia Tarifa University of Oslo, Norway Caterina Urban Inria & ENS—PSL, France

Yakir Vizel Technion, Israel

Tomas Vojnar Brno University of Technology, Czech Republic

Georg Weissenbacher TU Wien, Austria

Sarah Winkler Free University of Bozen-Bolzano, Italy

Ningning Xie University of Toronto and Google Brain, Canada

## **Artifact Evaluation Committee Chairs**

Hadar Frenkel CISPA Helmholtz Center for Information Security,

Germany

Michael Rawson TU Wien, Austria

## **Artifact Evaluation Committee**

Tripti Agarwal University of Utah, USA

Guy Amir The Hebrew University of Jerusalem, Israel

Ahmed Bhayat The University of Manchester, UK

Martin Blicha University of Lugano, Switzerland

Alexander Bork RWTH Aachen University, Germany

Lea Salome Brugger ETH Zürich, Switzerland

Marco Campion Inria & École Normale Supérieure—Université PSL,

France

David Cerna Czech Academy of Sciences Institute of Computer

Science, Czech Republic

Kevin Cheang Amazon Web Services, USA

Md Solimul Chowdhury Carnegie Mellon University, USA

Vlad Craciun BitDefender, UAIC, Romania

Jip J. Dekker Monash University, Australia

Rafael Dewes CISPA Helmholtz Center for Information Security,

Germany

Oyendrila Dobe Michigan State University, USA

Clemens Eisenhofer TU Wien, Austria

Yizhak Elboher The Hebrew University of Jerusalem, Israel Raya Elsaleh The Hebrew University of Jerusalem, Israel

Ferhat Erata Yale University, USA Zafer Esen Uppsala University, Sweden

Aoyang Fang Chinese University of Hong Kong, Shenzhen, China

Pritam Gharat Microsoft Research, India R. Govind Uppsala University, Sweden

Thomas Hader TU Wien, Austria

Philippe Heim CISPA Helmholtz Center for Information Security,

Germany

Maximilian Heisinger Johannes Kepler University Linz, Austria Alejandro Complutense University of Madrid, Spain

Hernández-Cerezo

Singh Hitarth Hong Kong University of Science and Technology,

China

Petra Hozzová TU Wien, Austria Jingmei Hu Amazon, USA

Tobias John University of Oslo, Norway

Martin Jonáš Masaryk University, Czech Republic

Aniruddha Joshi UC Berkeley, USA

Cezary Kaliszyk University of Innsbruck, Austria

Elad Kinsbruner Technion – Israel Institute of Technology, Israel

Åsmund Aqissiaq Arild University of Oslo, Norway

Kløvstad

Paul Kobialka University of Oslo, Norway

Kerim Kochekov Hong Kong University of Science and Technology,

China

Satoshi Kura National Institute of Informatics, Japan

Lorenz Leutgeb Max Planck Institute for Informatics, Germany

Marco Lewis Newcastle University, UK

Jing Liu University of California, Irvine, USA

Yonghui Liu Monash University, Australia

Ioan Vlad Luca West University of Timişoara, Romania

Kaushik Mallik Institute of Science and Technology Austria, Austria

Denis Mazzucato École Normale Supérieure, France

Baoluo Meng GE Global Research, USA

Niklas Metzger CISPA Helmholtz Center for Information Security,

Germany

Srinidhi Nagendra Chennai Mathematical Institute, India

Jens Otten University of Oslo, Norway Jiří Pavela FIT VUT, Czech Republic Bartosz Piotrowski IDEAS NCBR, Poland

Sumanth Prabhu TRDDC, India

Jyoti Prakash University of Passau, Germany Siddharth Priya University of Waterloo, Canada Felipe R. Monteiro Amazon Web Services, USA Idan RefaeliHebrew University of Jerusalem, IsraelSimon RobillardUniversité de Montpellier, France

Clara Rodríguez-Núñez Complutense University of Madrid, Spain

Hans-Jörg Schurr University of Iowa, USA

Tobias Seufert University of Freiburg, Germany Akshatha Shenoy Tata Consultancy Services, India

Boris Shminke Independent Researcher

Julian Siber CISPA Helmholtz Center for Information Security,

Germany

Cristian Simionescu Alexandru Ioan Cuza University, Romania

Abhishek Kr Singh Tel Aviv University, Israel

Alexander Steen University of Greifswald, Germany

Geoff Sutcliffe University of Miami, USA

Joseph Tafese University of Waterloo, Canada

Jinhao Tan University of Hong Kong, China

Abhishek Tiwari University of Passau, Germany

Divyesh Unadkat Synopsys, India

Lena Verscht Saarland University and RWTH Aachen University,

Germany

Christoph Wernhard University of Potsdam, Germany Haoze Wu Stanford University, USA

Jiong Yang National University of Singapore, Singapore

Yi Zhou Carnegie Mellon University, USA

# **SV-COMP Program Committee and Jury**

(more info: https://sv-comp.sosy-lab.org/2024/committee.php, sorted by tool name)

Dirk Beyer (Chair) LMU Munich, Germany

Viktor Malík Brno University of Technology, Czech Republic Zhenbang Chen National University of Defense Technology, China

Lei Bu Nanjing University, China

Marek Chalupa ISTA, Austria

Levente Bajczi Budapest University of Technology and Economics,

Hungary

Daniel Baier LMU Munich, Germany

Thomas Lemberger LMU Munich, Germany

Po-Chun Chien LMU Munich, Germany

Hernán Ponce de León Huawei Dresden Research Center, Germany

Fei He Tsinghua University, China

Fatimah Aljaafari University of Manchester, UK

Franz Brauße University of Manchester, UK

Martin Spiessl LMU Munich, Germany

Falk Howar TU Dortmund, Germany

Simmo Saan University of Tartu, Estonia

Hassan Mousavi University of Tehran, Tehran Institute for Advanced

Studies, Iran

Peter Schrammel University of Sussex and Diffblue, UK

Zaiyu Cheng University of Manchester, UK Gidon Ernst LMU Munich, Germany

Raphaël Monat Inria and University of Lille, France

Jana (Philipp) Berger RWTH Aachen, Germany

Veronika Šoková Brno University of Technology, Czech Republic

Ravindra Metta TCS, India

Vesal Vojdani University of Tartu, Estonia Nils Loose University of Luebeck, Germany

Paulína Ayaziová Masaryk University, Brno, Czech Republic Martin Jonáš Masaryk University, Brno, Czech Republic

Matthias Heizmann

Dominik Klumpp

Frank Schüssele

Daniel Dietsch

Priyanka Darke

University of Freiburg, Germany

Marian Lingsch-Rosenfeld LMU Munich, Germany

# **TACAS Steering Committee**

Dirk Beyer LMU Munich, Germany

Rance Cleaveland University of Maryland, USA

Dana Fisman Ben-Gurion University, Israel

Holger Hermanns Universität des Saarlandes, Germany

Joost-Pieter Katoen (Chair) RWTH Aachen, Germany and Universiteit Twente,

Netherlands

Kim G. Larsen Aalborg University, Denmark

Corina Păsăreanu NASA Ames, USA

# **Additional Reviewers**

Parosh Aziz Abdulla Csaba Biró Guy Amir León Bohn

Andrei Arusoaie Alberto Bombardelli Shaun Azzopardi Wael-Amine Boutglay

Thom Badings Eline Bovy Milan Banković Matías Brizzio Chinmayi Prabhu Baramashetru Gianpiero Cabodi Sebastien Bardin Francesca Cairoli Ludovico Battista Marco Campion Marco Carbone Anna Becchi Lena Becker Martin Ceresa Sidi Mohamed Beillahi Kevin Cheang

Yoav Ben Shimon Md Solimul Chowdhury

### Organization

Alessandro Cimatti Stefan Ciobaca Cayden Codel Jesús Correas Arthur Correnson Florin Craciun

Philipp Czerner

xvi

Tomáš Dacík Luis Miguel Danielsson

Alessandro De Palma

Aldric Degorre

Rafael Dewes

Antonio Di Stasio

Denisa Diaconescu

Crystal Chang Din

Clemens Dubslaff

Serge Durand

Alec Edwards

Neta Elad

Yizhak Elboher

Raya Elsaleh

Constantin Enea

Soroush Farokhnia Csaba Fazekas

Jan Fiedor

Zafer Esen

Emmanuel Fleury James Fox Felix Freiberger Eden Frenkel

Florian Frohn Maris Galesloot Samir Genaim Blaise Genest Pamina Georgiou

Debarghya Ghoshdastidar

Adwait Godbole

Miguel Gomez-Zamalloa

Pablo Gordillo

Felipe Gorostiaga

R. Govind

Orna Grumberg

Roland Guttenberg

Serge Haddad Philippe Heim Martin Helfrich Alejandro Hernández-Cerezo

Ivan Homoliak Dániel Horpácsi Karel Horák Tzu-Han Hsu Attila Házy Miguel Isabel Omri Isac

Omri Isac

Radoslav Ivanov

Predrag Janicic

Chris Johannsen

Eduard Kamburjan

Ambrus Kaposi

Joost-Pieter Katoen

Lutz Klinkenberg

Paul Kobialka

Wietze Koops

Katherine Kosaian

David Kozák

Merlijn Krale

Valentin Krasotin

Loes Kruger

Maximilian Alexander Köhl

Faezeh Labbaf Nham Le

Gabor Kusper

Matthieu Lemerre Ondrej Lengal Dániel Lukács Michael Luttenberger

Viktor Malík Alessio Mansutti Niccolò Marastoni Oliver Markgraf Enrique Martin-Martin

Ruben Martins

Denis Mazzucato Tobias Meggendorfer Roland Meyer Marcel Moosbrugger Federico Mora Alexander Nadel Satya Prakash Nayak Tobias Nießen

Tobias Nießen Andres Noetzli Mohammed Nsaif Robin Ohs Philipp Schröer Emanuel Onica Stefan Schwoon

Michele Pasqua Traian Florin Serbanuta

Andrea Pferscher Daqian Shao

Zoltan Porkolab Xujie Si

Kostiantyn Potomkin Mate Soos

Mathias Preiner Martin Steffen

Siddharth Priya Gregory Stock

Tim Quatmann Sana Stojanović-Đurđević Peter Rakyta Bernardo Subercaseaux

Omer Rappoport Marnix Suilen Jakob Rath Mantas Šimkus Máté Tejfel Rodrigo Raya Adrian Rebola Pardo Simon Thompson Gianluca Redondi Hazem Torfah Joseph Reeves **Dmitriy Traytel** Luke Rickard Marck van der Vegt Andoni Rodriguez Sarat Varanasi

Clara Rodríguez-Núñez Sarat Chandra Varanasi

Adam Rogalewicz Ennio Visconti Enrique Román Calvo Sebastian Wolff Guillermo Román-Díez Yechuan Xia

Vlad Rusu Mitsuharu Yamamoto Krishna S. Raz Yerushalmi Irmak Saglam Emre Yolcu Matteo Sammartino Pian Yu Raimundo Saona Urmeneta Hanwei Zhang Gaia Saveri Zhiwei Zhang Andre Schidler Shufang Zhu Djordje Zikelic Christoph Schmidl Zoltán Zimborás Andreas Schmidt Yannik Schnitzer Dominic Zimmer

# **Contents – Part III**

| Neural Networks                                                                                                                                |            |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Provable Preimage Under-Approximation for Neural Networks                                                                                      | 3          |

| Training for Verification: Increasing Neuron Stability to Scale DNN                                                                            | 2          |

| Verification                                                                                                                                   | 24         |

| NeuroSynt: A Neuro-symbolic Portfolio Solver for Reactive Synthesis                                                                            | 45         |

| Testing and Verification                                                                                                                       |            |

| HALIVER: Deductive Verification and Scheduling Languages Join Forces Lars B. van den Haak, Anton Wijs, Marieke Huisman, and Mark van den Brand | <b>7</b> 1 |

| Gray-Box Fuzzing via Gradient Descent and Boolean Expression Coverage<br>Martin Jonáš, Jan Strejček, Marek Trtík, and Lukáš Urban              | 9(         |

| Fast Symbolic Computation of Bottom SCCs                                                                                                       | 110        |

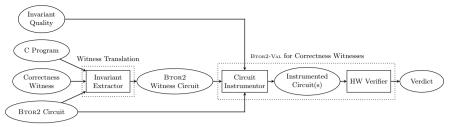

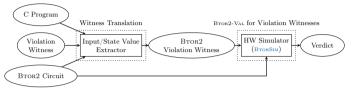

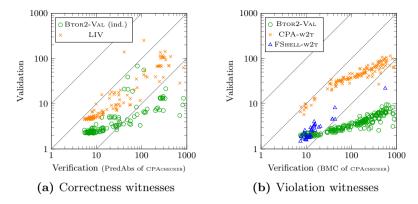

| Btor2-Cert: A Certifying Hardware-Verification Framework Using                                                                                 |            |

| Software Analyzers                                                                                                                             | 129        |

| Games                                                                                                                                          |            |

| Auction-Based Scheduling                                                                                                                       | 153        |

| Most General Winning Secure Equilibria Synthesis in Graph Games Satya Prakash Nayak and Anne-Kathrin Schmuck                                   | 173        |

| On-The-Fly Algorithm for Reachability in Parametric Timed Games                                                    | 194 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Rabin Games and Colourful Universal Trees                                                                          | 213 |

| Concurrency                                                                                                        |     |

| Decidable Verification under Localized Release-Acquire Concurrency Abhishek Kr Singh and Ori Lahav                 | 235 |

| OxiDD: A Safe, Concurrent, Modular, and Performant Decision Diagram Framework in Rust                              | 255 |

| Verification under TSO with an infinite Data Domain                                                                | 276 |

| 13th Competition on Software Verification—SV-Comp 2024                                                             |     |

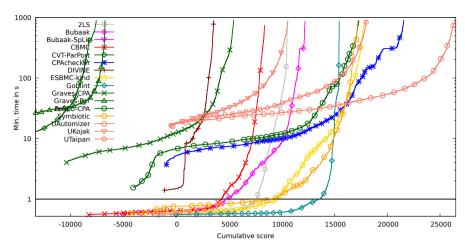

| State of the Art in Software Verification and Witness Validation:  SV-COMP 2024                                    | 299 |

| ConcurrentWitness2Test: Test-Harnessing the Power of Concurrency (Competition Contribution)                        | 330 |

| GOBLINT VALIDATOR: Correctness Witness Validation by Abstract Interpretation (Competition Contribution)            | 335 |

| WITCH 3: Validation of Violation Witnesses in the Witness Format 2.0 (Competition Contribution)                    | 341 |

| AISE: A Symbolic Verifier by Synergizing Abstract Interpretation and Symbolic Execution (Competition Contribution) | 347 |

| Bubaak-SpLit: Split what you cannot verify (Competition contribution)  Marek Chalupa and Cedric Richter                                                                                                                                                      | 353 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CPACHECKER 2.3 with Strategy Selection (Competition Contribution)  Daniel Baier, Dirk Beyer, Po-Chun Chien, Marek Jankola,  Matthias Kettl, Nian-Ze Lee, Thomas Lemberger,  Marian Lingsch-Rosenfeld, Martin Spiessl, Henrik Wachowitz,  and Philipp Wendler | 359 |

| CPV: A Circuit-Based Program Verifier (Competition Contribution)                                                                                                                                                                                             | 365 |

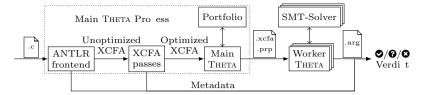

| EmergenTheta: Verification Beyond Abstraction Refinement (Competition Contribution)                                                                                                                                                                          | 371 |

| ESBMC v7.4: Harnessing the Power of Intervals (Competition Contribution)                                                                                                                                                                                     | 376 |

| GOBLINT: Abstract Interpretation for Memory Safety and Termination (Competition Contribution)                                                                                                                                                                | 381 |

| Mopsa-C: Improved Verification for C Programs, Simple Validation of Correctness Witnesses (Competition Contribution)                                                                                                                                         | 387 |

| PROTON: PRObes for Termination Or Not (Competition Contribution) Ravindra Metta, Hrishikesh Karmarkar, Kumar Madhukar, R. Venkatesh, and Supratik Chakraborty                                                                                                | 393 |

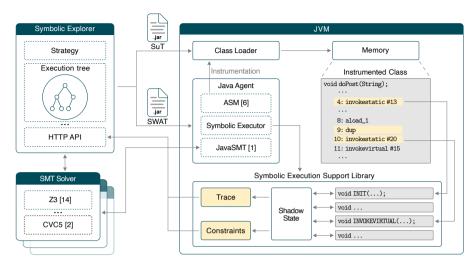

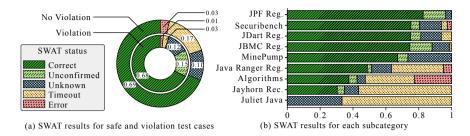

| SWAT: Modular Dynamic Symbolic Execution for Java Applications using Dynamic Instrumentation (Competition Contribution)                                                                                                                                      | 399 |

# xxii Contents - Part III

| Symbiotic 10: Lazy Memory Initialization and Compact Symbolic       |     |

|---------------------------------------------------------------------|-----|

| Execution (Competition Contribution)                                | 406 |

| Martin Jonáš, Kristián Kumor, Jakub Novák, Jindřich Sedláček,       |     |

| Marek Trtík, Lukáš Zaoral, Paulína Ayaziová, and Jan Strejček       |     |

| Theta: Abstraction Based Techniques for Verifying Concurrency       |     |

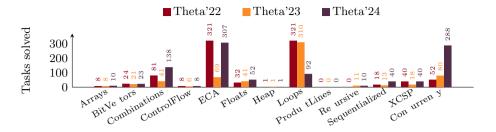

| (Competition Contribution)                                          | 412 |

| Levente Bajczi, Csanád Telbisz, Márk Somorjai, Zsófia Ádám,         |     |

| Mihály Dobos-Kovács, Dániel Szekeres, Milán Mondok,                 |     |

| and Vince Molnár                                                    |     |

| Ultimate Automizer and the Abstraction of Bitwise Operations        |     |

| (Competition Contribution)                                          | 418 |

| Frank Schüssele, Manuel Bentele, Daniel Dietsch, Matthias Heizmann, |     |

| Xinyu Jiang, Dominik Klumpp, and Andreas Podelski                   |     |

| Author Index                                                        | 425 |

|                                                                     |     |

# Provable Preimage Under-Approximation for Neural Networks

Xiyue Zhang<sup>(⊠)</sup>, Benjie Wang, and Marta Kwiatkowska

Department of Computer Science, University of Oxford, Oxford, UK {xiyue.zhang,benjie.wang,marta.kwiatkowska}@cs.ox.ac.uk

Abstract. Neural network verification mainly focuses on local robustness properties, which can be checked by bounding the image (set of outputs) of a given input set. However, often it is important to know whether a given property holds globally for the input domain, and if not then for what proportion of the input the property is true. To analyze such properties requires computing preimage abstractions of neural networks. In this work, we propose an efficient anytime algorithm for generating symbolic under-approximations of the preimage of any polyhedron output set for neural networks. Our algorithm combines a novel technique for cheaply computing polytope preimage under-approximations using linear relaxation, with a carefully-designed refinement procedure that iteratively partitions the input region into subregions using input and ReLU splitting in order to improve the approximation. Empirically, we validate the efficacy of our method across a range of domains, including a high-dimensional MNIST classification task beyond the reach of existing preimage computation methods. Finally, as use cases, we showcase the application to quantitative verification and robustness analysis. We present a sound and complete algorithm for the former, which exploits our disjoint union of polytopes representation to provide formal guarantees. For the latter, we find that our method can provide useful quantitative information even when standard verifiers cannot verify a robustness property.

### 1 Introduction

Despite the remarkable empirical success of neural networks, guaranteeing their correctness, especially when using them as decision-making components in safety-critical autonomous systems [7, 13, 43], is an important and challenging task. Towards this aim, various approaches have been developed for the verification of neural networks, with extensive effort devoted to local robustness verification [20, 22, 44, 11, 35, 32, 40, 41, 36]. While local robustness verification focuses on deciding the absence of adversarial examples within an  $\epsilon$ -perturbation neighbourhood, an alternative approach for neural network analysis is to construct the preimage of its predictions [27, 15]. Given a set of outputs, the preimage is defined as the set of all inputs mapped by the neural network to that output set. By characterizing the preimage symbolically in an abstract representation, e.g.,

<sup>©</sup> The Author(s) 2024

### X. Zhang et al.

4

polyhedra, one can perform more complex analysis for a wider class of properties beyond local robustness, such as computing the *proportion* of inputs satisfying a property (quantitative verification) even if standard robustness verification fails.

Exact preimage generation [27] is intractable, taking time exponential in the number of neurons in a network; thus approximations are necessary. Unfortunately, existing methods are limited in their applicability. The inverse abstraction method in [15] bypasses the intractability of exact preimage generation by leveraging symbolic interpolants [14,2] for abstraction of neural network layers. However, due to the complexity of interpolation, the time to compute the abstraction also scales exponentially with the number of neurons in hidden layers. A concurrent work [23] proposed an input bounding algorithm targeting backward reachability analysis for control policies and out-of-distribution (OOD) detection in low-dimensional domains. Their method produces a preimage overapproximation, which cannot be used for quantitative verification. Therefore, more efficient and flexible computation methods for (symbolic abstraction of) preimages of neural networks are needed.

The main contribution of this paper is a scalable method for preimage approximation, which can be used for a variety of robustness analysis tasks. More specifically, we propose an efficient anytime algorithm for generating symbolic under-approximations of the preimage of piecewise linear neural networks as a union of disjoint polytopes. The algorithm computes a sound preimage underapproximation leveraging linear relaxation based perturbation analysis (LiRPA) [40, 41, 32], applied backwards from a polyhedron output set. It iteratively refines the preimage approximation by adding input and/or intermediate (ReLU) splitting (hyper)planes to partition the input region into disjoint subregions, which can be approximated independently in parallel in a divide-and-conquer approach. The refinement scheme uses a novel differential objective to optimize the quality (volume) of the polytope subregions. We also show that our method can be generalized to generate preimage over-approximations. We illustrate the application of our method to quantitative verification, input bounding for control tasks, and robustness analysis against adversarial and patch attacks. Finally, we conduct an empirical analysis on a range of control and computer vision tasks, showing significant gains in efficiency compared to exact preimage generation methods and scalability to high-input-dimensional tasks compared to existing preimage approximation methods.

For space reasons, proofs and additional technical details have been moved to Appendix of the full version of the paper [45].

# 2 Preliminaries

We use  $f: \mathbb{R}^d \to \mathbb{R}^m$  to denote a feedforward neural network. For layer i, we use  $\mathbf{W}^{(i)}$  to denote the weight matrix,  $\mathbf{b}^{(i)}$  the bias,  $h^{(i)}$  the pre-activation neurons, and  $a^{(i)}$  the post-activation neurons, such that we have  $h^{(i)} = \mathbf{W}^{(i)} a^{(i-1)} + \mathbf{b}^{(i)}$ . In this paper, we focus on ReLU neural networks with  $a^{(i)}(x) = ReLU(h^{(i)}(x))$ ,

Fig. 1: Linear bounding functions for inactive, active, unstable ReLU neurons.

where ReLU(h) := max(h, 0) is applied element-wise. However, our method can be generalized to other activation functions bounded by linear relaxation [44].

Linear Relaxation of Neural Networks. Nonlinear activation functions lead to the NP-completeness of the neural network verification problem [22]. To address such intractability, linear relaxation is often used to transform the nonconvex constraints into linear programs. As shown in Figure 1, given concrete lower and upper bounds  $\mathbf{l}^{(i)} \leq h^{(i)}(x) \leq \mathbf{u}^{(i)}$  on the pre-activation values of layer i, there are three cases to consider. In the inactive  $(u_j^{(i)} \leq 0)$  and active  $(l_j^{(i)} \geq 0)$  cases, the post-activation neurons  $a_j^{(i)}(x)$  are linear functions  $a_j^{(i)}(x) = 0$  and  $a_j^{(i)}(x) = h_j^{(i)}(x)$  respectively. In the unstable case,  $a_j^{(i)}(x)$  can be bounded by  $\alpha_j^{(i)}h_j^{(i)}(x) \leq a_j^{(i)}(x) \leq -\frac{u_j^{(i)}l_j^{(i)}}{u_j^{(i)}-l_j^{(i)}} + \frac{u_j^{(i)}}{u_j^{(i)}-l_j^{(i)}}h_j^{(i)}(x)$ , where  $\alpha_j^{(i)}$  is a configurable parameter that produces a valid lower bound for any value in [0,1]. Linear bounds can also be obtained for other non-piecewise linear activation functions [44].

Linear relaxation can be used to compute linear upper and lower bounds of the form  $\underline{\mathbf{A}}x + \underline{\mathbf{b}} \leq f(x) \leq \overline{\mathbf{A}}x + \overline{\mathbf{b}}$  on the output of a neural network, for a given bounded input region  $\mathcal{C}$ . These methods are known as linear relaxation based perturbation analysis (LiRPA) algorithms [40, 41, 32]. In particular, backward-mode LiRPA computes linear bounds on f by propagating linear bounding functions backward from the output, layer-by-layer, to the input layer.

Polytope Representations. Given an Euclidean space  $\mathbb{R}^d$ , a polyhedron T is defined to be the intersection of a set of half spaces. More formally, suppose we have a set of linear constraints defined by  $\psi_i(x) := c_i^T x + d_i \geq 0$  for i = 1, ...K, where  $c_i \in \mathbb{R}^d$ ,  $d_i \in \mathbb{R}$  are constants, and  $x = x_1, ..., x_d$  is a set of variables. Then a polyhedron is defined as  $T = \{x \in \mathbb{R}^d | \bigwedge_{i=1}^K \psi_i(x) \}$ , where T consists of all values of x satisfying the first-order logic (FOL) formula  $\alpha(x) := \bigwedge_{i=1}^K \psi_i(x)$ . We use the term polytope to refer to a bounded polyhedron, that is, a polyhedron T such that  $\exists R \in \mathbb{R}^{>0} : \forall x_1, x_2 \in T, ||x_1 - x_2||_2 \leq R$  holds. The abstract domain of polyhedra [32, 6, 8] has been widely used for the verification of neural networks and computer programs. An important type of polytope is the hyperrectangle (box), which is a polytope defined by a closed and bounded interval  $[\underline{x_i}, \overline{x_i}]$  for each dimension, where  $\underline{x_i}, \overline{x_i} \in \mathbb{Q}$ . More formally, using the linear constraints  $\phi_i := (x_i \geq \underline{x_i}) \land (x_i \leq \overline{x_i})$  for each dimension, the hyperrectangle takes the form  $\mathcal{C} = \{x \in \mathbb{R}^d | x \models \bigwedge_{i=1}^d \phi_i\}$ .

# 3 Problem Formulation

# 3.1 Preimage Approximation

In this work, we are interested in the problem of computing preimages for neural networks. Given a subset  $O \subset \mathbb{R}^m$  of the codomain, the preimage of a function  $f: \mathbb{R}^d \to \mathbb{R}^m$  is defined to be the set of all inputs  $x \in \mathbb{R}^d$  that are mapped to an element of O by f. For neural networks in particular, the input is typically restricted to some bounded input region  $\mathcal{C} \subset \mathbb{R}^d$ . In this work, we restrict the output set O to be a polyhedron, and the input set  $\mathcal{C}$  to be an axis-aligned hyperrectangle region  $\mathcal{C} \subset \mathbb{R}^d$ , as these are commonly used in neural network verification. We now define the notion of a restricted preimage:

**Definition 1 (Restricted Preimage).** Given a neural network  $f: \mathbb{R}^d \to \mathbb{R}^m$ , and an input set  $\mathcal{C} \subset \mathbb{R}^d$ , the restricted preimage of an output set  $O \subset \mathbb{R}^m$  is defined to be the set  $f_{\mathcal{C}}^{-1}(O) := \{x \in \mathbb{R}^d | f(x) \in O \land x \in \mathcal{C}\}.$

Example 1. To illustrate our problem formulation and approach, we introduce a vehicle parking task [3] as a running example. In this task, there are four parking lots, located in each quadrant of a  $2 \times 2$  grid  $[0,2]^2$ , and a neural network with two hidden layers of 10 ReLU neurons  $f: \mathbb{R}^2 \to \mathbb{R}^4$  is trained to classify which parking lot an input point belongs to. To analyze the behaviour of the neural network in the input region  $[0,1] \times [0,1]$  corresponding to parking lot 1, we set  $\mathcal{C} = \{x \in \mathbb{R}^2 | (0 \le x_1 \le 1) \land (0 \le x_2 \le 1) \}$ . Then the restricted preimage  $f_{\mathcal{C}}^{-1}(O)$  of the set  $O = \{y \in \mathbb{R}^4 | \bigwedge_{i \in \{2,3,4\}} y_1 - y_i \ge 0\}$  is the subspace of the region  $[0,1] \times [0,1]$  that is labelled as parking lot 1 by the network.

We focus on provable approximations of the preimage. Given a first-order formula A,  $\alpha$  is an under-approximation (resp. over-approximation) of A if it holds that  $\forall x.\alpha(x) \implies A(x)$  (resp.  $\forall x.A(x) \implies \alpha(x)$ ). In our context, the restricted preimage is defined by the formula  $A(x) = (f(x) \in O) \land (x \in C)$ , and we restrict to approximations  $\alpha$  that take the form of a disjoint union of polytopes (DUP). The goal of our method is to generate a DUP approximation  $\mathcal{T}$  that is as tight as possible; that is, to maximize the volume  $\operatorname{vol}(\mathcal{T})$  of an under-approximation, or minimize the volume  $\operatorname{vol}(\mathcal{T})$  of an over-approximation.

**Definition 2 (Disjoint Union of Polytopes).** A disjoint union of polytopes (DUP) is a FOL formula  $\alpha$  of the form  $\alpha(x) := \bigvee_{i=1}^{D} \alpha_i(x)$ , where each  $\alpha_i$  is a polytope formula (conjunction of a finite set of linear half-space constraints), with the property that  $\alpha_i \wedge \alpha_j$  is unsatisfiable for any  $i \neq j$ .

# 3.2 Quantitative Properties

One of the most important verification problems for neural networks is that of proving guarantees on the output of a network for a given input set [18, 19, 30]. This is often expressed as a property of the form (I, O) such that  $\forall x \in I \implies f(x) \in O$ . We can generalize this to quantitative properties:

**Definition 3 (Quantitative Property).** Given a neural network  $f: \mathbb{R}^d \to \mathbb{R}^m$ , a measurable input set with non-zero measure (volume)  $I \subseteq \mathbb{R}^d$ , a measurable output set  $O \subseteq \mathbb{R}^m$ , and a rational proportion  $p \in [0,1]$  we say that the neural network satisfies the property (I,O,p) if  $\frac{\operatorname{vol}(f_I^{-1}(O))}{\operatorname{vol}(I)} \geq p$ .

Neural network verification algorithms [25] can be divided into two categories: sound, which always return correct results, and complete, guaranteed to reach a conclusion on any verification query. We now define soundness and completeness of verification algorithms for quantitative properties.

**Definition 4 (Soundness).** A verification algorithm QV is sound if, whenever QV outputs True, the property (I, O, p) holds.

**Definition 5 (Completeness).** A verification algorithm QV is complete if (i) QV never returns Unknown, and (ii) whenever QV outputs False, the property (I, O, p) does not hold.

If the property (I,O) holds, then the quantitative property (I,O,1) holds, while quantitative properties for  $0 \le p < 1$  provide more information when (I,O) does not hold. Most neural network verification methods produce approximations of the *image* of I in the output space, which cannot be used to verify quantitative properties. Preimage *over-approximations* include false regions, thereby not applicable for quantitative verification. In contrast, preimage *under-approximations* provide a lower bound on the volume of the preimage, allowing us to soundly verify quantitative properties.

# 4 Methodology

Overview. In this section we present the main components of our methodology. Firstly, in Section 4.1, we show how to cheaply and soundly under-approximate the (restricted) preimage with a single polytope, using linear relaxation methods (Algorithm 2). Secondly, in Section 4.2, we propose a novel differentiable objective to optimize the quality (volume) of the polytope under-approximation. Thirdly, in Section 4.3, we propose a refinement scheme that improves the approximation by partitioning a (sub)region into subregions with splitting planes, with each subregion then being under-approximated more accurately. The main contribution of this paper (Algorithm 1) integrates these three components and is described in Section 4.4. Finally, in Section 4.5, we apply our method to quantitative verification (Algorithm 3) and prove its soundness and completeness.

# 4.1 Polytope Under-Approximation via Linear Relaxation

We first show how to adapt linear relaxation techniques to efficiently generate valid under-approximations to the restricted preimage for a given input region  $\mathcal{C}$ .

<sup>&</sup>lt;sup>1</sup> In particular, the restricted preimage of a polyhedron under a neural network is Lebesgue measurable since polyhedra (intersection of a finite set of half-spaces) are Borel measurable and NNs are continuous functions.

# **Algorithm 1:** Preimage Approximation

```

Input: Neural network f, Input region C, Output region O, Volume threshold

v, Maximum iterations R, Boolean SplitOnInput

Output: Disjoint union of polytopes \mathcal{T}

1 T \leftarrow \text{GenUnderApprox}(\mathcal{C}, O);

// Initial preimage polytope

\mathbf{2} \ \widehat{\text{vol}}_T, \widehat{\text{vol}}_{f_{\mathcal{C}}^{-1}(O)} \leftarrow \text{EstimateVol}(T), \ \text{EstimateVol}(f_{\mathcal{C}}^{-1}(O)) \ ;

3 Dom \leftarrow \{(\mathcal{C}, T, \widehat{\text{vol}}_{f_c^{-1}(O)} - \widehat{\text{vol}}_T)\};

// Priority queue

// \mathcal{T}_{\mathrm{Dom}} is the union of polytopes in Dom

4 while EstimateVol(\mathcal{T}_{Dom}) < v and Iterations \leq R do

C_{\text{sub}}, T, \text{Priority} \leftarrow \text{Pop}(\text{Dom}) \; ; \quad // \; \text{Subregion with highest priority}

5

6

if SplitOnInput then

id \leftarrow \text{SelectInputFeature}(\text{Feature}_I);

// Feature_I is the set of

7

input features/dimensions

else

8

id \leftarrow \text{SelectReLUNode}(\text{Node}_Z); // Node<sub>Z</sub> is the set of unstable

9

ReLU nodes

[\mathcal{C}^l_{sub}, \mathcal{C}^u_{sub}] \leftarrow \mathrm{SplitOnNode}(\mathcal{C}_{sub}, \mathit{id}); \qquad \textit{//} \; \; \mathsf{Split} \; \; \mathsf{on} \; \; \mathsf{the} \; \; \mathsf{selected} \; \; \mathsf{node}

10

[T^l, T^u] \leftarrow \text{GenUnderApprox}([\mathcal{C}^l_{sub}, \mathcal{C}^u_{sub}], O) ;

// Generate preimage

11

[\widehat{\text{vol}}_{T^l}, \widehat{\text{vol}}_{T^u}] \leftarrow \text{EstimateVol}([T^l, T^u]);

12

\widehat{\text{vol}}_{f_{\mathcal{C}^{l}_{sub}}^{-1}(O)}, \widehat{\text{vol}}_{f_{\mathcal{C}^{u}_{sub}}^{-1}(O)} \leftarrow \text{EstimateVol}(f_{\mathcal{C}^{l}_{sub}}^{-1}(O)), \text{EstimateVol}(f_{\mathcal{C}^{u}_{sub}}^{-1}(O)) \; ;

13

\operatorname{Dom} \overset{\text{\tiny sub}}{\leftarrow} \operatorname{Dom} \, \cup \, \big\{ \big( \mathcal{C}^l_{sub}, T^l, \widehat{\operatorname{vol}}_{f^{-1}_{\mathcal{C}^l}, (O)} - \widehat{\operatorname{vol}}_{T^l} \big) \big\} \, \, \cup \,

14

\{(\mathcal{C}_{sub}^u, T^u, \widehat{\operatorname{vol}}_{f_{\mathcal{C}^u}^{-1}, (O)} - \widehat{\operatorname{vol}}_{T^u})\};

// Disjoint polytope

15 return \mathcal{T}_{\mathrm{Dom}}

```

Recall that LiRPA methods enable us to obtain linear lower and upper bounds on the output of a neural network f, that is,  $\underline{\mathbf{A}}x + \underline{\mathbf{b}} \leq f(x) \leq \overline{\mathbf{A}}x + \overline{\mathbf{b}}$ , where the linear coefficients depend on the input region  $\mathcal{C}$ .

Now, suppose that we are interested in computing an under-approximation to the restricted preimage, given the input hyperrectangle  $\mathcal{C}=\{x\in\mathbb{R}^d|x\models\bigwedge_{i=1}^d\phi_i\}$ , and the output polytope specified using the half-space constraints  $\psi_i(y)=(c_i^Ty+d_i\geq 0)$  for i=1,...,K over the output space. Given a constraint  $\psi_i$ , we append an additional linear layer at the end of the network f, which maps  $y\mapsto c_i^Ty+d_i$ , such that the function  $g_i:\mathbb{R}^d\to\mathbb{R}$  represented by the new network is  $g_i(x)=c_i^Tf(x)+d_i$ . Then, applying LiRPA bounding to each  $g_i$ , we obtain lower bounds  $\underline{g_i}(x)=\underline{a_i}^Tx+\underline{b_i}$  for each i, such that  $\underline{g_i}(x)\geq 0\Longrightarrow g_i(x)\geq 0$  for  $x\in\mathcal{C}$ . Notice that, for each i=1,...,K,  $\underline{a_i}^Tx+\underline{b_i}\geq 0$  is a half-space constraint in the input space. We conjoin these constraints, along with the restriction to the input region  $\mathcal{C}$ , to obtain a polytope  $T_{\mathcal{C}}(O):=\{x|\bigwedge_{i=1}^K(\underline{g_i}(x)\geq 0)\wedge\bigwedge_{i=1}^d\phi_i(x)\}$ .

**Proposition 1.**  $T_{\mathcal{C}}(O)$  is an under-approximation to the restricted preimage  $f_{\mathcal{C}}^{-1}(O)$ .

# **Algorithm 2:** GenUnderApprox

```

Input: List of subregions \mathcal{C}, Output set O, number of samples N

Output: List of polytopes \mathbf{T}

1 \mathbf{T} = [];

2 for subregion \mathcal{C}_{sub} \in \mathcal{C} // Parallel over subregions

3 do

4 \left[\underline{g_1}(x, \boldsymbol{\alpha}_1), ..., \underline{g_K}(x, \boldsymbol{\alpha}_K)\right] \leftarrow \text{LinearLowerBound}(\mathcal{C}_{sub}, O);

5 x_1, ..., x_N \leftarrow \text{Sample}(\mathcal{C}_{sub}, N);

6 \text{Loss}(\boldsymbol{\alpha}_1, ..., \boldsymbol{\alpha}_K) \leftarrow -\sum_{j=1,...,N} \sigma(-\text{LSE}(-\underline{g_1}(x_j, \boldsymbol{\alpha}_1), ..., -\underline{g_K}(x_j, \boldsymbol{\alpha}_K));

7 \boldsymbol{\alpha}_1^*, ..., \boldsymbol{\alpha}_K^* \leftarrow \text{Optimize}(\text{Loss}(\boldsymbol{\alpha}_1, ..., \boldsymbol{\alpha}_K));

8 \mathbf{T} = \text{Append}(\mathbf{T}, [\underline{g_1}(x, \boldsymbol{\alpha}_1^*) \geq 0, ..., \underline{g_K}(x, \boldsymbol{\alpha}_K^*) \geq 0, x \in \mathcal{C}_{sub}])

9 \mathbf{return} \ T

```

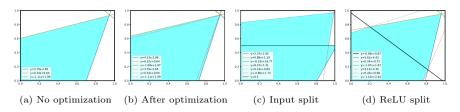

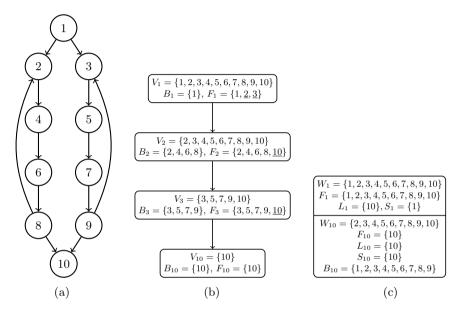

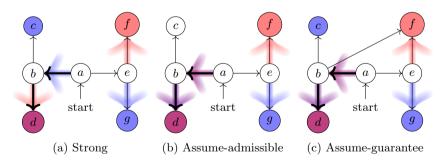

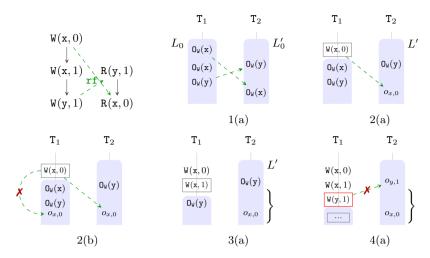

Example 2. Returning to Example 1, the output constraints (for i=2,3,4) are given by  $\psi_i=(y_1-y_i\geq 0)=(c_i^Ty+d_i\geq 0)$ , where  $c_i:=e_1-e_i$  (where  $e_i$  is the  $i^{\text{th}}$  standard basis vector) and  $d_i:=0$ . Applying LiRPA bounding, we obtain the linear lower bounds  $\underline{g_2}(x)=-3.79x_1+x_2+2.65\geq 0; \underline{g_3}(x)=0.34x_1-x_2-0.60\geq 0; \underline{g_4}(x)=-1.11x_1-x_2+1.99\geq 0$  for each constraint. The intersection of these constraints, shown in Figure 2a, represents the region where any input is guaranteed to satisfy the output constraints.

We generate the linear bounds in parallel over the output polyhedron constraints i = 1, ..., K using the backward mode LiRPA [44], and store the resulting input polytope  $T_{\mathcal{C}}(O)$  as a list of constraints. This highly efficient procedure is used as a sub-routine LinearLowerBound when generating a preimage underapproximation as a polytope union using Algorithm 2 (Line 4).

# 4.2 Local Optimization

One of the key components behind the effectiveness of LiRPA-based bounds is the ability to efficiently improve the tightness of the bounding function by optimizing the relaxation parameters  $\alpha$ , via projected gradient descent. In the context of local robustness verification, the goal is to optimize the concrete lower or upper bounds over the (sub)region  $\mathcal{C}$  [40], i.e.,  $\min_{x \in \mathcal{C}} \underline{\mathbf{A}}(\alpha)x + \underline{\mathbf{b}}(\alpha)$ , where we explicitly note the dependence of the linear coefficients on  $\alpha$ . In our case, we are instead interested in optimizing  $\alpha$  to refine the polytope under-approximation, that is, increase its volume. Unfortunately, computing the volume of a polytope exactly is a computationally expensive task, and requires specialized tools [12] that do not permit easy optimization with respect to the  $\alpha$  parameters.

To address this challenge, we propose to use statistical estimation. In particular, we sample N points  $x_1, ..., x_N$  uniformly from the input domain  $\mathcal{C}$  then employ Monte Carlo estimation for the volume of the polytope approximation:

$$\widehat{\text{vol}}(T_{\mathcal{C},\alpha}(O)) = \frac{\sum_{i=1}^{N} \mathbb{1}_{x_i \in T_{\mathcal{C},\alpha}(O)}}{N} \times \text{vol}(\mathcal{C})$$

(1)

where we highlight the dependence of  $T_{\mathcal{C}}(O) = \{x | \bigwedge_{i=1}^K \underline{g_i}(x, \alpha_i) \geq 0 \land \bigwedge_{i=1}^d \phi_i(x) \}$  on  $\alpha = (\alpha_1, ..., \alpha_K)$ , and  $\alpha_i$  are the  $\alpha$ -parameters for the linear relaxation of the neural network  $g_i$  corresponding to the  $i^{\text{th}}$  half-space constraint in O. However, this is still non-differentiable w.r.t.  $\alpha$  due to the identity function. We now show how to derive a differentiable relaxation which is amenable to gradient-based optimization:

$$\begin{split} \widehat{\operatorname{vol}}(T_{\mathcal{C}, \boldsymbol{\alpha}}(O)) &= \frac{\operatorname{vol}(\mathcal{C})}{N} \sum_{j=1}^{N} \mathbb{1}_{x_j \in T_{\mathcal{C}, \boldsymbol{\alpha}}(O)} = \frac{\operatorname{vol}(\mathcal{C})}{N} \sum_{j=1}^{N} \mathbb{1}_{\min_{i=1, \dots K} \underline{g_i}(x_j, \boldsymbol{\alpha}_i) \geq 0} \\ &\approx \frac{\operatorname{vol}(\mathcal{C})}{N} \sum_{j=1}^{N} \sigma \left( \min_{i=1, \dots K} \underline{g_i}(x_j, \boldsymbol{\alpha}_i) \right) \\ &\approx \frac{\operatorname{vol}(\mathcal{C})}{N} \sum_{j=1}^{N} \sigma \left( -\operatorname{LSE}(-\underline{g_1}(x_j, \boldsymbol{\alpha}_1), \dots, -\underline{g_K}(x_j, \boldsymbol{\alpha}_K)) \right) \end{split}$$

The second equality follows from the definition of the polytope  $T_{\mathcal{C},\alpha}(O)$ ; namely that a point is in the polytope if it satisfies  $g_i(x_j,\alpha_i) \geq 0$  for all i=1,...,K, or equivalently,  $\min_{i=1,...K} \underline{g_i}(x_j,\alpha_i) \geq 0$ . After this, we approximate the identity function using a sigmoid relaxation, where  $\sigma(y) \coloneqq \frac{1}{1+e^{-y}}$ , as is commonly done in machine learning to define classification losses. Finally, we approximate the minimum over specifications using the log-sum-exp (LSE) function. The log-sum-exp function is defined by  $LSE(y_1,...,y_K) \coloneqq \log(\sum_{i=1,...,K} e^{y_i})$ , and is a differentiable approximation to the maximum function; we employ it to approximate the minimization by adding the appropriate sign changes. The final expression is now a differentiable function of  $\alpha$ . We employ this as the loss function in Algorithm 2 (Line 6) for generating a polytope approximation, and optimize volume using projected gradient descent.

Example 3. We revisit the vehicle parking problem in Example 1. Figure 2a and 2b show the computed under-approximations before and after local optimization. We can see that the bounding planes for all three specifications are optimized, which effectively improves the approximation quality.

# 4.3 Global Branching and Refinement

As LiRPA performs crude linear relaxation, the resulting bounds can be quite loose even with  $\alpha$ -optimization, meaning that the polytope approximation  $T_{\mathcal{C}}(O)$  is unlikely to constitute a tight under-approximation to the preimage. To address this challenge, we employ a divide-and-conquer approach that iteratively refines our under-approximation of the preimage. Starting from the initial region  $\mathcal{C}$  represented at the root, our method generates a tree by iteratively partitioning a subregion  $\mathcal{C}_{sub}$  represented at a leaf node into two smaller subregions  $\mathcal{C}_{sub}^l$ ,  $\mathcal{C}_{sub}^u$ , which are then attached as children to that leaf node. In this way, the subregions represented by all leaves of the tree are disjoint, such that their union is the initial region  $\mathcal{C}$ .

For each leaf subregion  $C_{sub}$  we compute, using LiRPA bounds (Line 4, Algorithm 2), an associated polytope that under-approximates the preimage in  $C_{sub}$ . Thus, irrespective of the number of refinements performed, the union of the polytopes corresponding to all leaves forms an *anytime* DUP under-approximation  $\mathcal{T}$  to the preimage in the original region  $\mathcal{C}$ . The process of refining the subregions continues until an appropriate termination criterion is met.

Unfortunately, even with a moderate number of input dimensions or unstable ReLU nodes, naïvely splitting along all input- or ReLU-planes quickly becomes computationally infeasible. For example, splitting a d-dimensional hyperrectangle using bisections along each dimension results in  $2^d$  subdomains to approximate. It thus becomes crucial to identify the subregion splits that have the most impact on the quality of the under-approximation. Another important aspect is how to prioritize which leaf subregion to split. We describe these in turn.

**Subregion Selection.** Searching through all leaf subregions at each iteration is computationally too expensive. Thus, we propose a subregion selection strategy that prioritizes splitting subregions according to (an estimate of) the difference in volume between the exact preimage  $f_{\mathcal{C}_{sub}}^{-1}(O)$  and the (already computed) polytope approximation  $T_{\mathcal{C}_{sub}}(O)$  on that subdomain, that is:

$$Priority(\mathcal{C}_{sub}) = vol(f_{\mathcal{C}_{sub}}^{-1}(O)) - vol(T_{\mathcal{C}_{sub}}(O))$$

(2)

which measures the gap between the polytope under-approximation and the optimal approximation, namely, the preimage itself.

Suppose that a particular leaf subdomain attains the maximum of this metric among all leaves, and we partition it into two subregions  $C^l_{sub}$ ,  $C^u_{sub}$ , which we approximate with polytopes  $T_{C^l_{sub}}(O)$ ,  $T_{C^u_{sub}}(O)$ . As tighter intermediate concrete bounds, and thus linear bounding functions, can be computed on the partitioned subregions, the polytope approximation on each subregion will be refined compared with the single polytope restricted to that subregion.

**Proposition 2.** Given any subregion  $C_{sub}$  with polytope approximation  $T_{C_{sub}}(O)$ , and its children  $C_{sub}^l$ ,  $C_{sub}^u$  with polytope approximations  $T_{C_{sub}^l}(O)$ ,  $T_{C_{sub}^u}(O)$  respectively, it holds that:

$$T_{\mathcal{C}_{sub}^{l}}(O) \cup T_{\mathcal{C}_{sub}^{u}}(O) \supseteq T_{\mathcal{C}_{sub}}(O) \tag{3}$$

Corollary 1. In each refinement iteration, the volume of the polytope approximation  $\mathcal{T}_{Dom}$  does not decrease.

Since computing the volumes in Equation 2 is intractable, we sample N points  $x_1,...,x_N$  uniformly from the subdomain  $\mathcal{C}_{sub}$  and employ Monte Carlo estimation to estimate the volume for both the preimage and the polytope approximation using the same set of samples, i.e.,  $\widehat{\text{vol}}(f_{\mathcal{C}_{sub}}^{-1}(O)) = \text{vol}(\mathcal{C}_{sub}) \times \frac{1}{N} \sum_{i=1}^{N} \mathbbm{1}_{x_i \in f_{\mathcal{C}_{sub}}^{-1}(O)}$ , and  $\widehat{\text{vol}}(T_{\mathcal{C}_{sub}}(O)) = \text{vol}(\mathcal{C}_{sub}) \times \frac{1}{N} \sum_{i=1}^{N} \mathbbm{1}_{x_i \in T_{\mathcal{C}_{sub}}(O)}$ . We

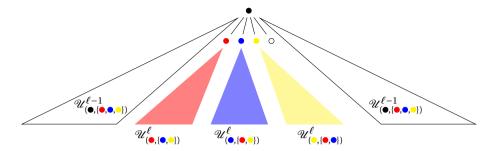

Fig. 2: Refinement and optimization for preimage approximation.

stress that volume estimation is only used to prioritize subregion selection, and does not affect the soundness of our method.

Input Splitting. Given a subregion (hyperrectangle) defined by lower and upper bounds  $x_i \in [\underline{x}_i, \overline{x}_i]$  for all dimensions i=1,...,d, input splitting partitions it into two subregions by cutting along some feature i. This splitting procedure will produce two subregions which are similar to the original subregion, but have updated bounds  $[\underline{x}_i, \frac{x_i + \overline{x}_i}{2}], [\frac{x_i + \overline{x}_i}{2}, \overline{x}_i]$  for feature i instead. In order to determine which feature/dimension to split on, we propose a greedy strategy. Specifically, for each feature, we generate a pair of polytopes for the two subregions resulting from the split, and choose the feature that results in the greatest total volume of the polytope pair. In practice, another commonly-adopted splitting heuristic is to select the dimension with the longest edge [10], that is, to select feature i with the largest range:  $\arg\max_i(\overline{x}_i - \underline{x}_i)$ . However, this method falls short in periteration approximation volume improvement compared to our greedy strategy.

Example 4. We revisit the vehicle parking problem in Example 1. Figure 2b shows the polytope under-approximation computed on the input region  $\mathcal{C}$  before refinement, where each solid line represents the bounding plane for each output specification  $(y_1 - y_i \ge 0)$ . Figure 2c depicts the refined approximation by splitting the input region along the vertical axis, where the solid and dashed lines represent the bounding planes for the two resulting subregions. It can be seen that the total volume of the under-approximation has improved significantly.

Intermediate ReLU Splitting. Refinement through splitting on input features is adequate for low-dimensional input problems such as reinforcement learning agents. However, it may be infeasible to generate sufficiently fine subregions for high-dimensional domains. We thus propose an algorithm for ReLU neural networks that uses intermediate ReLU splitting for preimage refinement. After determining a subregion for refinement, we partition the subregion based upon the pre-activation value of an intermediate unstable neuron  $z_j^{(i)} = 0$ . As a result, the original subregion  $C_{sub}$  is split into two new subregions  $C_{z_j^{(i)}}^+ = \{x \in C_{sub} \mid z_j^{(i)} = h_j^{(i)}(x) < 0\}$ .

To obtain a polytope under-approximation, we can utilize linear lower/upper bounds on  $h_i^{(i)}(x)$  as an approximation to the subregion boundary.

In this procedure, the order of splitting unstable ReLU neurons can greatly influence the refinement quality and efficiency. Existing heuristic methods of ReLU prioritization select ReLU nodes that lead to greater improvement in the final bound (maximum or minimum value) of the neuron network on the input domain [10], i.e.  $\min_{x \in \mathcal{C}} \underline{f}(x)$ . However, these ReLU prioritization methods are not effective for preimage analysis, because our objective is instead to refine the overall preimage approximation. We thus propose a heuristic method to prioritize unstable ReLU nodes for preimage refinement. Specifically, we compute (an estimate of) the volume difference between the split subregions  $|vol(\mathcal{C}^+_{z_j^{(i)}}) - \mathcal{C}^+_{z_j^{(i)}}|$

$\operatorname{vol}(\mathcal{C}_{z_j^{(i)}})|$ , using a single forward pass for a set of sampled datapoints from the input domain; note that this is bounded above by the total subregion volume  $\operatorname{vol}(\mathcal{C}_{sub})$ . We then propose to select the ReLU node that minimizes this difference. Intuitively, this choice results in balanced subdomains after splitting.

Another advantage of ReLU splitting is that we can replace the unstable neuron bound  $\underline{c}h_j^{(i)}(x) + \underline{d} \leq a_j^{(i)}(x) \leq \overline{c}h_j^{(i)}(x) + \overline{d}$  with the exact linear function  $a_j^{(i)}(x) = h_j^{(i)}(x)$  and  $a_j^{(i)}(x) = 0$ , respectively, as shown in Figure 1 (unstable to stable). This can then tighten the linear bounds for the other neurons, thus tightening the under-approximation on each subdomain.

Example 5. We now apply our algorithm with ReLU splitting to the vehicle parking problem in Example 1. Figure 2d shows the refined preimage polytope by adding the splitting plane (black solid line) along the direction of a selected unstable ReLU node. Compared with Figure 2b, we can see that the volume of the approximation is improved.

Remark 1 (Preimage Over-approximation). While Algorithms 1 and 2 focus on preimage under-approximations, they can be easily configured to generate over-approximations with two key modifications. Firstly, we generate polytope over-approximations by using LiRPA to propagate a linear upper bound  $\overline{g_i}(x) = \overline{a_i}^T x + \overline{b_i}$  for each output constraint, such that  $g_i(x) \geq 0 \implies \overline{g_i}(x) \geq 0$  for  $x \in \mathcal{C}$ . Secondly, the refinement and optimization objective is to minimize the volume of the over-approximation instead of maximizing the volume as in the case of under-approximation.

# 4.4 Overall Algorithm

Our overall preimage approximation method is summarized in Algorithm 1. It takes as input a neural network f, input region  $\mathcal{C}$ , output region O, target polytope volume threshold v (a proxy for approximation precision), termination iteration number R, and a Boolean indicating whether to use input or ReLU splitting, and returns a disjoint polytope union  $\mathcal{T}$  representing an underapproximation to the preimage.

The algorithm initiates and maintains a priority queue of (sub)regions according to Equation 2. The *initialization* step (Lines 1-3) generates an initial polytope approximation on the whole region using Algorithm 2 (Sections 4.1,

# **Algorithm 3:** Quantitative Verification

```

Input: Neural network f, Property (I, O, p), Maximum iterations R

Output: Verification Result \in \{\text{True, False, Unknown}\}\

1 \text{ vol}(I) \leftarrow \text{ExactVolume}(I);

// For general polytopes I

2 \ \mathcal{C} \leftarrow \text{OuterBox}(I) ;

3 \mathcal{T} \leftarrow \text{InitialRun}(f, \mathcal{C}, O);

4 while Iterations \leq R do

5

\mathcal{T} \leftarrow \text{Refine}(f, \mathcal{T}, \mathcal{C}, O);

6

if EstimateVolume(\mathcal{T}) > p \times vol(I) then

if ExactVolume(\mathcal{T}) \geq p \times \text{vol}(I) then

7

return True

8

if AllReLUSplit then

9

10

return False

11 return Unknown

```

4.2). Then, the preimage refinement loop (Lines 4-14) partitions a subregion in each iteration, with the preimage restricted to the child subregions then being re-approximated (Line 10-11). In each iteration, we choose the region to split (Line 5) and the splitting plane to cut on (Line 7 for input split and Line 9 for ReLU split), as detailed in Section 4.3. The preimage under-approximation is then updated by computing the priorities for each subregion (by approximating volumes) (Lines 12-14). The loop terminates and the approximation returned when the target volume threshold v or maximum iteration limit R is reached.

# 4.5 Quantitative Verification

We now show how to use our efficient preimage under-approximation method (Algorithm 1) to verify a given quantitative property (I,O,p), where O is a polyhedron, I a polytope and p the desired proportion value, summarized in Algorithm 3. To simplify assume that I is a hyperrectangle, so that we can take  $\mathcal{C} = I$  (in view of space constraints the case of general polytopes is discussed in Appendix of [45]). We utilize Algorithm 1 by setting the volume threshold to  $p \times \operatorname{vol}(I)$ , such that we have  $\frac{\widehat{\operatorname{vol}}(\mathcal{T})}{\operatorname{vol}(I)} \geq p$  if the algorithm terminates before reaching the maximum number of iterations. However, the Monte Carlo estimates of volume cannot provide a sound guarantee that  $\frac{\operatorname{vol}(\mathcal{T})}{\operatorname{vol}(I)} \geq p$ . To resolve this problem, we propose to run exact volume computation [5] only when the Monte Carlo estimate reaches the threshold. If the exact volume  $\operatorname{vol}(\mathcal{T}) \geq p \times \operatorname{vol}(I)$ , then the property is verified. Otherwise, we continue running the preimage refinement.

In Algorithm 3, InitialRun generates an initial approximation to the preimage as in Lines 1-3 of Algorithm 1, and Refine performs one iteration of approximation refinement (Lines 5-14). Termination occurs when we have verified or falsified the quantitative property, or when the maximum number of iterations has been exceeded.

**Proposition 3.** Algorithm 3 is sound for quantitative verification with input splitting.

**Proposition 4.** Algorithm 3 is sound and complete for quantitative verification on piecewise linear neural networks with ReLU splitting.

# 5 Experiments

We have implemented our approach as a prototype tool <sup>3</sup> for preimage approximation for polyhedron-type output sets/specifications. In this section, we perform experimental evaluation of the proposed approach on a set of benchmark tasks and demonstrate its effectiveness in approximation generation and its application to quantitative analysis of neural networks.

# 5.1 Benchmark and Evaluation Metric

We evaluate our preimage analysis approach on a benchmark of reinforcement learning and image classification tasks. Besides the vehicle parking task [3] shown in the running example, we use the following (trained) benchmarks: (1) aircraft collision avoidance system (VCAS) [21] with 9 feed-forward neural networks (FNNs); (2) neural network controllers from VNN-COMP 2022 [1] for three reinforcement learning tasks (Cartpole, Lunarlander, and Dubinsrejoin) [9]; and (3) the neural network from VNN-COMP 2022 for MNIST classification. Details of the models and additional experiments can be found in Appendix of [45].

**Evaluation Metric** To evaluate the quality of the preimage approximation, we define the coverage ratio to be the ratio of volume covered to the volume of the exact preimage, i.e.,  $\operatorname{cov}(\mathcal{T}, f_{\mathcal{C}}^{-1}(O)) := \frac{\operatorname{vol}(\mathcal{T})}{\operatorname{vol}(f_{\mathcal{C}}^{-1}(O))}$ . Note that this is a normalized measure for assessing the quality of the approximation, as shown in Algorithm 3 when comparing with target coverage proportion p for termination of the refinement loop, and not as a measure for formal verification guarantees. In practice, we estimate  $\operatorname{vol}(f_{\mathcal{C}}^{-1}(O))$  as  $\widehat{\operatorname{vol}}(f_{\mathcal{C}}^{-1}(O)) = \operatorname{vol}(\mathcal{C}) \times \frac{1}{N} \sum_{i=1}^{N} \mathbb{1}_{f(x_i) \in O}$ , where  $x_1, ... x_N$  are samples from  $\mathcal{C}$ . In Algorithm 1, the target volume (stopping criterion) is set as  $v = r \times \widehat{\operatorname{vol}}(f_{\mathcal{C}}^{-1}(O))$ , where r is the target coverage ratio.

### 5.2 Evaluation

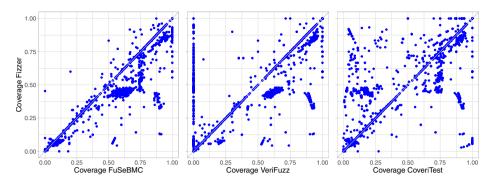

Effectiveness in Preimage Approximation with Input Split We apply Algorithm 1 with input splitting to the input bounding problem for low-dimensional reinforcement learning tasks to evaluate its effectiveness. For comparison, we also run the exact preimage (Exact) [27] and preimage over-approximation (Invprop) [23, 24] methods.

Vehicle Parking & VCAS. Table 1 presents experimental results on the vehicle parking and VCAS tasks. In the table, we show the number of polytopes (#Poly)

$<sup>^3</sup>$  The source code is at https://github.com/Zhang-Xiyue/PreimageApproxForNNs.

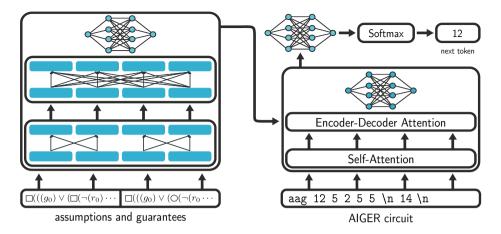

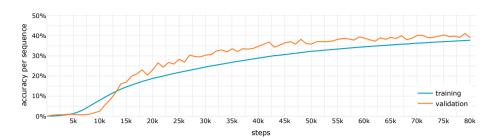

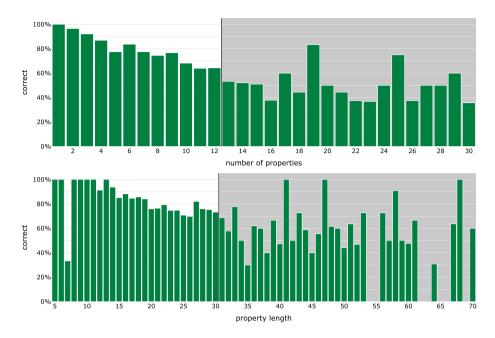

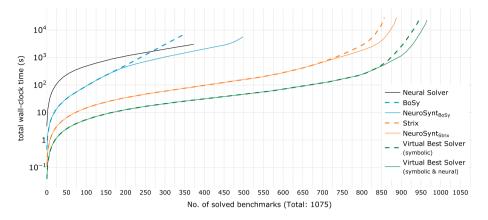

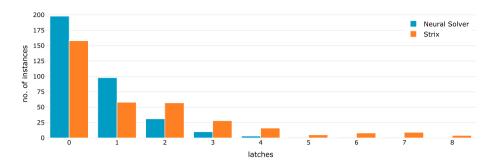

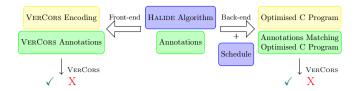

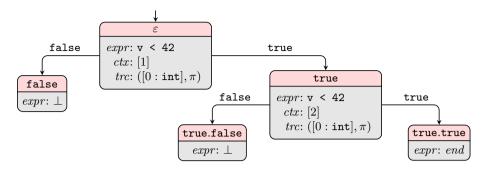

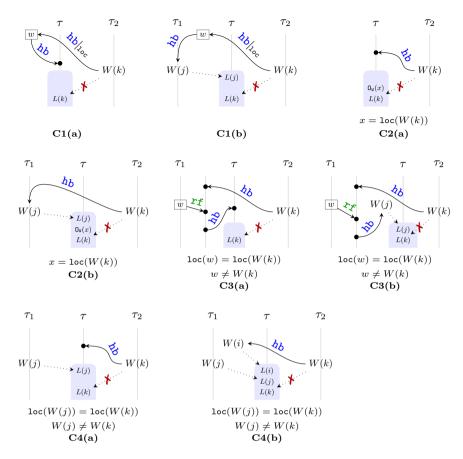

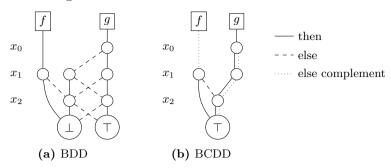

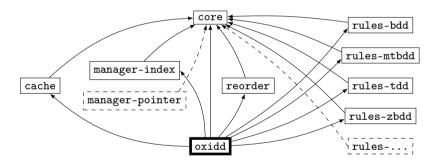

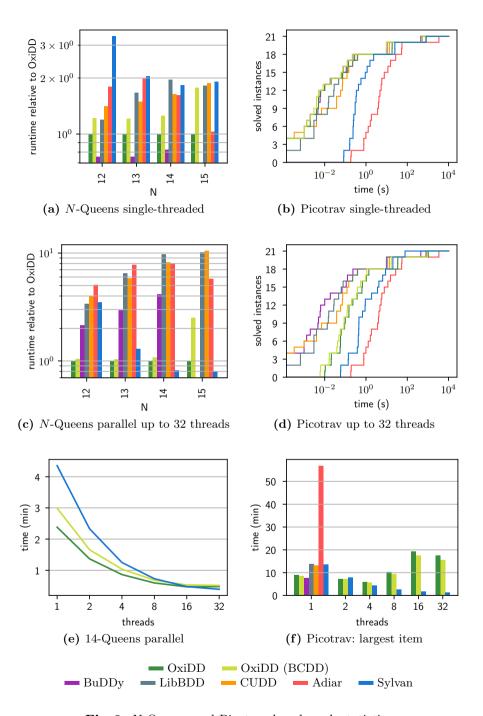

| Models                                                                           | Exact |                 | Invprop |                          | Our                |        |                          |