Ruzica Piskac / Michael W. Whalen (Eds.)

# PROCEEDINGS OF THE 21ST CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2021

Ruzica Piskac / Michael W. Whalen (Eds.)

PROCEEDINGS OF THE 21ST CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2021

### Conference Series: Formal Methods in Computer-Aided Design Volume 2

Conference Series: Formal Methods in Computer-Aided Design

Series edited by: Warren A. Hunt, Jr., The University of Texas at Austin Austin, TX 78705 | hunt@cs.utexas.edu Georg Weissenbacher, TU Wien

Karlsplatz 13, 1040 Wien, Austria | georg.weissenbacher@tuwien.ac.at

The Conference on Formal Methods in Computer-Aided Design (FMCAD) is an annual conference on the theory and applications of formal methods in hardware and system verification. FMCAD provides a leading forum to researchers in academia and industry for presenting and discussing groundbreaking methods, technologies, theoretical results, and tools for reasoning formally about computing systems. FMCAD covers formal aspects of computer-aided system design including verification, synthesis, and testing.

Information on this publication series and the volumes published therein is available at www.tuwien.ac.at/academicpress.

Volume 2 edited by:

Ruzica Piskac, Yale University

51 Prospect Street, New Haven, CT 06511, USA | ruzica.piskac@yale.edu

Michael W. Whalen, Amazon Web Services, Inc.

323 N Washington Ave, Minneapolis, MN 55401, USA | mww@amazon.com

# PROCEEDINGS OF THE 21ST CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2021

#### Cite as:

Piskac, R. & Whalen, M. W. (Eds.). (2021). Proceedings of the 21st Conference on Formal Methods in Computer-Aided Design – FMCAD 2021. TU Wien Academic Press. https://doi.org/10.34727/2021/isbn.978-3-85448-046-4

### TU Wien Academic Press, 2021

c/o TU Wien Bibliothek TU Wien Resselgasse 4, 1040 Wien academicpress@tuwien.ac.at www.tuwien.at/academicpress

This work is licensed under a Creative Commons attribution 4.0 international license (CC BY 4.0). https://creativecommons.org/licenses/by/4.0/

ISBN (online): 978-3-85448-046-4 ISSN (online): 2708-7824

Available online: https://doi.org/10.34727/2021/isbn.978-3-85448-046-4

Media proprietor: TU Wien, Karlsplatz 13, 1040 Wien Publisher: TU Wien Academic Press Publication series editor: Warren A. Hunt, Jr. and Georg Weissenbacher Editors (responsible for the content): Ruzica Piskac and Michael W. Whalen

### **Preface**

These are the proceedings of the twenty-first International Conference on Formal Methods in Computer-Aided Design (FMCAD), which was held online from October 18 – October 22, 2021 due to the coronavirus. FMCAD was constituted in 1996 as a conference covering formal aspects of specification, verification, synthesis, testing, and security, and as a leading forum for researchers and practitioners in academia and industry alike. 2021 marks the 25th anniversary of that original meeting, and so we wish to celebrate the vision of those original organizers!

The program of FMCAD 2021 is comprised of four tutorials, three invited talks, a student forum, an industry night, a panel session on "25 years of FMCAD", and the main program consisting of presentations of 30 accepted papers. The tutorial day featured four presentations:

- Active Automata Learning: from  $L^*$  to  $L^\#$  by Frits Vaandrager

- Stainless Verification System Tutorial by Viktor Kuncak

- Reactive Synthesis Beyond Realizability by Rayna Dimitrova

- Formal Methods for the Security Analysis of Smart Contracts by Matteo Maffei

and the main conference featured three invited talks:

- From Viewstamped Replication to Blockchains by Barbara Liskov

- Algorithms for the People by Seny Kamara

- Engineering with Full-scale Formal Architecture: Morello, CHERI, Armv8-A, and RISC-V by Peter Sewell

FMCAD'21 also hosted the ninth edition of the Student Forum, which has been held annually since 2013 and provides a platform for graduate students at any career stage to introduce their research to the FMCAD community. The FMCAD Student Forum 2021 was organized by Mark Santolucito and featured short presentations of 11 accepted contributions. A detailed description of the Student Forum, listing all accepted contributions, is provided in the conference proceedings. FMCAD 2021 received 72 submissions out of which the committee decided to accept 30 for publication. Each submission received at least three reviews. The topics of the accepted papers include hardware and software verification, SAT, SMT, learning, synthesis, Neural-Network verification, and more. Out of the accepted papers, 23 are classified as regular papers (20 long and 3 short) and 7 are classified as tool/case study papers (5 long and 2 short).

Organizing this event would not have been possible without the support of a large number of people and our sponsors. The program committee members and additional reviewers, listed on the following pages, did an excellent job providing detailed and insightful reviews, which helped the authors to improve their submissions and guided the selection of the papers accepted for publication. We thank each and everyone of them for dedicating their time and providing their expertise. We thank William Hallahan (Yale University) for being the web master, Daniel Schoepe for being the Sponsorship Chair, and Mark Santolucito for organizing this year's FMCAD Student Forum. We thank Georg Weissenbacher (TU Wien) both for his exceptional assistance in organizing the event, communicating to us the decisions of the steering committee, as well as being the publication chair. Holding a conference like FMCAD would not be feasible without the financial support of our sponsors. We would like to express our gratitude to our sponsors (in alphabetical order): Amazon Web Services, Amazon Prime Video, Cadence, Centaur Technology, Galois, Intel, Mentor Graphics, Novi, and Synopsys.

The conference proceedings are available as Open Access Proceedings published by TU Wien Academic Press, and through the IEEE Xplore Digital Library. Last but not least, we thank all authors who submitted their papers to FMCAD 2021 (accepted or not), and whose contributions and presentations form the core of the conference. We are grateful to everyone who presented their paper, gave a keynote or gave a tutorial. We thank all attendees of FMCAD for supporting the conference and making FMCAD a stimulating and enjoyable event.

October, 2021 Ruzica Piskac, Yale University

Michael W. Whalen, Amazon Inc. and the University of Minnesota

### Organizing Committee

### **Program Co-Chairs**

Ruzica Piskac Yale University

Michael W. Whalen Amazon Inc. and the University of Minnesota

Webmaster

William Hallahan Yale University

**Student Forum Chair**

Mark Santolucito Barnard College of Columbia University

**Publication Chair**

Georg Weissenbacher TU Wien

**Steering Committee**

Clark Barrett Stanford University

Armin Biere Johannes Kepler University Linz

Anna Slobodova Centaur Technology

Georg Weissenbacher TU Wien

### **Program Committee**

Erika Abraham RWTH Aachen University

Jade Alglave University College London

Pranav Ashar Real Intent

Per Bjesse Synopsys

Roderick Bloem Graz University of Technology

Ivana Cerna Masaryk University

Supratik Chakraborty IIT Bombay

Sylvain Conchon Université Paris-Sud

Leonardo de Moura Microsoft

Rayna Dimitrova CISPA Helmholtz Center for Information Security

Grigory Fedyukovich

Arie Gurfinkel

Liana Hadarean

Amazon Web Services

Ziyad Hanna

Cadence Design System

Fei He

Tsinghua University

Marijn Heule Carnegie Mellon University

Warren A. Hunt, Jr.

The University of Texas at Austin

Alexander Ivrii IBM

Dejan Jovanović Amazon Web Services Alan Jovic University of Zagreb

Laura Kovacs TU Wien

Ton Chanh Le Stevens Institute of Technology

Rebekah Leslie-Hurd Intel

Kuldeep S. Meel National University of Singapore

Ruzica Piskac Yale University

Elizabeth Polgreen University of California, Berkeley

Andrew Reynolds University of Iowa Christoph Scholl University of Freiburg

Natasha Sharygina Università della Svizzera italiana (USI Lugano, Switzerland)

Anna Slobodova Centaur Technology Christoph Sticksel The MathWorks

Murali Talupur Amazon Web Services, Inc.

Jean-Baptiste Tristan Boston College Yakir Vizel The Technion

Thomas Wahl Northeastern University

Georg Weissenbacher TU Wien

Michael Whalen Amazon Inc. and the University of Minnesota

Thomas Wies New York University

Valentin Wüstholz ConsenSys

Lenore Zuck University of Illinois in Chicago

### Additional Reviewers

Asadi, Sepideh

Athanasiou, Konstantinos

Bansal, Suguman Barnett, Lee Bendík, Jaroslav Blicha, Martin Bustan, Doron

Cano, Filip Chalupa, Marek Cheang, Kevin Chen, Hao

Chernigovskaia, Lidiia

Ebrahimi, Masoud

Fan, Hongyu Fernandez, Matt Fraer, Ranan

Georgiou, Pamina Goel, Shilpi Golia, Priyanka Grundy, Jim

Hamza, Ameer Hjort, Håkan Hoereth, Stefan Hozzová, Petra Huang, Daniel Hyvärinen, Antti

Jacoby, Reily Jain, Himanshu Jain, Mitesh Jin, Hoon Sang Jonas, Martin Könighofer, Bettina

Kwan, Carl

Larrauri, Alberto Le, Nham

Maderbacher, Benedikt Majumdar, Rupak Moosbrugger, Marcel Mora, Federico

Nalbach, Jasper

Otoni, Rodrigo

Ramanathan, Vivek Rane, Ashay Reeves, Joseph Rehak, Vojtech Ročkai, Petr

Santolucito, Mark Schoisswohl, Johannes Seufert, Tobias

Shi, Yunong Soos, Mate

Stankovic, Miroslav Strejček, Jan Strichman, Ofer

Sumners, Rob Swords, Sol

Tassarotti, Joseph Temel, Mertcan

Vediramana Krishnan, Hari Govind

Wolfovitz, Guy

# Table of Contents

### **Tutorials**

| Reactive Synthesis Beyond Realizability                                                                                                                                                                                                                                                                                 | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Stainless Verification System Tutorial                                                                                                                                                                                                                                                                                  | 2  |

| Formal Methods for the Security Analysis of Smart Contracts                                                                                                                                                                                                                                                             | 8  |

| Active Automata Learning: from L* to L#                                                                                                                                                                                                                                                                                 | 9  |

| Invited Talks                                                                                                                                                                                                                                                                                                           |    |

| From Viewstamped Replication to Blockchains                                                                                                                                                                                                                                                                             | 10 |

| Algorithms for the People                                                                                                                                                                                                                                                                                               | 11 |

| Engineering with Full-scale Formal Architecture: Morello, CHERI, Armv8-A, and RISC-V                                                                                                                                                                                                                                    | 12 |

| Student Forum                                                                                                                                                                                                                                                                                                           |    |

| The FMCAD 2021 Student Forum                                                                                                                                                                                                                                                                                            | 13 |

| Hardware                                                                                                                                                                                                                                                                                                                |    |

| CocoAlma: A Versatile Masking Verifier                                                                                                                                                                                                                                                                                  | 14 |

| End-to-End Formal Verification of a RISC-V Processor Extended with Capability Pointers                                                                                                                                                                                                                                  | 24 |

| Hardware Security Leak Detection by Symbolic Simulation                                                                                                                                                                                                                                                                 | 34 |

| Scaling Up Hardware Accelerator Verification using A-QED with Functional Decomposition Saranyu Chattopadhyay, Florian Lonsing, Luca Piccolboni, Deepraj Soni, Peng Wei, Xiaofan Zhang, Yuan Zhou, Luca Carloni, Deming Chen, Jason Cong, Ramesh Karri, Zhiru Zhang, Caroline Trippel, Clark Barrett and Subhasish Mitra | 42 |

| Sound and Automated Verification of Real-World RTL Multipliers                                                                                                                                                                                                                                                          | 53 |

### Model Checking and IC3

| IC3 with Internal Signals                                            |

|----------------------------------------------------------------------|

| Single Clause Assumption without Activation Literals to Speed-up IC3 |

| Logical Characterization of Coherent Uninterpreted Programs          |

| Data-driven Optimization of Inductive Generalization                 |

| Model Checking AUTOSAR Components with CBMC                          |

| Concurrency and Distributed Systems                                  |

| Automating System Configuration                                      |

| Towards an Automatic Proof of Lamport's Paxos                        |

| Refinement-Based Verification of Device-to-Device Information Flow   |

| Celestial: A Smart Contracts Verification Framework                  |

| The Civl Verifier                                                    |

| Applied Verification and Synthesis                                   |

| Synthesizing Pareto-Optimal Interpretations for Black-Box Models     |

| Dynamic Partial Order Reduction for Spinloops                        |

| Robustness between Weak Memory Models                                |

| Pruning and Slicing Neural Networks using Formal Verification        |

| Towards Scalable Verification of Deep Reinforcement Learning         |

### **SAT Solving**

| Exploiting Isomorphic Subgraphs in SAT                        | 204 |

|---------------------------------------------------------------|-----|

| On Decomposition of Maximal Satisfiable Subsets               | 212 |

| Designing Samplers is Easy: The Boon of Testers               | 222 |

| SAT-Inspired Eliminations for Superposition                   | 231 |

| SAT Solving in the Serverless Cloud                           | 241 |

| SMT and First-Order Logic                                     |     |

| Induction with Recursive Definitions in Superposition         | 246 |

| Fair and Adventurous Enumeration of Quantifier Instantiations | 256 |

| Mathematical Programming Modulo Strings                       | 261 |

| Lookahead in Partitioning SMT                                 | 271 |

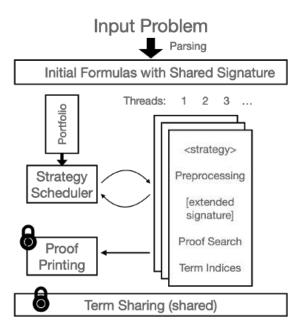

| A Multithreaded Vampire with Shared Persistent Grounding      | 280 |

### Reactive Synthesis Beyond Realizability

Rayna Dimitrova CISPA Helmholtz Center for Information Security Saarbrücken, Germany dimitrova@cispa.de

Abstract—The automatic synthesis of reactive systems from high-level specifications is a highly attractive and increasingly viable alternative to manual system design, with applications in a number of domains such as robotic motion planning, control of autonomous systems, and development of communication protocols. The idea of asking the system designer to describe what the system should do instead of how exactly it does it, holds a great promise. However, providing the right formal specification of the desired behaviour of a system is a challenging task in itself. In practice it often happens that the system designer provides a specification that is unrealizable, that is, there is no implementation that satisfies it. Such situations typically arise because the desired behavior represents a trade-off between multiple conflicting requirements, or because crucial assumptions about the environment in which the system will execute are missing. Addressing such scenarios necessitates a shift towards synthesis algorithms that utilize quantitative measures of system correctness. In this tutorial I will discuss two recent advances in this research direction.

First, I will talk about the maximum realizability problem, where the input to the synthesis algorithm consists of a hard specification which must be satisfied by the synthesized system, and soft specifications which describe other desired, possibly prioritized properties, whose violation is acceptable. I will present a synthesis algorithm that maximizes a quantitative value associated with the soft specifications, while guaranteeing the satisfaction of the hard specification. In the second half of the tutorial I will present algorithms for synthesis in bounded environments, where a bound is associated with the sequences of input values produced by the environment. More concretely, these sequences consists of an initial prefix followed by a finite sequence repeated infinitely often, and satisfy the constraint that the sum of the lengths of the initial prefix and the loop does not exceed a given bound. I will also discuss the synthesis of approximate implementations from unrealizable specifications, which are guaranteed to satisfy the specification on at least a specified portion of the bounded-size input sequences. I will conclude by outlining some of the open avenues and challenges in quantitative synthesis from temporal logic specifications.

This tutorial is based on joint work with Mahsa Ghasemi and Ufuk Topcu published in [1], [2], and with Bernd Finkbeiner and Hazem Torfah published in [3].

#### REFERENCES

- [1] R. Dimitrova, M. Ghasemi, and U. Topcu, "Reactive synthesis with maximum realizability of linear temporal logic specifications," Acta Informatica, vol. 57, no. 1-2, pp. 107-135, 2020.

- -, "Maximum realizability for linear temporal logic specifications," in Automated Technology for Verification and Analysis 16th International Symposium, ATVA 2018, Los Angeles, CA, USA, October 7-10, 2018, Proceedings, ser. Lecture Notes in Computer Science, S. K. Lahiri and C. Wang, Eds., vol. 11138. Springer, 2018, pp. 458-475.

- R. Dimitrova, B. Finkbeiner, and H. Torfah, "Synthesizing approximate implementations for unrealizable specifications," in Computer Aided Verification - 31st International Conference, CAV 2019, New York City, NY, USA, July 15-18, 2019, Proceedings, Part I, ser. Lecture Notes in Computer Science, I. Dillig and S. Tasiran, Eds., vol. 11561. Springer, 2019, pp. 241-258.

### Stainless Verification System Tutorial

Viktor Kunčak LARA Research Group School of Computer and Communication Sciences **EPFL** Lausanne, Switzerland viktor.kuncak@epfl.ch

Jad Hamza LARA Research Group School of Computer and Communication Sciences **EPFL** Lausanne, Switzerland jad.hamza@epfl.ch

Abstract—Stainless ( https://stainless.epfl.ch ) is an open-source tool for verifying and finding errors in programs written in the Scala programming language. This tutorial will not assume any knowledge of Scala. It aims to get first-time users started with verification tasks by introducing the language, providing modelling and verification tips, and giving a glimpse of the tool's inner workings (encoding into functional programs, function unfolding, and using theories of satisfiability modulo theory solvers Z3 and CVC4).

Stainless (and its predecessor, Leon) has been developed primarily in the EPFL's Laboratory for Automated Reasoning and Analysis in the period from 2011-2021. Its core specification and implementation language are typed recursive higher-order functional programs (imperative programs are also supported by automated translation to their functional semantics). Stainless can verify that functions are correct for all inputs with respect to provided preconditions and postconditions, it can prove that functions terminate (with optionally provided termination measure functions), and it can provide counter-examples to safety properties. Stainless enables users to write code that is both executed and verified using the same source files. Users can compile programs using the Scala compiler and run them on the JVM. For programs that adhere to certain discipline, users can generate source code in a small fragment of C and then use standard C compilers.

Index Terms—verification, formal methods, proof, counterexample, model checking, Scala, functional programming, satisfiability modulo theories

### I. INTRODUCTION

Stainless [1] is a tool for verifying and finding errors in programs written in a subset of the Scala [2] programming language. Stainless is open source (distributed under Apache license) and hosted on GitHub at:

> https://github.com/epfl-lara/stainless/ https://epfl-lara.github.io/stainless/

Stainless (and its predecessor, Leon) have been developed primarily in the EPFL's Laboratory for Automated Reasoning and Analysis in the period from 2011-2021, see, in particular [1], [3] as well as [4]-[14]. The core specification and implementation language of Stainless are typed recursive higherorder functional Scala programs. It also supports certain imperative programs [4], [6]. Stainless can verify that functions are correct for all inputs with respect to provided preconditions and postconditions, it can prove that functions terminate (with optionally provided termination measure functions), and it can also provide counter-examples to safety properties.

Stainless can be used to write programs that are directly executable and proven correct. In particular, because it uses Scala's syntax and type system, users can execute Stainless programs using the standard Scala compiler (version 2.12.13 at the time of writing). In addition, there are passes that eliminate non-executable (ghost) code from source to make sure that it does not result in run-time overhead after compilation. For programs that adhere to certain discipline the "genc" option of Stainless can be used to generate C source code that compiles with common compilers such as gcc.

### A. Outline

In this tutorial, we show examples demonstrating how to use Stainless to develop verified models and programs. We will mostly use basic notation for functional programming, which we will introduce along the way. We will use Stainless version 0.9 or later.

In addition to basic introduction, we will suggest strategies for specifying programs and helping Stainless prove them correct. An example is using lemmas and proving them by induction expressed through terminating recursion.

To help users be more effective when using Stainless, we also outline key mechanisms that Stainless uses in proof and counterexample search: encoding into functional programs, function unfolding, and using rich theories of satisfiability modulo theory solvers Z3 and CVC4.

### II. GETTING STARTED

Stainless is a command line application that runs on the Java virtual machine, version 1.8. We mostly test it on Ubuntu Linux. We provide releases for Linux and Mac. Others use it on Windows as well, where it may be simplest to use Windows Subsystem for Linux to get started. Download the release file from

https://github.com/epfl-lara/stainless/releases/

then unzip the file and put a link to stainless in your path.

The following is a simple program, call it MaxBug.scala, containing a function max. Max attempts to compute maximum of the two 32-bit integers by returning one of them, depending on the sign d of their difference.

```

object TestMax {

def max(x: Int, y: Int): Int = {

val d = x - y

if (d > 0) x

else y

} ensuring(res =>

x <= res && y <= res && (res == x || res == y))

}</pre>

```

We use object to group functions into modules. We define functions using def and provide their parameters (here: x and y) and their types, as well as the return type. We define local immutable values using val keyword. Scala infers the type of d as Int.

After the usual body, we introduced an ensuring statement. The first identifier, res, binds the return value of the function. After the arrow => we state the property we would like the result to satisfy. In this case, the result should be greater than each argument and it should be equal to one of them.

Invoke stainless MaxBug.scala and you may get output containing some of the following.

```

MaxBug.scala:7:49: warning: => INVALID

x \le res \&\& y \le res \&\& (res == x || res == y))

warning: Found counter-example:

warning: y: Int -> -2147483648

x: Int -> 1

Verified: 0 / 3

stainless summary

MaxBug.scala:3:13: max Subtraction overflow invalid

MaxBug.scala:7:37: max postcondition

invalid

MaxBug.scala:7:49: max postcondition

invalid

valid: 0

(0 from cache) invalid: 3

total: 3

```

Use --timeout=5 to set time out to 5 seconds. and --no-colors to request clean ASCII output with parsable line numbers in reports.

Why did Stainless report a counterexample? Indeed, executing  $\max$  with the two provided values computes using signed 32-bit arithmetic the value -11 for d, so the function returns y as the result res so y <= res is false. We can repair this example in at least two ways:

- Use if  $(x \le y)$  instead of the value d.

- Use BigInt instead of Int, thus adopting unbounded integers instead signed 32-bit ones.

If you run your program several times, you may notice that Stainless reports that a valid verification condition was persistently cached (inside .stainless-cache). You can turn off caching with --vc-cache=false.

You may find the --watch option useful when modifying a file several times, which makes Stainless run verification whenever the source file is changed.

By default, Stainless uses a version of z3 (4.7.1) which is packaged inside Stainless (--solvers=nativez3). This allows Stainless to interact with z3 through Java calls. You may also use an externally built version of z3 (for instance, z3 4.8.12 is shipped with the release) by specifying --solvers=smt-z3. In that case, Stainless will communicate with z3 using SMT-LIB files, which might be slower than Java calls, but has two

benefits. First, you get to use the newest release of z3. Second, smt-z3 is more likely to respect timeouts than nativez3.

You can also use CVC4 as the solver if you download and put cvc4 executable on your path. You can use both with --solvers=smt-cvc4, smt-z3. Use --debug=smt to preserve the generated SMT-LIB files and look for them in the smt-sessions directory.

### III. VERIFIED FUNCTIONAL PROGRAMMING

We will now implement a simple function that computes differences of successive elements of a list. Let us start our file with import stainless.collection.\_ so we can use the immutable List library of Stainless. You can find the sources of this and other library files at following URL:

https://github.com/epfl-lara/stainless/blob/master/frontends/library/stainless/collection/List.scala

Let's try to write a function diffs that takes a list of elements, for example  $x_1, x_2, x_3, x_4$  and keeps the first element and then follows it by the list of their differences. In this case we would like to obtain  $x_1, x_2 - x_1, x_3 - x_2, x_4 - x_3$ . For empty and one-element list the output equals input. Let us write this as the default implementation. We can also state the example of four-element list as a symbolic test case. To state it, we use another function with a dummy body and a postcondition that invokes diffs.

```

import stainless.collection._

object Diffs {

def diffs(1: List[BigInt]): List[BigInt] = {

l match {

case Nil() => 1

case _ :: Nil() => 1

// missing cases

}

}

def test(x1: BigInt, x2: BigInt,

x3: BigInt, x4: BigInt): Unit = {

} ensuring(_ =>

diffs(List(x1, x2, x3, x4)) ==

List(x1, x2 - x1, x3 - x2, x4 - x3))

}

```

After developing a function that meets this partial specification, we can see whether it meets a stronger specification. For example, we can define the inverse function undiff that takes  $y_0, y_1, \ldots, y_n$  and computes  $y_0, y_0 + y_1, \ldots, \sum_{i=0}^n y_i$ . Being masters of functional programming, we recognize that this is just a prefix sum of a list, so we define it by

```

def undiff(l: List[BigInt]): List[BigInt] =

l.scanLeft(BigInt(0))(_ + _).tail

```

where scanLeft is defined in our List library. Now we can add as the ensuring condition of diffs the condition ensuring (res => (undiff(res) == 1)). It so happens that Stainless proves this condition automatically using its algorithm. As an off-line exercise, try to prove this result with pen and paper. This might give you a sense on how Stainless is able to prove this property.

The algorithm of Stainless initially treats called functions as unknown (uninterpreted) mathematical functions. It then

iteratively expands each call by defining the function to be equal to one unfolding of its body and also inserts the ensuring clause as an assumption.

### IV. AMORTIZED QUEUE

We have found Stainless to work very well for verification of purely functional data structures. Let us examine the case of an amortized queue such as the one from [15, Section 5.2, Page 42]. We will start by writing down an *abstract class*. In this class we define methods with dummy bodies denoted by ??? but with ensuring clauses that specify the desired behavior of operations. To specify the behavior we use tolist function, which is also left unspecified in the abstract class.

```

import stainless.collection._

import stainless.lang._

abstract class Queue[A] {

def enqueue(a: A) = (??? : Queue[A])

.ensuring(res =>

res.toList == this.toList ++ List(a))

def dequeue: Option[(A, Queue[A])] =

(??? : Option[(A, Queue[A])])

.ensuring(res => res match {

case None() =>

this.toList == Nil[A]()

case Some((a, q)) =>

this.toList == a :: q.toList

})

def toList: List[A]

}

```

When we extend the abstract class, Scala requires us to define toList, whereas Stainless ensures that our implementation meets the specifications in the abstract class. We can implement an inefficient queue using a single list.

```

case class SimpleQueue[A](1: List[A])

extends Queue[A] {

def enqueue(a: A) = SimpleQueue(1 ++ List(a))

def dequeue = 1 match {

case Nil() => None()

case Cons(x, xs) => Some((x, SimpleQueue(xs)))

}

def toList = 1

```

Stainless successfully verifies that the properties required by a queue are satisfied by this implementation. Even if correct, this implementation is inefficient because enqueue takes linear time in the current number of queue elements. We will thus try to develop and prove correct the implementation like one from [15, Section 5.2, Page 42] that uses two lists and that has constant time amortized complexity.

The toList, which we use only for specification, gives us a hint on how to implement enqueue efficiently. For dequeue we will need a reverse operation on lists, which we can implement in linear time. Despite its complexity, our version

of dequeue will be verified automatically. As for enqueue, its implementation is simple, yet its proof turns out to require some well known property of lists that we need to tell Stainless to invoke explicitly!

```

def enqueue(a: A): Queue[A] = {

val res: Queue[A] = // to fill

// You can state using assertions things you know are true,

// to see if Stainless is able to prove them:

assert (res.toList == front ++ (a :: rear).reverse)

// Alternatively, you can use an equation style reasoning.

// Here Stainless should timeout from the second to the third

// step, because some steps are missing.

res.toList ==: | trivial |:

front ++ (a :: rear).reverse ==:| trivial |:

// Add missing steps here to arrive to the result.

// For complicated steps, you need to invoke lemmas

// instead of writing 'trivial'.

this.toList ++ List(a)

).qed

res

```

#### V. PROPERTIES AND PROOFS

How do we state properties in Stainless? We write a property  $\forall x: T.F(x)$  as a function lemmaF defined by:

```

def lemmaF(x: T): Unit = {

()

} ensuring (_ => F(x))

```

When we wish to instantiate the property taking x to be some specific value v, we insert a function invocation lemmaF(v) into the part of the code where we need this property. Suppose that proving property  $\forall x: T.F(x)$  is not automatic. Then verification of lemmaF itself will fail, as stated. If F(x), for example, follows from G(x, x + 1) that is established in lemmaG(x, y), then we can state and prove lemmaF as:

```

def lemmaF(x: T): Unit = {

lemmaG(x,x+1)

} ensuring (_ => F(x))

```

Thus, we can adopt the following strategies for libraries of lemmas:

- introduce a function for a lemma

- use a function parameter for each universally quantified variable

- write lemma statement in the ensuring clause

- use the body of the function to encode a high-level proof, with function invocations corresponding to applying previously proven lemmas.

Purely universal statements can return Unit type. For existential statements, we can often state their constructive Skolemized form and return a witness for the existential quantifier from the lemma.

It can be helpful to examine some proofs of properties in the List library. Remarkably, we can even make recursive invocations of functions in their bodies. Which mathematical reasoning principle do such proofs correspond to?

#### VI. DIGITS

For built-in types such as Int and Long, the SMT solvers will successfully reason about their bitwidth representation. What if we wish to reason about the bits of arbitrarily large numbers? As a simple example, let us define simple addition as a recursive function on lists of bits.

```

import stainless.annotation.

import stainless.lang._

import stainless.collection._

object AddBitwise {

type Digits = List[Boolean]

val zero = Nil[Boolean]()

def add(x: Digits, y: Digits, carry: Boolean):

Digits = {

require (x.length == y.length)

(x,y) match {

case (Nil(), Nil()) =>

if (carry) true::zero else zero

case (Cons(x1,xs), Cons(y1,ys)) => {

val z = x1 ^ y1 ^ carry

val carry1 = (x1 && y1) ||

(x1 && carry) ||

(y1 && carry)

z :: add(xs, ys, carry1)

}

}

```

How can we state that such addition is commutative? How can we prove it in Stainless? As an off-line exercise, think about how we can prove that this corresponds to actual addition on integers (BigInt).

### VII. TERMINATION

The following recursive function searches for an element in a sorted array, but it has a bug. You may run Stainless on this file to spot it. Fix the issue, and add a decreases clause at the beginning of the function to ensure that Stainless can prove the function terminating.

```

import stainless.lang._

object BinarySearch1 {

def search(arr: Array[Int], x: Int, lo: Int, hi:

Int): Boolean = {

if (lo <= hi) {

val i = (lo + hi) / 2

val y = arr(i)

if (x == y) true

else if (x < y) search(arr, x, lo, i-1)

else search(arr, x, i+1, hi)

} else {

false

}

}

}</pre>

```

In Stainless, all functions are required to have a measure (either inferred automatically, or written in a decreases clause by the user). The system in its current design would be unsound (we would be able to prove false postconditions or assertions) if we allowed non-terminating functions.

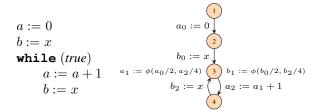

#### VIII. IMPERATIVE FEATURES

Stainless supports some imperative features, such as local mutable variables, while loops, return statements, and more (see https://epfl-lara.github.io/stainless/imperative.html). Stainless transforms these constructs into functional programs.

Using a while loop and a return statement, rewrite the findIndexOpt function:

that finds an index of element v in a sorted array ar. Prove that, when your function returns Some(i), then ar(i) == v. To prove that array indices are within bounds, you will need a loop invariant, for which the syntax is:

```

(while(...) {

decreases(...)

...

}).invariant(...)

```

Does Stainless help you if you make an overflow mistake when computing the middle of an interval using bounded arithmetic?

Note that while loops require decreases clauses as well (when the measure cannot be inferred automatically), because they are translated into recursive functions by Stainless. To see how the while loop and the return statement are transformed, you may run the command below on your file. Stainless has a pipeline containing several phases, and ReturnElimination is the one that removes while loops and return statements. The --debug-objects option tells Stainless to only display the findIndexOpt function in the debug output.

```

stainless --debug=trees

--debug-objects=findIndexOpt

--debug-phases=ReturnElimination FindIndex.scala

```

As a harder exercise, identify and prove a stronger postcondition of findIndexOpt: what can we state in the postcondition for the case when the function returns None? What assumptions and loop invariants do we need to be be able to prove this postcondition?

### IX. DESIGN PRINCIPLES

A number of verification systems have been developed in the past decades. Stainless tries to borrow many of the features that others and us have found useful in other systems. At the same time, it is driven by a somewhat unique combination of principles, whose understanding may help set the expectations from the tool.

### A. Searching for Both Proofs and Counterexamples

From the beginning [13], the system was designed to search for both counterexamples and proofs in a unified iterative loop. Thanks to this design, on many programs Stainless behaves like a combination of a bounded model checker and a k-inductive prover such as [16]: we can often expect a definite answer, whether the program verifies or has a counterexample.

### B. Recursive programs as foundation, not transition systems.

Operational semantics tells us that we can translate functional (and many other) programs into transition systems. This has even been used in verification tools with success []. Nonetheless, we believe that it carries significant overhead, especially for proofs. Thus, like in ACL2 [17], [18] our intermediate representation is based on recursive functions [13] and we hope to leverage high-level structure to make verification more feasible, much like Liquid Haskell [19] which needs to be complemented with symbolic execution to also generate counterexamples [20]. Consequently, iterative unfolding of our recursive functions in Stainless gives a different sequence of approximations than the one we would obtain by representing programs using control-flow graphs and explicit stacks [21].

### C. Top-down verification for each function.

Stainless verifies each desired function one by one. When verifying a function f, it does not check which other parts of code invoke f. In particular, it will, in its current design, not infer preconditions for a function automatically. Preconditions need to be explicitly specified using a require clause at function entry. On the other hand, when Stainless examines the body of f and finds a function g, then it will examine not only the specification of g, but also its body. If g is recursive, this process will continue, with a check for counterexample and check for unsatisfiability performed at each step. This process treats functions more transparently than some modular verifiers. The process is also breadth-first, instead of having the form of directed rewriting as in some other systems. The effectiveness of this process is explained in part by the fact that it results in a decision procedure for certain classes of functions [14], [22], [23]. Furthermore, we continue to be surprised by how well this simple strategy works in practice, even if we have no theoretical reason to know that it will succeed.

### D. Scala subset as the input language.

Stainless uses Scala as a language that has substantial user base, regularly ranked higher than Haskell and LISP in Stack Overflow developer surveys [24], which is relevant for maintaining the correspondence between what executes and that is verified. As a functional language, Scala contains an expressive purely functional fragment which can be used for specification and modelling. The users of Stainless thus largely avoid the need to learn a separate specification language, because functional programs are a great specification vehicle. At the same time, the system supports polymorphism and subtyping with a type system that eliminates many nonsensical programs before they waste user's time inside the program verifier's loop. That said, Stainless purposely avoids by design certain Scala 2 features, such as null references and complex initalization. Other features, such as machine integers, are modelled precisely: it is certainly necessary in practice to have machine integers of various width available (for example, 32-bit Int and 64-bit Long), but it is also helpful to use unbounded BigInt data types, especially for specifications, and these different types should not be confused. Stainless provides the user a choice and maps these data types and operations on them to the appropriate types and theories inside SMT solvers [8]. Subtyping is currently implemented via a translation into a language with disjoint types [3]; its use requires additional encoding and may slow down verification. Imperative features are supported as a choice of either unshared mutable state [6] or using a model [4] that, at user level, is similar to dynamic frames [25] of Dafny [26].

#### E. Embracing SMT solver theories, avoiding quantifiers.

Instead of using axioms to encode program semantics and data types, Stainless leverages algebraic data types, sets, and arrays. Stainless thus currently emits quantifier-free queries to solvers (either Z3 or CVC4). The hope with this choice is that SMT solvers will remain predictable for both proofs and counterexamples. In contrast, the use of quantifiers may lead to more automation and sometimes excellent performance for proofs, but quickly leads outside of the space where the solvers can reliable report counterexamples.

### F. Executability of programs and specifications.

In Stainless we aim to write programs that can be compiled using the standard Scala compiler. Specification constructs in Stainless are defined in a Scala library and they have dummy execution semantics. In some cases, even such dummy semantics may result in overhead, so we have developed passes that eliminate some of the specification code altogether. In addition, Stainless has a subset that can be used to generate C code suitable for embedded systems, an enhanced version of such functionality developed for Leon [27].

Acknowledgements. Research on Stainless has been funded in part by (i) the Swiss Science Foundation grants 200021\_132176, 200020\_138204, 200020\_146649, 200021\_144503, 200020\_159949, and 200021\_175676. (ii) European Research Council (ERC) Starting Grant PE6-306484-IMPRO, (iii) The Swiss State Secretariat for Education, Research and Innovation, Swiss Space Office grant "Embedded Flight Software Verification—ESOVER" and (iv) the envelope budget for the LARA group from the EPFL School of Computer and Communication Sciences.

Stainless and Inox were created from parts of Leon code by Nicolas Voirol. In addition to Nicolas and the two authors of this tutorial, contributors to Stainless and Inox include: Roman Ruetschi, Georg Stefan Schmid, Marco Antognini, Ravichandhran Madhavan, Etienne Kneuss, Lars Hupel, Emmanouil Koukoutos, Philippe Suter, Roman Edelmann, Utkarsh Upadhyay, Ivan Kuraj, Sandro Stucki, Ruzica Piskac, Tihomir Gvero, Czipó Bence, Sumith Kulal, Lucien Iseli, Regis Blanc, Iulian Dragos, Dragana Milovančević, Antoine Brunner, Mirco Dotta, Yann Bolliger, Rodrigo Raya, Samuel Gruetter, Mikaël Mayer, Guillaume Massé. Romain Jufer worked with Jad Hamza on a fork for smart contract verification and Solidity code generation, Romain Edelmann and Rodrigo Raya developed an interactive proof assistant concept

based on Inox. Regis Blanc developed a Scala library for input and output of SMT-LIB files. ScalaZ3 interface to the Z3 dynamically linked library additionally received contributions from Ali Sinan Köksal and Thorsten Tarrach. Contributors to Stainless Bolts case studies include additionally Samuel Chassot and Clément Burgelin. We thank users of Stainless from Ateleris GmbH including Simon Felix, Filip Schramka, and Ivo Nussbaumer. We also thank MSc students at EPFL taking the Formal Verification course, completing interesting case studies and identifying bugs in the system.

#### REFERENCES

- J. Hamza, N. Voirol, and V. Kunčak, "System FR: Formalized foundations for the Stainless verifier," *Proc. ACM Program. Lang*, no. OOPSLA, November 2019.

- [2] M. Odersky, L. Spoon, and B. Venners, *Programming in Scala*, 4th ed. Artima Inc, 2008.

- [3] N. C. Y. Voirol, "Verified functional programming," Ph.D. dissertation, EPFL, thesis number 9479, 2019. [Online]. Available: http://doi.org/10. 5075/epfl-thesis-9479

- [4] G. Schmid and V. Kunčak, "Proving and disproving programs with shared mutable data," 2021.

- [5] R. Madhavan, S. Kulal, and V. Kuncak, "Contract-based resource verification for higher-order functions with memoization," in ACM SIGACT-SIGPLAN Symposium on Principles of Programming Languages (POPL), 2017.

- [6] R. W. Blanc, "Verification by reduction to functional programs," Ph.D. dissertation, EPFL, thesis number 7636, 2017. [Online]. Available: http://doi.org/10.5075/epfl-thesis-9479

- [7] N. Voirol, E. Kneuss, and V. Kuncak, "Counter-example complete verification for higher-order functions," in *Scala Symposium*, 2015.

- [8] R. Blanc and V. Kuncak, "Sound reasoning about integral data types with a reusable SMT solver interface," in Scala Symposium, 2015.

- [9] V. Kuncak, "Developing verified software using Leon (invited contribution)," in NASA Formal Methods (NFM), 2015.

- [10] E. Koukoutos and V. Kuncak, "Checking data structure properties orders of magnitude faster," in *Runtime Verification (RV)*, 2014.

- [11] R. W. Blanc, E. Kneuss, V. Kuncak, and P. Suter, "An overview of the Leon verification system: Verification by translation to recursive functions," in *Scala Workshop*, 2013.

- [12] A. Köksal, V. Kuncak, and P. Suter, "Constraints as control," in ACM SIGACT-SIGPLAN Symposium on Principles of Programming Languages (POPL), 2012.

- [13] P. Suter, A. S. Köksal, and V. Kuncak, "Satisfiability modulo recursive programs," in *Static Analysis Symposium (SAS)*, 2011.

- [14] P. Suter, M. Dotta, and V. Kuncak, "Decision procedures for algebraic data types with abstractions," in ACM SIGACT-SIGPLAN Symposium on Principles of Programming Languages (POPL), 2010.

- [15] C. Okasaki, Purely Functional Data Structures. Cambridge University Press, 1998.

- [16] A. Champion, A. Mebsout, C. Sticksel, and C. Tinelli, "The kind 2 model checker," in Computer Aided Verification 28th International Conference, CAV 2016, Toronto, ON, Canada, July 17-23, 2016, Proceedings, Part II, ser. Lecture Notes in Computer Science, vol. 9780. Springer, 2016, pp. 510–517.

- [17] J. S. Moore, "Milestones from the pure lisp theorem prover to ACL2," Formal Aspects Comput., vol. 31, no. 6, pp. 699–732, 2019.

- [18] R. S. Boyer and J. S. Moore, "Proving theorems about LISP functions," in *Proceedings of the 3rd International Joint Conference on Artificial Intelligence. Standford, CA, USA, August 20-23, 1973*, N. J. Nilsson, Ed. William Kaufmann, 1973, pp. 486–493. [Online]. Available: http://ijcai.org/Proceedings/73/Papers/053.pdf

- [19] N. Vazou, "Liquid haskell: Haskell as a theorem prover," Ph.D. dissertation, UNIVERSITY OF CALIFORNIA, SAN DIEGO, 2016.

- [20] W. T. Hallahan, A. Xue, M. T. Bland, R. Jhala, and R. Piskac, "Lazy counterfactual symbolic execution," in *Proceedings of the 40th ACM SIGPLAN Conference on Programming Language Design and Implementation, PLDI 2019, Phoenix, AZ, USA, June 22-26, 2019*, K. S. McKinley and K. Fisher, Eds. ACM, 2019, pp. 411–424. [Online]. Available: https://doi.org/10.1145/3314221.3314618

- [21] L. Lamport, "The pluscal algorithm language," in *Theoretical Aspects of Computing ICTAC 2009, 6th International Colloquium, Kuala Lumpur, Malaysia, August 16-20, 2009. Proceedings*, ser. Lecture Notes in Computer Science, M. Leucker and C. Morgan, Eds., vol. 5684. Springer, 2009, pp. 36–60.

- [22] V. Sofronie-Stokkermans, "Locality results for certain extensions of theories with bridging functions," in Automated Deduction - CADE-22, 22nd International Conference on Automated Deduction, Montreal, Canada, August 2-7, 2009. Proceedings, ser. Lecture Notes in Computer Science, R. A. Schmidt, Ed., vol. 5663. Springer, 2009, pp. 67–83.

- [23] T. Pham, A. Gacek, and M. W. Whalen, "Reasoning about algebraic data types with abstractions," *J. Autom. Reason.*, vol. 57, no. 4, pp. 281–318, 2016

- [24] S. Overflow, "Annual developer survey," 2021. [Online]. Available: https://insights.stackoverflow.com/survey/

- [25] I. T. Kassios, "Dynamic frames: Support for framing, dependencies and sharing without restrictions," in FM 2006: Formal Methods, 14th International Symposium on Formal Methods, Hamilton, Canada, August 21-27, 2006, Proceedings, ser. Lecture Notes in Computer Science, J. Misra, T. Nipkow, and E. Sekerinski, Eds., vol. 4085. Springer, 2006, pp. 268– 283.

- [26] K. R. M. Leino, "Dafny: An automatic program verifier for functional correctness," in Logic for Programming, Artificial Intelligence, and Reasoning 16th International Conference, LPAR-16, Dakar, Senegal, April 25-May 1, 2010, Revised Selected Papers, ser. Lecture Notes in Computer Science, E. M. Clarke and A. Voronkov, Eds., vol. 6355. Springer, 2010, pp. 348–370.

- [27] M. Antognini, "Extending safe C support in Leon," Master's thesis, EPFL, 2017. [Online]. Available: https://infoscience.epfl.ch/record/ 227942/

# Formal Methods for the Security Analysis of Smart Contracts

Mattei Maffei TU Wien Vienna, Austria matteo.maffei@tuwien.ac.at

Abstract—Smart contracts consist of distributed programs built over a blockchain and they are emerging as a disruptive paradigm to perform distributed computations in a secure and efficient way. Given their nature, however, program flaws may lead to dramatic financial losses and can be hard to fix. This motivates the need for formal methods that can provide smart contract developers with correctness and security guarantees, ideally automating the verification task.

This tutorial introduces the semantic foundations of smart contracts and reviews the state-of-the-art in the field, focusing in particular on the automated, sound, static analysis of Ethereum smart contracts. We will highlight the strengths and drawbacks of different methods, suggesting open challenges that can stimulate new research strands. Finally, we will overview eThor, an automated static analysis tool that we recently developed based on rigorous semantic foundations.

# Active Automata Learning: from $L^*$ to $L^\#$

Frits Vaandrager Radboud University Nijmegen, The Netherlands F.Vaandrager@cs.ru.nl

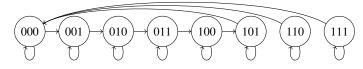

Abstract—In this tutorial on active automata learning algorithms, I will start with the famous  $L^*$  algorithm proposed by Dana Angluin in 1987, and explain how this algorithm approximates the Nerode congruence by means of refinement. Next, I will present a brief overview of the various improvements of the  $L^*$  algorithm that have been proposed over the years. Finally, I will introduce  $L^\#$ , a new and simple approach to active automata learning. Instead of focusing on equivalence of observations, like the  $L^*$  algorithm and its descendants,  $L^{\#}$  takes a different perspective: it tries to establish apartness, a constructive form of inequality.

### From Viewstamped Replication to Blockchains

Barbara Liskov MIT Computer Science & Artificial Intelligence Lab Cambridge, MA, USA liskov@csail.mit.edu

Abstract-This talk will discuss two replication protocols. The first, Viewstamped Replication, was developed in the 1980s when research on replication protocols was concerned primarily with systems that survived crash failures, e.g., individual replicas could fail only by crashing. Viewstamped replication is similar to Paxos; it was the earliest practical replication algorithm that provided the ability to execute general operations (as opposed to just reads and writes).

In the 1990s, researchers became interested in systems that could survive Byzantine failures, in which replicas fail arbitrarily. Replicated systems that survive Byzantine failures are substantially more complex, requiring both more replicas and more phases of communication, than those that survive only crash failures. The talk will present PBFT, the first practical replication technique that handles Byzantine failures. PBFT is now of great interest to researchers working on blockchains.

### Algorithms for the People

Seny Kamara Brown University Providence, Rhode Island, USA seny@brown.edu

Abstract-Algorithms have transformed every aspect of society, including communication, transportation, commerce, finance, and health. The revolution enabled by computing has been extraordinarily valuable. The largest tech companies generate a trillion dollars a year and employ 1 million people. But technology does not affect everyone in the same way. In this talk, we will examine how new technologies affect marginalized communities and think about what technology and academic research would look like if its goal was to serve the disenfranchised.

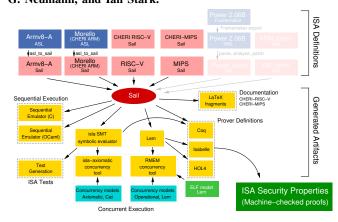

## Engineering with Full-scale Formal Architecture: Morello, CHERI, Armv8-A, and RISC-V

Peter Sewell University of Cambridge Cambridge, UK Peter.Sewell@cl.cam.ac.uk

Abstract—Architecture specifications define the fundamental interface between hardware and software. Historically, mainstream architecture specifications have been informal prose-andpseudocode documents. This talk will describe our work to establish and use mechanised semantics for full-scale instruction-set architectures (ISAs): the mainstream Armv8-A architecture, the emerging RISC-V architecture, the CHERI-MIPS and CHERI-RISC-V research architectures that use hardware capabilities for improved security, and Arm's prototype Morello architecture an industrial demonstrator incorporating the CHERI ideas.

We use a variety of tools, especially our Sail ISA definition language and Isla symbolic evaluation engine, to build semantic definitions that are readable, executable as test oracles, support reasoning within the Coq, HOL4, and Isabelle proof assistants, support SMT-based symbolic evaluation, support model-based test generation, and can be integrated with operational and axiomatic concurrency models. These models are all complete enough to boot operating systems and hypervisors, covering the full sequential ISA (though not other SoC components, such as the Arm Generic Interrupt Controller). They range from 5000 to 60000 lines of specification.

For CHERI-MIPS and CHERI-RISC-V, we have used Sail models (and previously L3 models) as the golden reference during design, working with our systems and computer architecture colleagues in the CHERI team to use lightweight formal specification routinely in documentation, testing, and test generation. We have stated and proved (in Isabelle) some of the fundamental intended security properties of the full CHERI-MIPS ISA.

For Armv8-A, building on Arm's internal shift to an executable model in their ASL language, we have the complete sequential ISA semantics automatically translated from the Arm ASL to Sail, and for RISC-V, we have hand-written what is now the offically adopted model. For their concurrent semantics, the "user" semantics, partly as a result of our collaborations with Arm and within the RISC-V concurrency task group, have become simplified and well-defined, with multiple models proved equivalent, and we are currently working on the "system"

This work was partially supported by the UK Government Industrial Strategy Challenge Fund (ISCF) under the Digital Security by Design (DSbD) Programme, to deliver a DSbDtech enabled digital platform (grant 105694), ERC AdG 789108 ELVER, EPSRC programme grant EP/K008528/1 REMS, Arm iCASE awards, EPSRC IAA KTF funding, the Isaac Newton Trust, the UK Higher Education Innovation Fund (HEIF), Thales E-Security, Microsoft Research Cambridge, Arm Limited, Google, Google DeepMind, HP Enterprise, and the Gates Cambridge Trust. Approved for public release; distribution is unlimited. This work was supported by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL), under contracts FA8750-10-C-0237 ("CTSRD"), FA8750-11-C-0249 ("MRC2"), HR0011-18-C-0016 ("ECATS"), and FA8650-18-C-7809 ("CIFV"), as part of the DARPA CRASH, MRC, and SSITH research programs. The views, opinions, and/or findings contained in this report are those of the authors and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

semantics. Our symbolic execution tool for Sail specifications, Isla, supports axiomatic concurrency models over the full ISA.

Morello, supported by the UKRI Digital Security by Design programme, offers a path to hardware enforcement of finegrained memory safety and/or secure encapsulation in the production Armv8-A architecture, potentially excluding or mitigating a large fraction of today's security vulnerabilities for existing C/C++ code with little modification. During the ISA design process, we have proved (in Isabelle) fundamental security properties for the complete Morello ISA definition, and generated tests from the definition which were used during hardware development and for QEMU bring-up.

All these tools and models are (or will soon be) available under open-source licences, providing well-validated models for others to use and build on.

This is joint work by many people, including especially, for Sail and Isla: Alasdair Armstrong, Brian Campbell, Kathryn E. Gray, Mark Wassell, Jon French, Neel Krishnaswami; for Morello verification and ASL-to-Sail translation: Thomas Bauereiss, Thomas Sewell, Brian Campbell, Alasdair Armstrong, Alastair Reid; for Morello and CHERI-MIPS test generation: Brian Campbell; for CHERI-MIPS verification: Kyndylan Nienhuis; for RISC-V and CHERI-RISC-V specifications: Robert M. Norton, Prashanth Mundkur, Jessica Clark; for MIPS and CHERI-MIPS specifications: Alexandre Joannou, Anthony Fox, Michael Roe, Matthew Naylor; and for Concurrency semantics: Christopher Pulte, Shaked Flur, Will Deacon, Ben Simner, Luc Maranget, Susmit Sarkar, Jean Pichon-Pharabod, Ohad Kammar, Jeehoon Kang, Sung-Hwan Lee, Chung-Kil Hur. All this is in collaboration with the rest of the CHERI team and others in Arm (especially Richard Grisenthwaite, Graeme Barnes, and the Morello team) and in the RISC-V community, with the CHERI team jointly led by Robert N. M. Watson, Simon W. Moore, Peter Sewell, Peter G. Neumann, and Ian Stark.

Fig. 1. Sail models and infrastructure (grayed-out models are partial ISA models in an older version of Sail)

### The FMCAD 2021 Student Forum

Mark Santolucito (D) Barnard College, Columbia University New York City, USA msantolu@barnard.edu

Abstract—The Student Forum at the International Conference on Formal Methods in Computer-Aided Design (FMCAD) gives undergraduate and graduate students the opportunity to engage with to the Formal Methods community by presenting their working and receiving feedback. The Student Forum was held in a hybrid format, with some students participating in limited in-person events in New Haven, Connecticut, USA.

The Graduate Student Forum was first introduced in 2013 to the FMCAD conference series. The goal of the Forum is to enable graduate students to attend the conference, even if they do not have a paper accepted at the main conference track. Students were attracted with an opportunity to present their on-going work to a broader scientific audience and receive valuable feedback about the research they are currently pursuing.

FMCAD 2021 hosted the ninth edition of the Student Forum. There was an open call for papers from both undergraduate and graduate students working broadly in the area of Formal Methods. In the call, students were asked to submit a 2page summary of their current research and on-going work. We received a number of high quality submissions to the Student Forum and accepted a total of 10 submissions. Reviews were based on the overall quality and novelty of work, the potential for impact of the work on the field of Formal Methods, as well as the potential positive impact on the student to have the opportunity to participate in the forum.

This year, the Student Forum allowed for the submission of joint research where two student researchers collaborated and contributed equally in the eyes of their advisors. The topics covered by the accepted submissions ranged across the field of Formal Methods, including foundational advancements as well as a variety of application domains. The accepted submissions are listed below with their respective student authors:

- Wonhyuk Choi: Can Reactive Synthesis and Syntax-Guided Synthesis Be Friends?

- Shmuel Berman: Programming-By-Example Synthesis *Programming-By-Example:* Looping Programs

- Ameer Hamza: Automated Alignment for Equivalence

- Amitash Nanda: NeuCASL: From Logic Design to System Simulation of Neuromorphic Engines

- Guy Amir: Verifying Deep Reinforcement-Learning Sys-

- Ori Lahav: Neural Network Simplification using Formal Verification

- Y. Cyrus Liu: Source-Level Bitwise Branching for Temporal Verification

- Maxwell Levatich: Using Z3 to Validate Executions of a Program Partitioner

- Priyanka Golia: Boolean Functional Synthesis and its **Applications**

- John Hui and Robert Krook: Toward Sparse Synchronous Computing on Embedded Systems

This edition of the FMCAD Student Forum follows a series of previous successful iterations of the forum [1]-[8].

We would like to thank the organizers of FMCAD, as well as the entire program committee of FMCAD, who have made the FMCAD student forum possible. Additionally, we are grateful to the student authors and their research mentors who have contributed their excellent work to the program.

#### REFERENCES

- [1] T. Wahl, "The FMCAD graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2013, Portland, OR, USA, October 20-23, 2013. IEEE, 2013, pp. 16-17. [Online]. Available: https://doi.org/10.1109/FMCAD.2013.7035523

- [2] R. Piskac, "The FMCAD 2014 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2014, Lausanne, Switzerland, October 21-24, 2014. IEEE, 2014, p. 13. [Online]. Available: https://doi.org/10.1109/FMCAD.2014.6987589

- [3] G. Weissenbacher, "The FMCAD 2015 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2015, Austin, Texas, USA, September 27-30, 2015, R. Kaivola and T. Wahl, Eds. IEEE, 2015,

- [4] H. Hojjat, "The FMCAD 2016 graduate student forum," in 2016 Formal Methods in Computer-Aided Design, FMCAD 2016, Mountain View, CA, USA, October 3-6, 2016, R. Piskac and M. Talupur, Eds. IEEE, 2016, p. 8. [Online]. Available: https://doi.org/10.1109/FMCAD.2016.7886654

- [5] K. Heljanko, "The FMCAD 2017 graduate student forum," in 2017 Formal Methods in Computer Aided Design, FMCAD 2017, Vienna, Austria, October 2-6, 2017, D. Stewart and G. Weissenbacher, Eds. IEEE, 2017, p. 10. [Online]. Available: https://doi.org/10.23919/FMCAD. 2017.8102234

- [6] D. Jovanovic and A. Reynolds, "The FMCAD 2018 graduate student forum," in 2018 Formal Methods in Computer Aided Design, FMCAD 2018, Austin, TX, USA, October 30 - November 2, 2018, N. Bjørner and A. Gurfinkel, Eds. IEEE, 2018, p. 1. [Online]. Available: https://doi.org/10.23919/FMCAD.2018.8602995

- G. Fedyukovich, "The FMCAD 2019 student forum," in 2019 Formal Methods in Computer Aided Design, FMCAD 2019, San Jose, CA, USA, October 22-25, 2019, C. W. Barrett and J. Yang, Eds. IEEE, 2019, p. 1. [Online]. Available: https://doi.org/10.23919/FMCAD.2019.8894257

- [8] P. Schrammel, "The FMCAD 2020 student forum," in 2020 Formal Methods in Computer Aided Design, FMCAD 2020, Haifa, Israel, September 21-24, 2020. IEEE, 2020, p. 1. [Online]. Available: https://doi.org/10.34727/2020/isbn.978-3-85448-042-6\_6

### COCOALMA: A Versatile Masking Verifier

Vedad Hadžić Graz University of Technology

Roderick Bloem Graz University of Technology

Abstract-Masking techniques are an effective countermeasure against power side-channel attacks. Unfortunately, correctly masking a hardware circuit is difficult, and mistakes may lead to functionally correct circuits with insufficient protection. We present COCOALMA, a tool that formally verifies the side-channel resistance of stateful hardware circuits. Although COCOALMA was initially used to verify programs running on CPUs, we extended it to verify the security of several industrial masked hardware implementations. We give an overview of the tool's structure, implementation details, optimizations that make it faster and more scalable than its predecessor REBECCA, and changes that enable verifying the probing security of any stateful hardware circuit. Finally, we evaluate COCOALMA with masked implementations of the PRINCE and AES ciphers.

Index Terms-Side-channels, Hardware masking, Formal verification

### I. Introduction

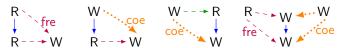

Integrated circuits that process sensitive data are susceptible to passive side-channel attacks like differential power analysis. Naturally, attackers are interested in the secret keys of symmetric ciphers because that would break the confidentiality of the processed data [22], [23], [26], [21]. Classical power analysis attacks exploit the correlation of the circuit's power consumption to bits of the secret key. Ultimately, the key is reconstructed using statistic analysis techniques in a series of key guesses [22], [27].

Masking is an algorithmic countermeasure against power analysis attacks. It relies on splitting all secrets and intermediate computations into multiple signals. The circuit is rewritten so that attackers can only reconstruct the original value if they can observe all the shares simultaneously. Masking techniques achieve this by introducing randomness into the circuit and destroying the correlation between the powertrace and the original data. Several masking schemes describe how to make circuits secure against side-channel attacks. Among them, domain-oriented masking [15] and threshold implementations [9] are well studied and widely adopted. The security of masked hardware circuits is expressed using the hardware probing model [2], [18], [4], where an attacker can read the values of d wires. Traditionally, engineers validate masked hardware implementations empirically by creating power traces and computing the correlations over many executions. Recently, however, we see several formal masking verification methods that can substantially reduce the costs of validating power side-channel resistance of software and hardware [2], [1], [11].

This work was supported by the Austrian Research Promotion Agency (FFG) through the FERMION project (grant number 867542).

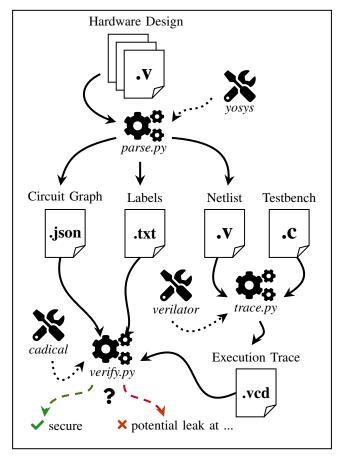

Figure 1. The workflow of COCOALMA showing the parsing, tracing, and verification phases, as well as their artifacts. At the end of the verification phase, COCOALMA either acknowledges that the analyzed design is secure or shows that a secret is leaked at a given location in the circuit.

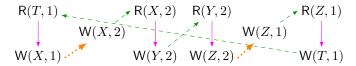

COCOALMA is an open-source masking verifier<sup>1</sup> that assisted the hardening of a RISC-V processor<sup>2</sup> so it could safely execute masked software [13]. It considers the exact description of the hardware that runs the software and accounts for hardware leakage effects such as glitches. Figure 1 shows the workflow of COCOALMA. Starting with a hardware design written in Verilog, COCOALMA uses Yosys [31] to synthesize a flat gate-level Verilog netlist. Additionally, the parsing phase extracts a circuit graph of the synthesized design and creates a labeling template where the user can specify the contents of each register and input port of the circuit after the reset.

<sup>1</sup>https://github.com/IAIK/coco-alma

<sup>&</sup>lt;sup>2</sup>https://github.com/IAIK/coco-ibex

COCOALMA uses a testbench provided by the user to simulate the netlist with Verilator [28], resulting in a *value change dump* showing how the internal signals changed throughout the execution. For the analysis of software running on RISC-V processors, COCOALMA additionally requires the RISC-V toolchain to compile programs and add them to the testbench before starting the simulation. The resulting execution trace is used to determine the value and glitching properties of each wire in the design. Afterward, the time-constrained probing model, initial state, simulation trace, and glitching information are encoded as a SAT problem and solved with CaDiCaL [3]. If the problem is unsatisfiable, no possible observation would leak any of the secrets. Otherwise, COCOALMA gives a precise description of leakage location, the secret bits that are leaked, and a variety of other debugging information.

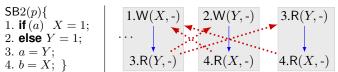

Although COCOALMA was first used for analyzing software running on CPUs [13], its roots in the older verification tool REBECCA [4] can be leveraged towards stateful hardware verification of masked cipher implementations. Luckily, all the principles used in COCOALMA also apply to hardware masking verification with minor tweaks. In this paper, we document the inner workings of COCOALMA, its features, and show the extensions necessary for applying it to cryptographic accelerator modules. We present the following details about COCOALMA's implementation:

- In Section II, we define the supported probing models, emphasizing the newly supported hardware probing model, which allows us to prove the security of stateful hardware circuits. We also discuss the support for random number generators.

- o In Section III-A, we give a breakdown of the *correlation set* methodology and show its encoding into a SAT formula in Section III-B. Here we give a precise description of the encoding, which is missing in the original publication [13], and more efficient than the encoding used in REBECCA [4]. Finally, in Section III-C, we describe details of several optimizations that reduce the size of the encoding and the number of probing locations. Here, the *hardware probing model* requires special considerations.

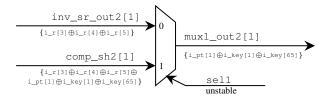

- In Section IV, we motivate and describe the execution-dependent correlation set simplifications. Additionally, we present the *stable signal detection* algorithm computing the *stability* of each control signal in Section IV-A. This optimization allows us to simplify the correlation sets even in the presence of glitches.

- o In Section V, we demonstrate COCOALMA's capabilities by verifying the probing security of state-of-the-art masked implementations of the PRINCE [6], [12], [20] and AES [30], [7], [17], [15] ciphers as they are popular in the semiconductor industry. Additionally, we go over the debugging tools provided with COCOALMA, which allow a designer to locate the source of the leakage and see how leakage propagates through the circuit.

### II. SECURITY MODELS

Masked implementations split all intermediate data signals x into d+1 uniformly random pieces  $x_i$ , with  $x=x_0\oplus\ldots\oplus x_d$ . In practice, for  $i\neq d$ , the signal shares  $x_i$  are sampled from a random number generator, whereas  $x_d$  is chosen as  $x\oplus x_0\oplus\ldots\oplus x_{d-1}$  to fit the equality. This countermeasure tries to prevent an attacker, who can observe intermediate computations through side-channels, from learning anything about the processed data. When investigating whether a masked implementation is actually side-channel resistant, several security models describe the capabilities of an attacker and the real-world effects they can observe. COCOALMA implements three different probing models that consider different attacker capabilities and system behavior. More specifically, this work extends COCOALMA to support continuous probing as part of the hardware probing model.

**Software probing model.** The original probing model defined by Ishai et al. [18] considers the stable state of computations, ignoring hardware side-effects such as glitches and transitions. Their seminal paper says that an attacker in this probing model can choose d intermediate values that they can observe. The attacker can then interactively query the execution of the system several times with different inputs and starting states. The inputs of the computation are declared either (a) public, which means that learning them does not benefit the attacker, (b) fixed uniformly random values called masks, or (c) parts of a secret called shares. The attacker's goal is to learn all the shares of a secret and use them to reconstruct the secret value they are not supposed to know. Proving that an implementation is d-probing secure requires showing that no attacker adhering to this probing model can learn the secrets, irrespective of their strategy.

Time-constrained probing model.<sup>3</sup> When COCOALMA was first presented [13], its primary goal was verifying the masking of software programs running on an accurate description of the underlying hardware. Naturally, this required an adequate probing model that translates software probing into the hardware domain. The time-constrained probing model uses the gate-level description of the hardware and an execution trace generated by simulating the hardware running the software, instead of a purely algorithmic description. The goals of the attacker are the same as in the software probing model. However, this model is more realistic, as the attacker can probe d observation tuples (g,t), where g is a logic gate or register and t is a cycle in the execution trace. This gives an attacker access to all the intermediate values of gate g in cycle t, including all the values caused by hardware effects such as glitches and register transition leakage. The two parameters g and t are not coupled, meaning that the attacker can also probe the same gate in multiple clock cycles or even probe ddifferent gates in the same clock cycle. Although this model limits each probe to observing only one clock cycle, instead of running throughout the computation, its inclusion of hardware effects significantly enhances the capabilities of an attacker.

<sup>&</sup>lt;sup>3</sup>Barthe et al. [2] and Moos et al. [24] call this the *robust probing model*.