IntechOpen

## Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications

Edited by Yogesh Kumar Sharma

# DISRUPTIVE WIDE BANDGAP SEMICONDUCTORS, RELATED TECHNOLOGIES, AND THEIR APPLICATIONS

Edited by Yogesh Kumar Sharma

#### Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications

http://dx.doi.org/10.5772/intechopen.71702 Edited by Yogesh Kumar Sharma

#### Contributors

Aaron Cai, Liter Siek, Anup Bhalla, Neophytos Lophitis, Marina Antoniou, Anastasios Arvanitopoulos, Samuel Perkins, Yaqi Wang, Fan Li, Mike Jennings, Paul Mumby-Croft, Daohui Li, Gary Liu, Andy Dai, Yogesh Kumar Sharma

#### © The Editor(s) and the Author(s) 2018

The rights of the editor(s) and the author(s) have been asserted in accordance with the Copyright, Designs and Patents Act 1988. All rights to the book as a whole are reserved by INTECHOPEN LIMITED. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECHOPEN LIMITED's written permission. Enquiries concerning the use of the book should be directed to INTECHOPEN LIMITED rights and permissions department (permissions@intechopen.com). Violations are liable to prosecution under the governing Copyright Law.

#### CC BY

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be foundat http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in London, United Kingdom, 2018 by IntechOpen eBook (PDF) Published by IntechOpen, 2019 IntechOpen is the global imprint of INTECHOPEN LIMITED, registered in England and Wales, registration number: 11086078, The Shard, 25th floor, 32 London Bridge Street London, SE19SG – United Kingdom Printed in Croatia

British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library

Additional hard and PDF copies can be obtained from orders@intechopen.com

Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications Edited by Yogesh Kumar Sharma

p. cm.

Print ISBN 978-1-78923-668-2 Online ISBN 978-1-78923-669-9 eBook (PDF) ISBN 978-1-83881-599-8

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

3,700+

115,000+

International authors and editors

119M+

151 Countries delivered to Our authors are among the Top 1%

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

## Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Meet the editor

Dr. Yogesh Sharma was born in Amritsar, India, in 1983. He received his MSc degree in Physics from the Punjab University, Chandigarh, India, in 2004. Following this, he worked as a lecturer for 3 years in a college and taught graduate-level mathematics and physics courses. Later, he moved to the USA to pursue his PhD degree. He started his integrated PhD program at the Auburn University,

AL, USA, in wide bandgap semiconductors, SiC and GaN. He completed his PhD degree in 2012 and ever since has been working in wide bandgap semiconductor technology. He has authored/coauthored over 50 journal/ conference papers. He is the holder of one patent and is a reviewer of various international journals. He is a member of IEEE and IET.

## Contents

#### Preface XI

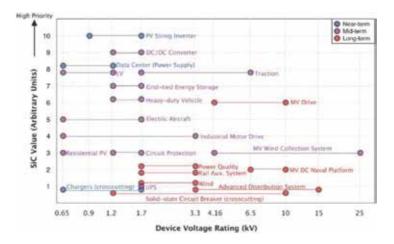

| Chapter 1 | Introductory Chapter: Need of SiC Devices in Power Electronics |

|-----------|----------------------------------------------------------------|

|           | - A Beginning of New Era in Power Industry 1                   |

|           | Yogesh K. Sharma                                               |

- Chapter 2 **TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors 17** Neophytos Lophitis, Anastasios Arvanitopoulos, Samuel Perkins and Marina Antoniou

- Chapter 3 Main Differences in Processing Si and SiC Devices 45 Fan Li and Mike Jennings

- Chapter 4 High-Performance Packaging Technology for Wide Bandgap Semiconductor Modules 65 Paul Mumby-Croft, Daohui Li, Xiaoping Dai and Guoyou Liu

- Chapter 5 Status of SiC Products and Technology 85 Anup Bhalla

- Chapter 6 GaN-Based Schottky Diode 103 Yaqi Wang

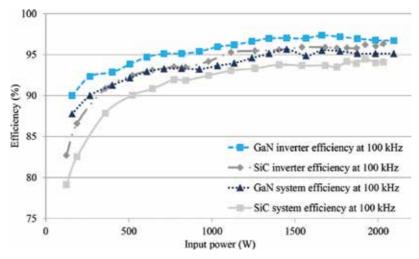

- Chapter 7 Inductive Power Transfer for Electric Vehicles Using Gallium Nitride Power Transistors 123 Cai Qingwei Aaron and Siek Liter

### Preface

Devices fabricated from wide bandgap semiconductors such as SiC and GaN are considered to be a third generation of semiconductor devices. These devices will change the power industry significantly in the near future. High-electric field of breakdown, low-intrinsic carrier concentration, and high-bandgap mean that the devices fabricated from these materials can outperform their Si counterparts in high-power regimes and hence enable engineers and researchers to build more efficient electrical systems. At present time, more efficient electrical systems are necessary to limit the amount of  $CO_2$  emissions and make the planet greener. In this book, we try to cover the main aspect of SiC and GaN technologies. The book is organized in the following manner.

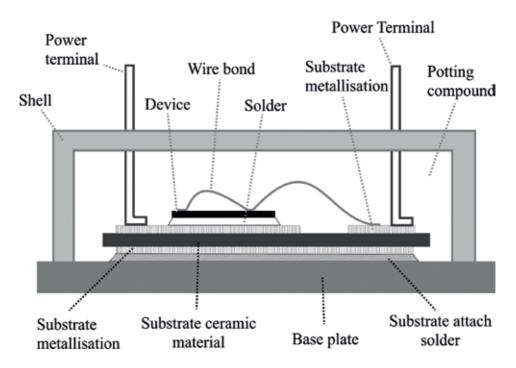

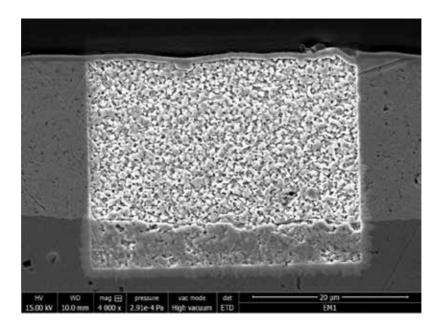

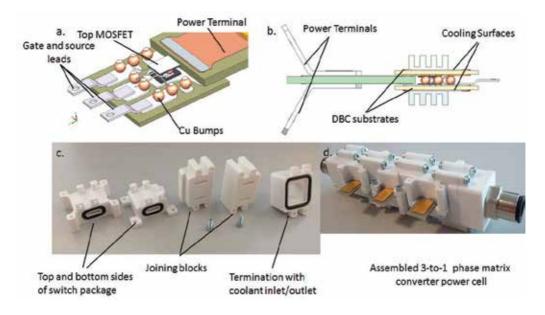

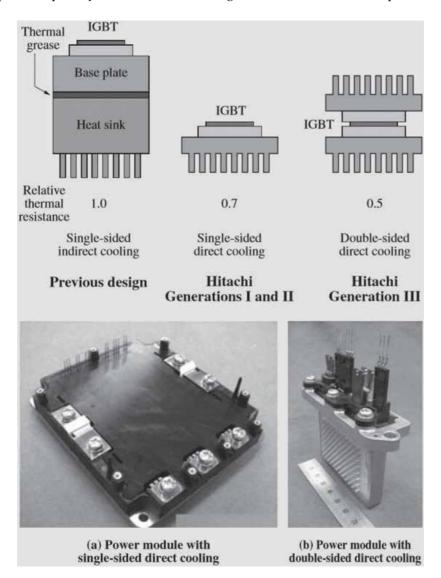

The introductory chapter deals with the basics of power devices and explains why it is advantageous to use SiC devices in power electronics. The use of SiC devices in hybrid SiC technology is demonstrated, and the issues related to it are addressed. Challenges such as the quality of the oxide-SiC interface and ohmic contacts on SiC are also discussed briefly in this chapter. The second chapter covers an in-depth analysis of the main differences of, while developing the simulation platforms for, these technologies using technology computer-aided design (TCAD) tools. Most of the tools that have been established are more suitable for Si technology, so special attention is needed while using them to develop wide bandgap semiconductor devices. The third chapter highlights the processing aspects of SiC devices. This chapter addresses the questions such as why SiC devices need a special set of expertise and tools for fabrication and why they are more expensive, and so on, as compared to their Si counterparts. The fourth chapter focuses on the development of packaging technology for power semiconductor devices. Packaging technology such as Ag sintering, copper wire bonding, and wire bond-free and planar modules with low inductance is discussed in this chapter. In Chapter 5, the current stage of SiC devices is summarized. The evolution of SiC devices, including different types, and market response to these devices is discussed. Also, this chapter addresses some practical challenges, which engineers have to face while using these devices.

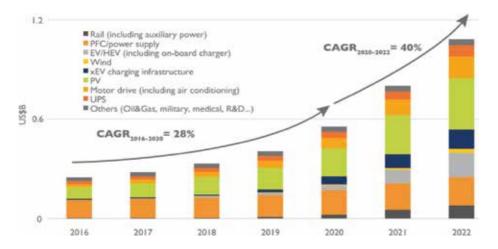

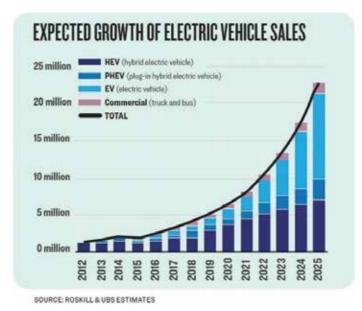

The last two chapters deal with GaN technology. Chapter 6 reviews the state-of-the-art GaN Schottky diode technology. This chapter covers the background of GaN-based Schottky diodes, current transportation theory, Schottky material selection, contact quality, and thermal stability of Schottky contact to GaN. This chapter also discusses the evolution of epitaxial and device structures of the GaN-based lateral, quasi-vertical, and vertical Schottky diodes as well as AlGaN/GaN field effect Schottky diodes. Also, this chapter gives a viewpoint on the forth-coming development of GaN-based Schottky diodes. The last chapter, Chapter 7, deals with the application of GaN devices in electric vehicles (EVs). It presents the application of the GaN gate injection transistor (git) in inductive power transfer (ipt) for electric vehicles.

The chapters in this book have been contributed by the respected researchers and technology experts and cover up-to-date developments in wide bandgap semiconductor technology. I hope that graduate students, researchers, engineers, and technology experts who have been working in the exciting field of SiC and GaN power devices will find this book useful.

I would like to thank all the contributors for their hard work and support during this project. Special thanks go to Ms. Dajana Pemac of IntechOpen for her assistance and guidance during the writing of this book.

My greatest acknowledgement goes to my father (Jagdish Ram Sharma) and mother (Kusum Sharma) who have taught me to be a good person and respect all. I would like to thank my brother (Munish Sharma) and sister (Monika Sharma) from whom I have learned a lot throughout the life. Special thanks go to my beloved wife (Vasudha Dewan) and daughter (Ayana Sharma) for their love and patience during this work. Without my wife's encouragement, I would not have had started working on this project.

Yogesh Kumar Sharma R&D Centre: Semiconductors Dynex Semiconductor Ltd. Lincoln, United Kingdom

## Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era in Power Industry

Yogesh K. Sharma

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.79487

#### 1. Introduction

#### 1.1. Development in device technology

Germanium (Ge) was used as a material to manufacture the first semiconductor device. Ge was touted as the semiconductor material of the future. But after the arrival of silicon (Si), it turned out to be more suitable for several reasons [1–4]. The main reason is to get the high-purity Si from silica, which is widely available. Also, it is easy to modify Si into n-type, p-type, and semi-insulating materials [5]. In addition to this, Si can easily be converted into its native oxide,  $SiO_{2'}$  with the help of thermal oxidation at the relatively low temperature of around 900°C [6–8]. These features make Si, as a material, semiconductor industry favorite. Global semiconductor industry, and currently, is worth more than \$430 billion [9]. Around 9–10% of this worth is in smart-integrated circuits and electronic power devices [10, 11]. These power devices processed more than 50% of our electricity [12, 13]. It has been reported that by 2025, Power Electronics market size will be worth \$39.22 billion [9]. As we can envision, power devices have a larger impact on the economy of any country. Power semiconductor devices are crucial to determine the cost and efficiency of electronic systems.

In power systems, diodes (uncontrolled switch) and transistors (controlled switch) play a major role. A small increase in their efficiency and power-handling capability make the systems more powerful and energy efficient. In the early 1950s, the advent of solid-state devices like bipolar transistors led to the phasing-out of vacuum tubes [13, 14]. These Si devices created the second wave of electronic revolution possible, with Si as the material of choice. Power devices had played a vital role in electronics industry. There is a rich history about the evolution of power devices. Initially, there were only bipolar devices with a blocking capability of 500 V (or so) and high-current capabilities. But after sometime, in the 1970s, International

### IntechOpen

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

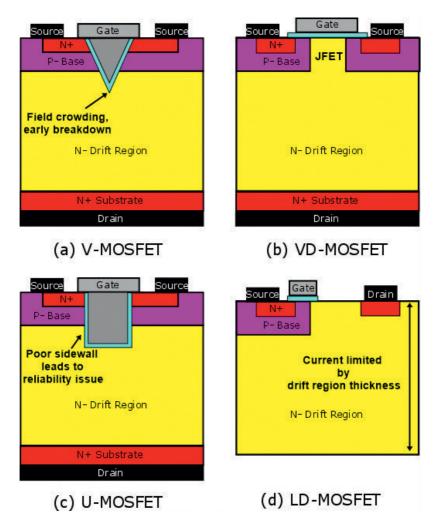

Rectifier Inc. launched the first metal-oxide-field effect transistor (MOSFET) [15]. The idea was to switch to MOSFETs from BJTs in high-power applications. The MOSFET is a unipolar device, meaning there is only one type of carriers (electrons) which participate during conduction and thus has a high switching speed. Another advantage the MOSFET has is a voltage control device and hence it is easy to switch (on-state to off-sate). On the other hand, the BJT is a current control device and as a result not so easy to control. Voltage control instead of current control means that less internal energy loss occurs in a device. Also, with an increasing switching speed, other components of the system like filters (consist of capacitors/inductors) can be reduced in size. Si-MOSFETs could be designed to handle voltages up to 1000 V and in special case (super-junction) to 1200 V [13, 16, 17]. At voltages higher than 1000 V, the on-state losses of silicon MOSFET start increasing drastically and hence no longer able to perform efficiently. The performance predicament between bipolar and MOSFET devices was solved with the invention of an insulated gate bipolar transistor (IGBT). This is a new device structure where the best electrical features of bipolar (BJT) and unipolar (MOSFET) devices were combined together. With this new device structure, it is possible to cover the blocking voltage range from 750 to 6500 V. Like BJTSs, IGBTs are also able to carry high-forward current.

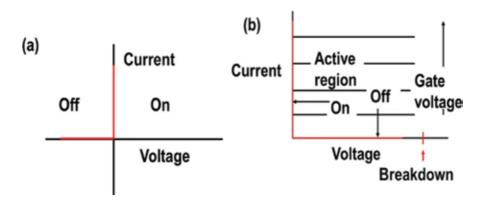

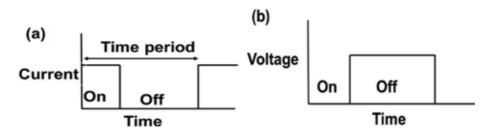

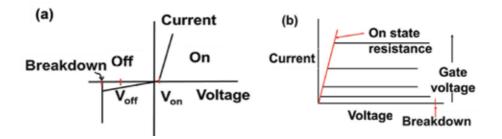

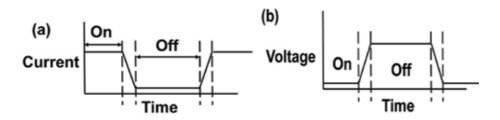

#### 1.2. Diode and transistor

In power electronics to build electrical systems, we need both a rectifier and a transistor. The features of an ideal rectifier and a transistor are shown in **Figure 1**. For an ideal rectifier, there is no voltage drop in on-state and no current flows in off-state. Hence, there is no power loss during the operation of a rectifier, **Figure 1(a)**. Similarly, in the case of an ideal transistor, there is no power dissipation during commutation from on- to off–states, **Figure 1(b)**. The waveforms of an ideal power switching system are shown in **Figure 2**. But in reality, this is not the case, either with devices or power systems. The characteristics of a real (non-ideal) rectifier/transistor are shown in **Figure 3**, and the corresponding waveforms of a power system are shown in **Figure 4**. The total power loss occurred in a switch (P<sub>Total</sub>) and is given by:

$$P_{\text{Total}} = \Sigma P = P_{\text{conduction}} + P_{\text{on}} + P_{\text{off}} = P_{\text{turn-on}} + P_{\text{turn-off}} + P_{\text{on}} + P_{\text{off}}$$

(1)

Figure 1. Ideal current-voltage characteristics of a diode (a) and a transistor (b).

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 3 http://dx.doi.org/10.5772/intechopen.79487

Figure 2. Switching waveforms of an ideal power system, (a) Current versus Time and (b) Volatge versus Time.

Figure 3. Real (nonideal) current-voltage characteristics of a diode (a) and a transistor (b).

Figure 4. Switching waveforms in a real (nonideal) power system, (a) Current versus Time and (b) Volatge versus Time.

At high frequencies, the switching power loss dominates, so fast switching power devices are desirable. At low frequencies, on-state power loss dictates, so power devices with a low on-state resistance are vital.

#### 1.3. Conduction mechanism of a power device

As mentioned previously with the help of an IGBT, it is possible to increase the operating voltage range of a power transistor without compromising its on-state losses. In unipolar devices like Schottky diode (SBD), MOSFET, the blocking capability of the device increases with an increasing drift region thickness. With an increasing thickness, the conduction losses of a device also increase. In a bipolar device, because of conduction modulation (injection of minority carriers (holes mainly) into the n-type drift region), this is not true, and the conduction losses are low despite a thick drift layer. For example, the specific on-resistance (R<sub>pin</sub>) of a drift layer (blocking layer) for a unipolar device, n-type Schottky diode', is given by [18].

$$R_{\rm pin} = T_{\rm drift} / q N_{\rm drift} \left( \mu_{\rm n+} \, \mu_{\rm p} \right) \tag{2}$$

where  $T_{drift}$  = thickness of the drift layer;  $N_{drit}$  = doping concentration of the n drift layer;  $\mu_n/\mu_p$  = bulk mobility of electrons/holes in semiconductor.

For an n-type pin diode, the specific on-resistance  $(R_{pin})$  under high-current density condition is given by

$$R_{pin} = T_{drift} / q\mu_n N_{drift} + q (\mu_{n+} \mu_p) \Delta p$$

(3)

Because of the extra term, q ( $\mu_{n+} \mu_p$ )  $\Delta p$ , in the pin diode, the specific resistance will be lower as compared to Si Schottky diode. In the case of high injection  $\Delta p >> N_{drift'}$  the resistance will decrease considerably during conduction. Now, in order to get the diode into the blocking mode, minority carriers (corresponding to  $\Delta p$ ) have to be removed from the drift region. These minority carriers in the drift region cause stored charge in the device and hence increase the switching losses. As a result, the operating switching frequency limit for bipolar devices (PIN or BJT) is lower, as compared to unipolar device (SBD or MOSFET). With the help of a wideband semiconductor material like SiC, there is no need to switch to Si IGBT, as we can realize a high-blocking capability (>1200 V) SiC MOSFET without increasing the on-state losses. The specific on-résistance ( $R_{op}$ ) of a MOSFET is given by [19, 20].

$$R_{on} = 4 V_{blocking}^2 / \mu_n \varepsilon_s E_{critical}^3$$

(4)

where  $\mu_n$  = bulk mobility of SiC;  $\varepsilon_s$  = permittivity of SiC;  $E_c$  = critical electric field of breakdown for SiC;  $V_{blocking}$  = the desired blocking voltage.

Bulk electron motilities are similar for low-doped Si and SiC (900–1200 cm<sup>2</sup>/Vs) [24]. However,  $E_{critical}^{SiC} = 7 E_{critical}^{Si}$ , so that for a given blocking voltage, the specific on-resistance can be a factor of 343 times lower for SiC devices. This is the reason why we need a wide-band gap semiconductor material for power device.

#### 2. Application of SiC devices in hybrid module technology

There are a plethora of applications where these devices had been used and have shown their positive impact, and many more potential applications are on the horizon [21–23]. Although there are different kinds of SiC devices available, the most interesting ones are Schottky diodes and MOSFETs. These devices can be used to build either full SiC modules or hybrid SiC modules. In a hybrid SiC module, conventional Si diodes are replaced by Schottky diodes while the transistors are still Si IGBTs. With hybrid approach, we can maintain the cost of an electronic system down but the power saving would not be as much as it can be by using full SiC modules. The fabrication of SiC devices is more complicated and costly as compared with Si counterparts. The situation is more compounded for SiC MOSFETs. SiC MOSFETs are not only more expensive than SiC Schottky diodes but also there are only few suppliers who can provide these devices with limited current ratings. As a result, it makes more sense to build

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 5 http://dx.doi.org/10.5772/intechopen.79487

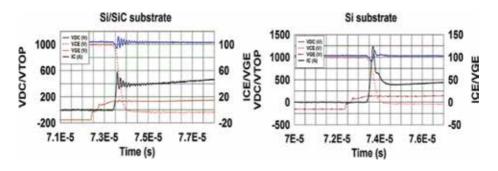

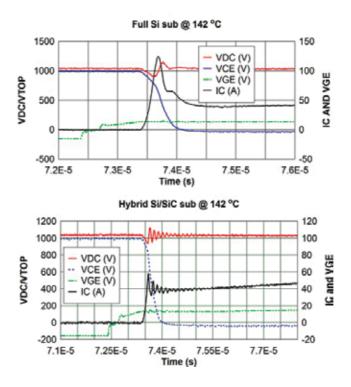

**Figure 5.** Output waveforms obtained for hybrid 1.7 kV SiC (a) and Si substrates (b) obtained during the first turn-on of the IGBT. These devices were tested at 150°C.

hybrid systems. Also at present, hybrid approach strikes a good balance between cost and efficiency achieved by these modules [24–27]. Also, it is worthwhile to point out that although SiC diodes and MOSFETs are available at 1.7 kV and lower voltages, there is no MOSFET supplier at 3.3 kV. Also, SiC diode technology is more matured and has been around for some time as compared to SiC MOSFETs. SiC diodes were made available commercially in early 2000s, while the first SiC MSOFET came to the market in 2011 (by CREE).

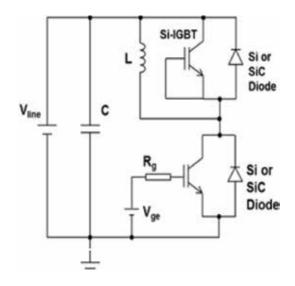

#### 2.1. 1700 V Si/SiC hybrid technology

The results of a double-pulse test done on a hybrid substrate, built using 1 GBT and 1 diode (Si or SiC), are shown in **Figure 5**. These substrates are manufactured to conduct only 50A. By executing this test, we can evaluate the transient behavior of both IGBT and diode. In our case, we are interested in SiC Schottky diode's transient behavior and power losses suffered by it. The external gate resistors,  $R_{gon} = R_{gotf} = 6 \Omega$ , and the value of inductance (L) used is 260 µH. The waveforms during the second turn-on of the IGBT are recorded and are shown in **Figure 5**. The input voltage used for the test is around 1050 V. **Figure 5** shows that the peak reverses recovery current overshoot ( $I_{rr}$ ) increases significantly to 87A, if Si diode is used instead of an SiC diode. The values of  $I_{rr}$  for Si and hybrid SiC substrates are listed in **Table 1**. Although the value of  $I_{rr}$  is lower for hybrid substrate, some oscillations in the current waveform are observed. The reverse recovery charge,  $Q_{rr'}$  is minute ( $3\mu$ C) in the case of SiC diode. This low  $Q_{rr}$  can be transformed into a low-energy loss during a switching event. Also, for hybrid SiC substrate, the reverse recovery energy ( $E_{rec'}$ ) is 1 mJ. The corresponding value for Si substrate is 11 mJ. All these tests are done at 150°C. The test setup used to perform a double-pulse test is shown in **Figure 6**.

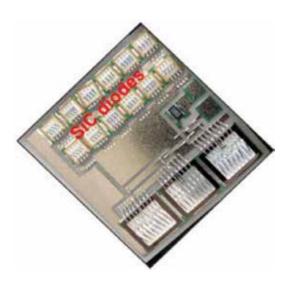

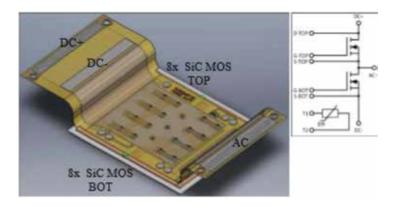

#### 2.2. 3300 V Si/SiC technology

In order to build 3.3 kV hybrid SiC substrates, two 1.7 kV, 50 A diodes are packaged in series. Again, the idea of using these diodes is to reduce the overall losses as compared with Si modules. These 3.3 kV modules can be used in wind power, solar energy, and rail-car applications. Like 1.7 kV hybrid modules, new system topologies can be realized with the help of these modules. Because of the limited availability of 3.3 kV SiC diodes, 1.7 kV SiC diodes are used to realize this high-voltage hybrid technology. All the diodes used to build these substrates are chosen carefully (e.g., the devices with similar  $V_F$ ) so that there is no problem during current sharing in SiC diodes. This is very crucial for the reliability of these substrates. The waveforms

| At 150 °C, 1.7kV            | Full Si | Hybid Si/SiC |

|-----------------------------|---------|--------------|

| V <sub>line</sub> (V)       | 1049    | 1056         |

| dV <sub>ce</sub> /dt (V/µs) | 1372    | 1319         |

| Irr (A)                     | 87      | 21           |

| Q <sub>rr</sub> (µC)        | 22      | 3            |

| Erec (J)                    | 0.011   | 0.001        |

Table 1. Comparison of various parameters extracted for Si and hybrid 1.7 kVSiC substrates at 150°C from a doublepulse test.

Figure 6. The schematic of a double-pulse test bench used to test devices.

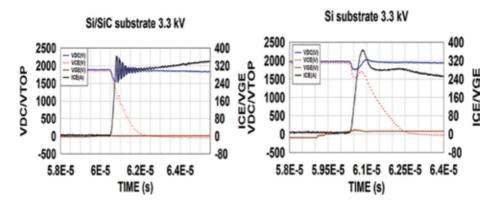

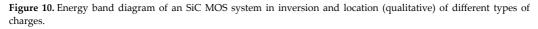

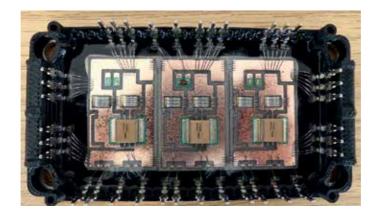

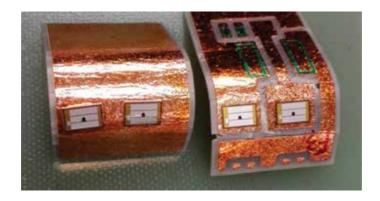

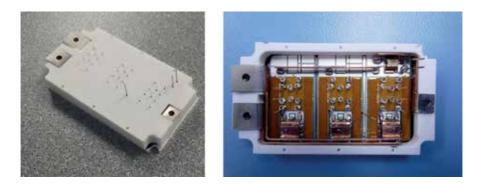

during the second turn-on of the IGBT at 150°C are recorded and are shown in **Figure 7**. For a di/dt = 1100 or 1388 A/µs, a reverse recovery current overshoot ( $I_{rr}$ ) of 128 A is observed for an Si substrate, which is higher than that of a hybrid SiC substrate (65A). The reverse recovery energy loss occurred in a substrate during the transient is  $E_{rec'}$  and the values for  $E_{rec}$  (Si) and  $E_{rec}$  (SiC) are 0.199 and 0.01 J, respectively. This represents a reduction of about 95% for hybrid substrate. Other transient parameters for the substrates, namely  $Q_{rr'}$   $E_{on}$ , and  $E_{off}$  (J), are also listed in **Table 2**. **Figure 8** shows the picture of a 3.3 kV, 200A hybrid SiC substrate. Again, like 1.7 kV hybrid substrates, 3.3 kV hybrid substrates are prone to electromagnetic interference (EMI), caused by the oscillations observed in the output waveforms.

#### 3. Processing challenges of SiC devices

The fabrication of SiC devices is more demanding and complicated as compared with Si devices. Intrinsic properties of SiC make the devices suitable for high operating temperatures

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 7 http://dx.doi.org/10.5772/intechopen.79487

**Figure 7.** Output waveforms obtained for hybrid 3.3 kV SiC (a) and Si substrates (b) obtained during the first turn-on of the IGBT. These devices were tested at 150°C.

| At 150 °C, 3.3kV            | Full Si | Hybid Si/SiC |

|-----------------------------|---------|--------------|

| V <sub>line</sub> (V)       | 1800    | 1800         |

| dl <sub>ce</sub> /dt (A/µs) | 1100    | 1388         |

| Irr (A)                     | 128     | 65           |

| Q <sub>rr</sub> (µC)        | 167     | 13           |

| E <sub>rec</sub> (J)        | 0.199   | 0.01         |

Table 2. Comparison of various parameters extracted for Si and hybrid 3.3 kVSiC substrates at 150°C from a double-pulse test.

(>200°C). But at the same time, due to its intrinsic properties, it is difficult to perform any electrical and physical change to the material at temperatures lower than 1000°C. That means in order to fabricate an SiC device, different set of tools are required as compared to Si device world [28–31]. The electrical and physical properties of Si and SiC are listed in **Table 3**.

#### 3.1. Oxidation of SiC

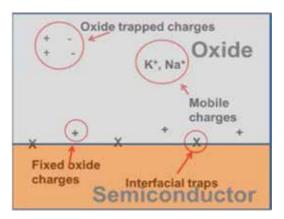

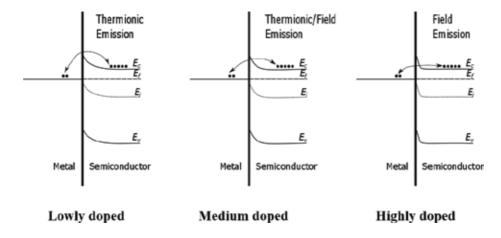

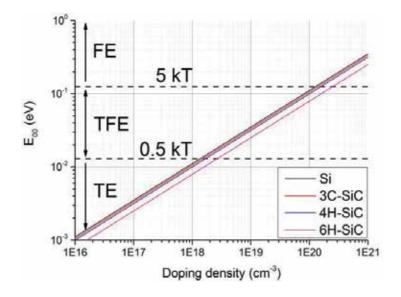

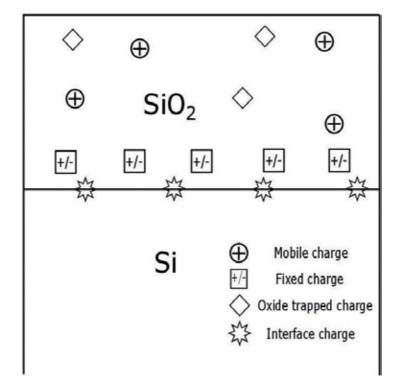

In an oxide/semiconductor system, there are different types of charges which are present in the system. These charges are not desirable and greatly influence the electrical properties of a device. For example, the threshold voltage of a MOSFET and the breakdown voltage of a power, device, could change significantly because of these charges. These charges are divided into four types—mobile oxide charge, fixed oxide charge, oxide trapped charge, and interface trapped charge—and are shown in **Figure 9** [32].

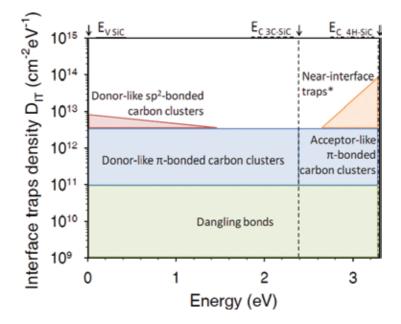

At present, interface trapped charge is a key hurdle for the silicon carbide MOS R&D community. The origin of these charges is not well understood but may be related to mainly siliconand carbon-dangling bonds, carbon clusters, carbon dimers in the SiC, and oxygen vacancies in the oxide very near to the interface [33–36]. Interfacial traps create localized energy levels in the energy band gap of SiC. These interface traps form potential wells that capture electrons

Figure 8. A picture of a 200 a, 3.3 kV hybrid SiC substrate.

| Semiconductor                                                           | Si      | 3C-SiC | 6H-SiC                                                 | 4H-SiC                                                    |

|-------------------------------------------------------------------------|---------|--------|--------------------------------------------------------|-----------------------------------------------------------|

| Bandgap (eV)                                                            | 1.12    | 2.4    | 3.03                                                   | 3.26                                                      |

| Breakdown Field<br>(MV/cm)                                              | 0.25    | >1.5   | 2.4 parallel to c-axis<br>> 1, perpendicular to c-axis | 2.2 parallel to c-axis                                    |

| Intrinsic Carrier<br>Conc.(cm <sup>-3</sup> )                           | 1.45e10 | 1.5e-1 | 1.6e-6                                                 | 5e-9                                                      |

| Electron Mobility<br>@ n <sub>d</sub> =10 <sup>16</sup> cm <sup>3</sup> | 1430    | 800    | 60 parallel to c-axis<br>400 perpendicular to c-axis   | 900 parallel to c-axis<br>800 perpendicular to c-<br>axis |

| Hole Mobility , @ n <sub>a</sub><br>=10 <sup>16</sup> cm <sup>-3</sup>  | 480     | 40     | 90                                                     | 115                                                       |

| Saturated Electron Vel<br>(10 <sup>7</sup> cm/s)                        | 1       | 2.5    | 2                                                      | 2                                                         |

| Thermal Conductivity<br>(W/cm-K)                                        | 1.5     | 3.2    | 3.0-3.8                                                | 3.0-3.8                                                   |

Table 3. Electrical and physical properties of Si, 3C-SiC, 6H-SiC and 4H-SiC.

and holes. In addition, charge traps also act as Columbic scattering centers [37]. These two effects decrease the effective channel mobility in a MOSFET. In Si world, a typical oxidation temperature employed to grow an oxide layer is 1050 (dry oxidation) or 850°C (wet oxidation). The oxidation step is followed by an annealing step in  $H_2$  gas ambient at 800°C for 30 min. In 4H-SiC, typical oxidation temperature to grow a layer of native oxide is 1150°C. In some cases, it could be as high as 1300 or 1500°C which requires special oxidation furnaces, not the conventional quartz furnaces used for Si oxidation [38–41]. To use SiC devices to their full potential, we must continue to work to improve the electrical characteristics of the oxide/SiC

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 9 http://dx.doi.org/10.5772/intechopen.79487

Figure 9. Different types of charges in oxide/semiconductor system [10].

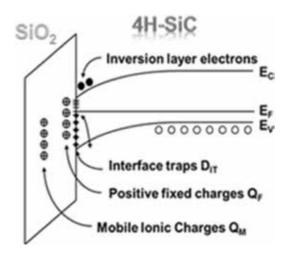

interface by developing more effective processes to passivate defects at the interface formed during the oxidation process. These defects give rise to interface trap density,  $D_{IT}$  (cm<sup>-2</sup> eV<sup>-1</sup>) and is shown in **Figure 10**. Depending upon the surface potential, these traps can be charged positively or negatively charged.

As mentioned previously, these traps decrease the effective channel mobility of electrons significantly. At present, there is a standard passivation process based on post-oxidation annealing in nitric/nitrous oxide (NO/N<sub>2</sub>O) for 2 h at 1175°C. [42, 43]. This post-oxidation annealing (passivations) increases the inversion electron channel mobility of an SiC-MOSFET from single digits, ~ 8 cm<sup>2</sup>V<sup>-1</sup>·s<sup>-1</sup>, to around 30 cm<sup>2</sup>/V·s. Although these processes have made the commercialization of SiC MOSFETs possible, there is still room for significant improvement. This inversion channel mobility value is only around 4% of bulk mobility value of SiC. In case of Si, the inversion channel mobility can be as much as 50% of bulk mobility [29]. In addition to standard  $N_2O$  annealing, there are different types of annealing which can increase the channel mobility significantly, but these annealings degrade some important parameters of a MOSFET and hence cannot be used [44–50]. More work is still needed in this field to improve the performance of SiC MOSFETs.

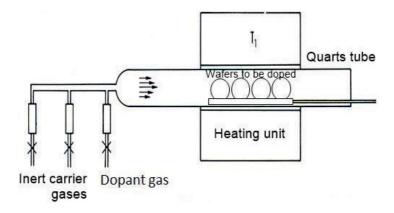

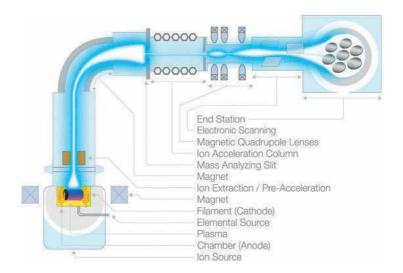

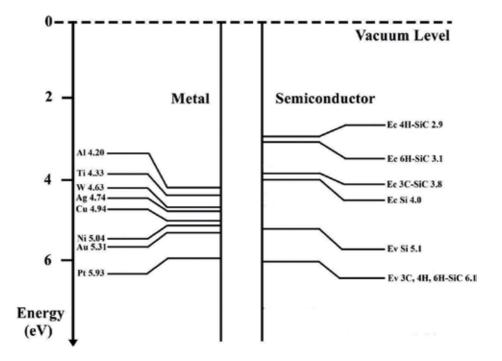

#### 3.2. Ohmic contacts

In SiC, there is no or very little diffusion as a result, it is not possible to use temperature annealing process to drive in the dopants into the material. To get a desired doping profile in SiC, dopants are implanted using a high-energy implanter (typically 50–500 keV), and sometimes, wafers are needed to be at high temperature (~500°C) during this step. Implantation of dopants is followed by a dopant activation step, which requires a very high temperature. Typically, n-dopants get electrically activated at 1550°C, while p-dopants require a temperature of as high as 1700°C, which is very challenging to achieve. With n-dopants, the electrical activation rate of more than 90% can be attained, but in p-dopants, it is tough to realize an activation rate of more than 50%. The reason why lower activation temperature is required for n-dopants as compared to p-dopants is because of the difference in the location of respective dopant energy levels in SiC. For n dopants (N), the donor energy level is located at 0.3 eV (shallow) below the conduction band edge and hence not much energy is required to electrically activate these donors. In the case of p dopants (Al), the position of the acceptor level is 0.7 eV (deep) above the valance band edge. Hence, more energy is needed to electrically activate them. Even at present, various research groups are working on p-type ohmic contacts [51–56]. Also, high temperature and special metallization processes are necessary to form ohmic and Schottky contacts on SiC.

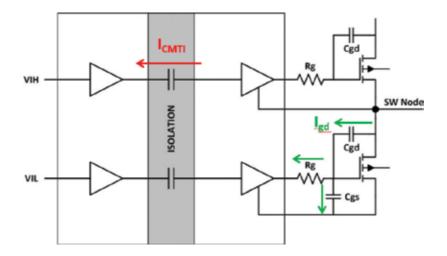

#### 4. EMI problems

Due to fast switching speed of SiC devices (Schottky diodes, MOSFETs), some undesirable effects are observed during the switching (from on-state to off-state and vice versa) of these devices. The oscillations observed in the output current waveform, Figure 11, are the result of the fast switching behavior of 1.7 kV, 50 A SiC diodes, which are used to build 3.3 kV, 1200 A hybrid SiC modules. From the application point of view, this is problematic and can lead to EMI with neighboring electrical systems. Sometimes, it can also lead to a premature breakdown of the module during operation. In full SiC module, it is common measure to slow the switching speed of the devices (by increasing the gate resistance) to reduce/eliminate the oscillations. From Figure 11, we can clearly see that the oscillations are present, both in current and in voltage waveforms. Also, these oscillations are present in the gate signal, which is used to control Si IGBT (clear from the inset in Figure 11) in the module. Because of these oscillations, the gate signal voltage in some cases may shoot up/down to +40 to -40 V, much higher than the recommended voltage range (-15 to +15 V) of the gate signal. We can imagine how detrimental this would be for Si IGBTs. If new design ideas are used for the substrate layout of these modules, then the parasitic elements (stray inductance and capacitance) could be minimized, and, hence, there will be no necessity of compromising on the switching speed of SiC devices.

Figure 11. The ringing/oscillations observed in the output waveforms of a 3.3 kV, 1200A SiC hybrid module due to an underdamped response to an RLC circuit formed among the diode depletion capacitance, parasitic inductance, and SiC diode during the second turn-on event.

#### 5. Conclusions

SiC device technology has a promising future. Different types of more efficient power systems have already been built using SiC devices and demonstrated in real applications around the world. This technology materializes the possibility of new topologies for inverter and converter, which were not possible in the past. Various fields including automotive, traction-train, renewable energy, geothermal energy, and so on have already been benefitted from SiC technology. Despite all these advantages, this technology is relatively new and hence poses some challenges. New control strategies, and more suitable module designs and packaging options are needed to be developed for the optimal use of these devices. The cost of SiC device is still a bit high, although, in the past couple of years, it has come down significantly. Even with all these challenges, new technology like SiC is indispensable to achieve the goal of a greener planet.

#### Acknowledgements

The author would like to thank his collogues at Dynex Semiconductors for their help and support provided, during this project. Also, I would like to specially thank my old colleagues and partners at the University of Warwick (UK) and Auburn University (USA).

#### Author details

Yogesh K. Sharma

Address all correspondence to: aceyogesh83@gmail.com

R&D Centre: Semiconductors, Dynex Semiconductor Ltd., Lincoln, UK

#### References

- Pfann WG, Scaff JH. The p-germanium transistor. Proceedings of the IRE. 1950;38(10): 1151-1154

- [2] Valdes LB. Effect of electrode spacing on the equivalent base resistance of point-contact transistors. Proceedings of the IRE. 1952;40(11):1429-1434

- [3] Ball JA. The Harvard minicorrelator. IEEE Transactions on Instrumentation and Measurement. 1973;22(2):193-196

- [4] Lécuyer C. Making Silicon Valley: Innovation and the Growth of High Tech. Cambridge, Massachusetts, USA; MIT Press; 2006. pp. 1930-1970

- [5] O'Mara W, Herring RB, Hunt LP. Handbook of Semiconductor Silicon Technology. Park Ridge, NJ, USA: Noyes Publications; 1990

- [6] Deal BE, Grove AS. General relationship for the thermal oxidation of silicon. Journal of Applied Physics. 1965;36(12):3770-3778

- [7] Mott NF, Rigo S, Rochet F, Stoneham AM. Oxidation of silicon. Philosophical Magazine Part B. 1989;60(2):189-212

- [8] Kao DB, Mcvittie JP, Nix WD, Saraswat KC. Two-dimensional thermal oxidation of silicon. II. Modeling stress effects in wet oxides. IEEE Transactions on Electron Devices. 1988;35(1):25-37

- [9] https://www.prnewswire.com/news-releases/global-semiconductor-market-forecast-2017-2024-300541299.html

- [10] http://www.icinsights.com

- [11] http://www.electroiq.com/articles/sst/print/volume-54/issue-7.html

- [12] http://www.power-mag.com/news.detail.php?NID=38

- [13] Baliga BJ. Fundamentals of Power Semiconductor Devices. USA: Springer Science & Business Media; 2010

- [14] Warner RM. Microelectronics: Its unusual origin and personality. IEEE Transactions on Electron Devices. 2001;48(11):2457-2467

- [15] http://www.irf.com/60anniversary/index.html#1970s

- [16] Lin Z, Hu S, Yuan Q, Zhou X, Tang F. Low-reverse recovery charge superjunction MOSFET with a p-type Schottky body diode. IEEE Electron Device Letters. 2017;38(8):1059-1062

- [17] Udrea F, Deboy G, Fujihira T. Superjunction power devices, history, development, and future prospects. IEEE Transactions on Electron Devices. 2017;64(3):720-734

- [18] Morisette DT, Cooper JA. Theoretical comparison of SiC PiN and Schottky diodes based on power dissipation considerations. IEEE Transactions on Electron Devices. 2002;49(9):1657-1664

- [19] Baliga BJ. Trends in power semiconductor devices. IEEE Transactions on Electron Devices. 1996;43(10):1717-1731

- [20] Sharma Y. Advanced SiO<sub>2</sub>/SiC interface passivation [doctoral dissertation]; 2012

- [21] She X, Huang AQ, Lucía O, Ozpineci B. Review of silicon carbide power devices and their applications. IEEE Transactions on Industrial Electronics. 2017;64(10):8193-8205

- [22] Piasecki S, Kazmierkowski MP. Applications of SiC MOSFETs in AC–DC converters dedicated for distributed generation systems. In: Analysis and Simulation of Electrical and Computer Systems. Cham: Springer; 2018. pp. 1-14

- [23] Morya A, Moosavi M, Gardner MC, Toliyat HA. Applications of wide bandgap (WBG) devices in AC electric drives: A technology status review. In: 2017 IEEE International Electric Machines and Drives Conference (IEMDC); IEEE. 2017. pp. 1-8

- [24] Ishikawa K, Ogawa K, Yukutake S, Kameshiro N, Kono Y. Traction inverter that applies compact 3.3 kV/1200 A SiC hybrid module. In: 2014 International Power Electronics Conference (IPEC-Hiroshima 2014-ECCE-ASIA); IEEE. 2014. pp. 2140-2144

- [25] Yuan L, Li J, Gu Q, Zhao Z, Shen Y. Power losses of Si/SiC semiconductors in medium voltage energy router sub-modules with hybrid topology. In: 2017 20th International Conference on Electrical Machines and Systems (ICEMS); IEEE. 2017. pp. 1-6

- [26] Kranz L, Minamisawa RA, Knoll L, Matthias S, Mihaila A, Papadopoulos C, et al. Robust SiC JBS diodes for the application in hybrid modules. In: Proceedings of PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; VDE. 2017. pp. 1-6

- [27] Sharma YK, Jiang H, Zheng C, Dai X, Wang Y, Deviny I. Impact of design and process variation on the fabrication of SiC diodes. Journal of Semiconductors. Manuscript ID 18020011.R1 (in press)

- [28] Grossner U, Alfieri G, Nipoti R. SiC device manufacturing: How processing impacts the material and device properties. In: Materials Science Forum. Vol. 821. Switzerland: Trans Tech Publications Ltd.; 2015. p. 381

- [29] Kimoto T. Material science and device physics in SiC technology for high-voltage power devices. Japanese Journal of Applied Physics. 2015;54(4):040103

- [30] Bonyadi Y, Gammon PM, Sharma YK, Baker G, Mawby PA. An investigation into the impact of surface passivation techniques using metal-semiconductor interfaces. In: Materials Science Forum. Vol. 897. Switzerland: Trans Tech Publications Ltd.; 2017. pp. 443-446

- [31] Liu G, Tuttle BR, Dhar S. Silicon carbide: A unique platform for metal-oxide-semiconductor physics. Applied Physics Reviews. 2015;**2**(2):021307

- [32] Sze SM, Ng KK. Physics of Semiconductor Devices. Hoboken, New Jersey, USA: John Wiley & Sons Inc.; 2006

- [33] Afanas'ev VV, Ciobanu F, Dimitrijev S, Pensl G, Stesmans A. Band alignment and defect states at SiC/oxide interfaces. Journal of Physics: Condensed Matter. 2004;16(17):S1839

- [34] Tuttle BR. Dangling bond defects in SiC: An ab initio study. Physical Review B. 2018;97(4):045203

- [35] Jayawardhena IU, Jayawardena A, Isaacs-Smith T, Dhar S. Effect of wafer orientation on near-interface oxide traps in 4H-SiC metal-oxide-semiconductor capacitors. In: Meeting Abstracts, No. 23; The Electrochemical Society. 2018. pp. 1441-1441

- [36] Jiao C, Ahyi AC, Dhar S, Morisette D, Myers-Ward R. Interface trap profiles in 4H-and 6H-SiC MOS capacitors with nitrogen-and phosphorus-doped gate oxides. Journal of Electronic Materials. 2017;46(4):2296-2300

- [37] Pérez-Tomás A, Brosselard P, Godignon P, Millán J, Mestres N, Jennings MR, et al. Fieldeffect mobility temperature modeling of 4H-Si C metal-oxide-semiconductor transistors. Journal of Applied Physics. 2006;100(11):114508

- [38] Ramamurthy RP, Morisette DT, Amarasinghe V, Feldman LC. Thermal-oxidation-free dielectrics for SiC power devices. In: 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA); IEEE. 2017. pp. 242-245

- [39] Thomas SM, Jennings MR, Sharma YK, Fisher CA, Mawby PA. Impact of the oxidation temperature on the interface trap density in 4H-SiC MOS capacitors. In: Materials Science Forum. Vol. 778. Switzerland: Trans Tech Publications Ltd.; 2014. pp. 599-602

- [40] Thomas SM, Sharma YK, Crouch MA, Fisher CA, Perez-Tomas A, Jennings MR, Mawby PA. Enhanced field effect mobility on 4H-SiC by oxidation at 1500 C. IEEE Journal of the Electron Devices Society. 2014;2(5):114-117

- [41] Jia Y, Lv H, Song Q, Tang X, Xiao L, Wang L, et al. Influence of oxidation temperature on the interfacial properties of n-type 4H-SiC MOS capacitors. Applied Surface Science. 2017;397:175-182

- [42] Chung GY, Tin CC, Williams JR, McDonald K, Chanana RK, Weller RA, et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Letters. 2001;22(4):176-178

- [43] Li HF, Dimitrijev S, Harrison HB, Sweatman D. Interfacial characteristics of N<sub>2</sub>O and NO nitrided SiO<sub>2</sub> grown on SiC by rapid thermal processing. Applied Physics Letters. 1997;70(15):2028-2030

- [44] Modic A, Sharma YK, Xu Y, Liu G, Ahyi AC, Williams JR, et al. Nitrogen plasma processing of SiO<sub>2</sub>/4H-SiC interfaces. Journal of Electronic Materials. 2014;43(4):857-862

- [45] Okamoto D, Sometani M, Harada S, Kosugi R, Yonezawa Y, Yano H. Effect of boron incorporation on slow interface traps in SiO<sub>2</sub>/4H-SiC structures. Applied Physics A. 2017;123(2):133

- [46] Liu G, Ahyi AC, Xu Y, Isaacs-Smith T, Sharma YK, Williams JR, et al. Enhanced inversion mobility on 4H-SiC (1120) using phosphorus and nitrogen interface passivation. IEEE Electron Device Letters. 2013;34(2):181-183

- [47] Sharma YK, Ahyi AC, Issacs-Smith T, Shen X, Pantelides ST, Zhu X, et al. Phosphorous passivation of the SiO<sub>2</sub>/4H–SiC interface. Solid-State Electronics. 2012;**68**:103-107

- [48] Sharma YK, Ahyi AC, Isaacs-Smith T, Modic A, Park M, Xu Y, et al. High-mobility stable 4H-SiC MOSFETs using a thin PSG interfacial passivation layer. IEEE Electron Device Letters. 2013;34(2):175-177

- [49] Zheng Y, Isaacs-Smith T, Ahyi AC, Dhar S. 4H-SiC MOSFETs with borosilicate glass gate dielectric and antimony counter-doping. IEEE Electron Device Letters. 2017;38(10): 1433-1436

- [50] Cabello M, Soler V, Rius G, Montserrat J, Rebollo J, Godignon P. Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Materials Science in Semiconductor Processing. 2018;78:22-31

- [51] Vivona M, Greco G, Bongiorno C, Nigro RL, Scalese S, Roccaforte F. Electrical and structural properties of surfaces and interfaces in Ti/Al/Ni Ohmic contacts to p-type implanted 4H-SiC. Applied Surface Science. 2017;420:331-335

- [52] Fedeli P, Puzzanghera M, Moscatelli F, Minamisawa RA, Alfieri G, Grossner U, Nipoti R. Ni-Al-Ti Ohmic contacts on Al implanted 4H-SiC. In: Materials Science Forum. Vol. 897. Switzerland: Trans Tech Publications Ltd.; 2017. pp. 391-394

- [53] Zhang Y, Guo T, Tang X, Yang J, He Y, Zhang Y. Thermal stability study of n-type and p-type ohmic contacts simultaneously formed on 4H-SiC. Journal of Alloys and Compounds. 2018;731:1267-1274

- [54] Gammon PM, Pérez-Tomás A, Shah VA, Vavasour O, Donchev E, Pang JS, et al. Modelling the inhomogeneous SiC Schottky interface. Journal of Applied Physics. 2013;114(22):223704

- [55] Jennings MR, Fisher CA, Walker D, Sanchez A, Pérez-Tomás A, Hamilton DP, et al. On the Ti<sub>3</sub>SiC<sub>2</sub> metallic phase formation for robust p-type 4H-SiC ohmic contacts. In: Materials Science Forum. Vol. 778. Switzerland: Trans Tech Publications Ltd.; 2014. pp. 693-696

- [56] Baliga BJ, Sung WJ, Han KJ, Harmon J, Tucker A, Syed S. PRESiCETM: Process engineered for manufacturing SiC electronic devices. In: Materials Science Forum. Vol. 924. Switzerland: Trans Tech Publications Ltd.; 2018. pp. 523-526

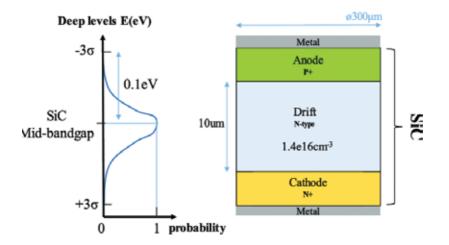

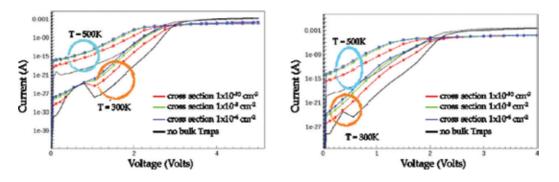

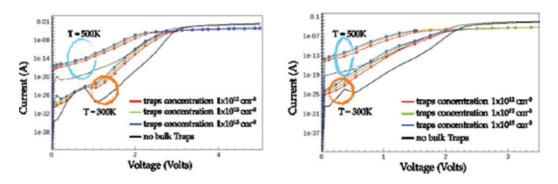

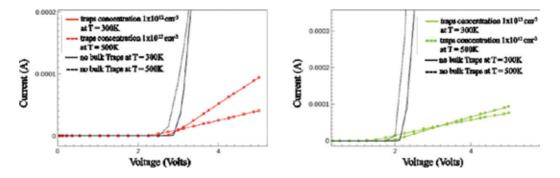

## TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors

Neophytos Lophitis, Anastasios Arvanitopoulos, Samuel Perkins and Marina Antoniou

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.76062

#### Abstract

Technology computer-aided Design (TCAD) is essential for devices technology development, including wide bandgap power semiconductors. However, most TCAD tools were originally developed for silicon and their performance and accuracy for wide bandgap semiconductors is contentious. This chapter will deal with TCAD device modelling of wide bandgap power semiconductors. In particular, modelling and simulating 3C- and 4H-Silicon Carbide (SiC), Gallium Nitride (GaN) and Diamond devices are examined. The challenges associated with modelling the material and device physics are analyzed in detail. It also includes convergence issues and accuracy of predicted performance. Modelling and simulating defects, traps and the effect of these traps on the characteristics are also discussed.

**Keywords:** TCAD, modelling and simulation, silicon carbide, gallium nitride, diamond, physics modelling, material parameters

#### 1. Introduction

#### 1.1. Materials and devices

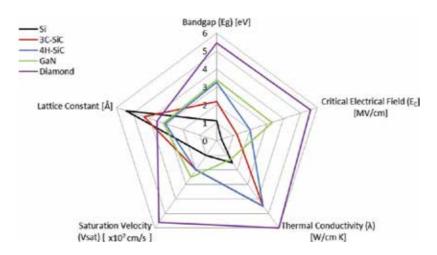

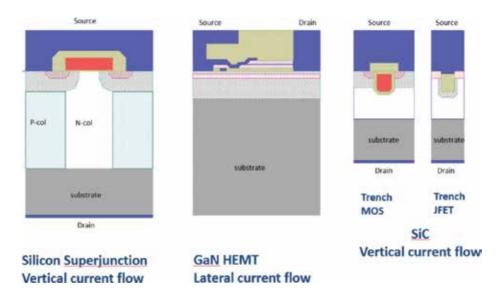

Power devices made from wide bandgap materials have superior performance compared to those made from silicon. They can sustain higher voltages or endure smaller losses, they can operate at much higher junction temperatures and can switch faster. This is because, as seen in **Figure 1**, of their superior electrical properties. This in turn can revolutionize how applications work and possibly make new applications possible. The most mature materials in terms of process and device technology are the 4H-SiC and GaN-based devices. There is however, an

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Figure 1. Material properties of significant power semiconductors normalized against Si, data taken form [1, 2].

increased interest and effort in advancing 3C-SiC and overcoming the technical challenges associated with the development of good-quality 3C-SiC wafers because of lower processing costs and the possibility for high channel mobility MOSFETs. Ultra-wide bandgap materials such as diamond are also being explored.

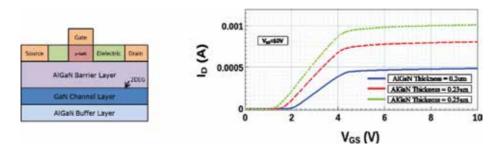

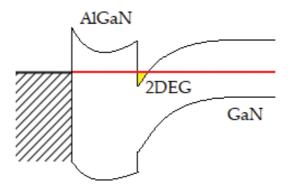

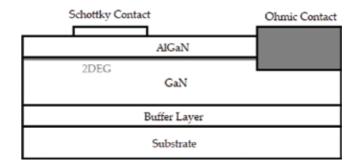

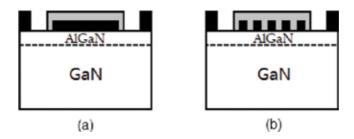

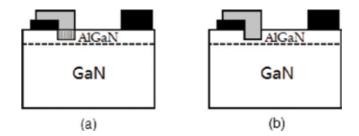

Silicon carbide is similar to silicon in terms of device design and optimization strategies. Most devices made in silicon can also be made in SiC. This includes Schottky Barrier Diodes, MOSFETs, IGBTs, and Thyristors. However, devices made in GaN are hetero devices and base their operation on the two-dimensional electron gas (2DEG) that is formed in the quantum well between the heterojunction interfaces. This quantum well provides electrons with a highly conductive channel, allowing high electron mobility. It is reported in literature that the electron mobility in GaN HEMT devices can be upwards of 1500 cm<sup>2</sup>/Vs [3].

#### 1.2. Technology computer-aided design

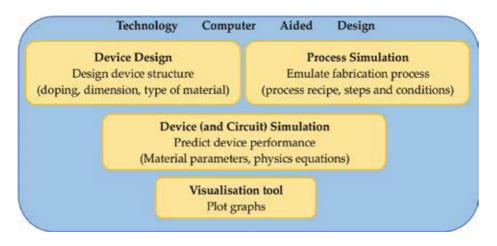

TCAD is an engineering computer-aided tool which enables the physics-based modelling of semiconductor devices and their fabrication process. Due to the excellent predicting capability, semiconductor process and device engineers use TCAD for virtual prototyping and optimization of devices, to reduce the number of experimental cycles and, therefore, to reduce the production cost. TCAD can also be used to study the performance of devices when used in new applications or environments, to find performance limits and to analyze failures [4, 5]. Modern TCAD suites are compiled by several tools. A typical example of a TCAD suite is diagrammatically described in **Figure 2** and it consists of the following elements:

#### • Device design tool

The device design tool allows the rapid creation of device structures via the use of scripting language or a graphical user interface without the need to know the process recipe. At this

TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors 19 http://dx.doi.org/10.5772/intechopen.76062

Figure 2. Exemplary combination of tools making up a typical TCAD suite framework.

stage, the device geometry, the material and doping profile, and concentration of regions is defined. Commercial tools include Synopsys Sentaurus Structure Editor [6] and SilvacoDev-Edit<sup>™</sup> [7]. These tools allow device designers to parameterize device aspects and features to optimize their design or to assess the performance dependence on the parameters of question.

#### • Process simulation tool

The process simulation tools allow for the virtual fabrication of devices and the emulation of fabrication steps and conditions. They typically make use of a scripting language and require knowledge of a process recipe. These tools allow process engineers to fine tune their recipe and to analyze the effect of each process step and condition on the resulting device structure. Commercial tools include Synopsys Sentaurus Sentaurus Process [8] and Silvaco Athena [9].

#### • Device (and circuit) simulation tool

Device simulation tools have the capability to simulate the electrical, thermal, and optical properties and performance of devices. They can also account for the circuitry that surrounds a device when used in real applications. Therefore, they typically have SPICE capabilities too. They predict the device performance by executing finite element analysis and the solution of fundamental semiconductor physics equations. They make use of numerical devices created either through a device design tool or a process simulation tool. They take into consideration the materials incorporated in the device and they have a database with physics equations and the equivalent material parameters. Commercial tools include Synopsys Sentaurus Device [10] and Silvaco Atlas [11].

#### 1.3. Summary

This chapter aims to highlight issues and present solutions and methods for achieving accurate models of WBG power devices. This includes proper modelling the material physics equations

and their parameters, creating the finite elements and geometry and simulation of device characteristics including numerical issues and the effect of traps.

#### 2. Material physics modelling

TCAD tools solve fundamental semiconductor physics equations to predict the performance of semiconductor devices. Accurately modelling the material properties through appropriate physics equations and parameters is essential for reliable simulations. These can depend on how advanced and mature the process, growth and technology is. For silicon, the material properties have been studied extensively and the technology is mature. Therefore, the material models and their parameters are typically considered accurate and able to predict the silicon-based devices performance with high level of accuracy. However, for WBG semiconductor-based devices, a lower confidence level exists. In the following subsections, we discuss the physics equations and the parameter sets required for accurate physical modelling of 3C-SiC, 4H-SiC, GaN and diamond power semiconductors. The equations used and parameters are compatible with most TCAD products.

#### 2.1. Silicon carbide

There are hundreds of Silicon Carbide polytypes. From those, 4H-SiC is the most mature and studied polytype. The cubic polytype, 3C-SiC is also of particular interest because of its special properties, such as the ability to grow this compound semiconductor on large area silicon wafers, the lower temperatures required when processing the material and the ability to make MOSFETs with much higher channel mobility. The former two results in a much cheaper starting wafer whereas the latter one can enable the development of devices with higher efficiency. The corresponding values required in a physics parameter file for 4H-SiC were developed and improved alongside the improvement of the technology. Recently there have been efforts to compile an equivalent set of parameters for 3C and to validate them [12, 13]. This section presents the required models and the parameters of both materials. Wherever necessary, a range of values is used. Further, each physical mechanism presented is accompanied with the corresponding identified limitations. SiC polytypes can experience anisotropic properties, therefore when aiming multidimensional device simulation, these must be accounted for in the material parameter file and physics equations [14]. 4H-SiC experiences such behaviour, whilst 3C-SiC experiences isotropic behaviour. The parameters are then included within the 'Device (and Circuit) Simulation' tool of TCAD tools.

#### 2.1.1. Band parameters

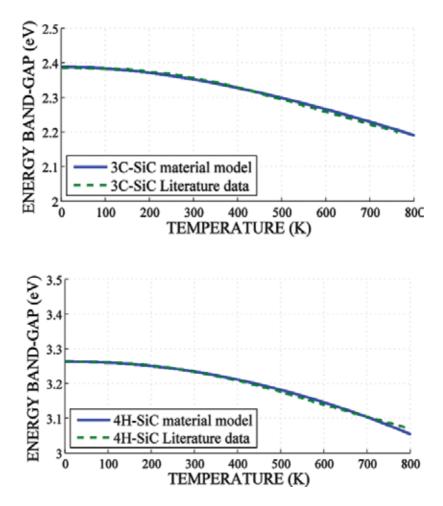

The desired properties of the WBG SiC originate from its bandgap characteristics. The value of  $E_g$  shall not be considered constant, but variable with dependencies on both the concentration of impurities and temperature as shown in **Figures 3** and **4** correspondingly. Increasing the temperature of the material essentially leads to lower gap values as described by Eq. (1). In

TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors 21 http://dx.doi.org/10.5772/intechopen.76062

Figure 3. The 3C-SiC (top) and 4H-SiC (bottom) bandgap dependence on temperature as described with the models given in this chapter are in excellent agreement to literature data [15] for both  $\beta$ -SiC and  $\alpha$ -SiC, respectively.

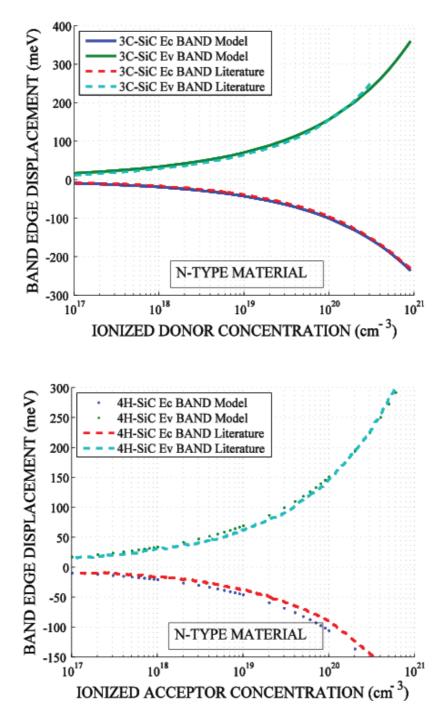

addition, the phenomenon of bandgap narrowing causes band displacements in the energy scale directly related to doping according to Eq. (2), (3). These displacements represent potential barriers that may influence carrier transportation phenomena in the device. The bandgap dependence on doping in SiC can be described as in Eq. (4). The perception of the modeled effective bandgap value for the SiC can be expressed as  $E_{g,eff}(T) = E_g(T) - E_{bgn}$  utilizing the parameters shown in **Tables 1–3**.

$$E_g(T) = E_g(0) - \alpha T^2 / (T + \beta)$$

<sup>(1)</sup>

$$E_{bgn}^{cond} = \begin{cases} A_n \cdot N_{tot}^{1/3} + C_n \cdot N_{tot}^{1/2}, & N_{D,0} > N_{A,0} \\ B_p \cdot N_{tot}^{1/4} + D_p \cdot N_{tot}^{1/2}, & otherwise \end{cases}$$

(2)

Figure 4. The bandgap narrowing phenomenon as modeled for TCAD simulations assuming n-type SiC material. The measured energy displacements of the bands are sourced from [16].

| Parameters description | 3C-SiC               | 4H-SiC            |

|------------------------|----------------------|-------------------|

| $E_g(0)$ [eV]          | 2.39                 | 3.265             |

| α [eV/K]               | $0.66 	imes 10^{-3}$ | $3.3	imes10^{-2}$ |

| β [K]                  | 1335                 | $1.0 	imes 10^5$  |

Table 1. SiC parameter set related to bandgap.

| Lindefelt model coefficients                  | 3C-SiC semiconductor material |                        |

|-----------------------------------------------|-------------------------------|------------------------|

|                                               | n-type                        | p-type                 |

| $A_{n,p}$ [eV·cm]                             | $-1.48	imes10^{-8}$           | $1.3	imes 10^{-8}$     |

| $B_{n,p} [\text{eV} \cdot \text{cm}^{3/4}]$   | $9.0	imes 10^{-7}$            | $-4.8	imes10^{-7}$     |

| $C_{n,p} [eV \cdot cm^{3/2}]$                 | $-3.06 	imes 10^{-12}$        | $1.43\times 10^{-12}$  |

| $D_{n,p} \ [\text{eV} \cdot \text{cm}^{3/2}]$ | $6.85 	imes 10^{-12}$         | $-6.41 	imes 10^{-13}$ |

Table 2. 3C-SiC band gap narrowing doping dependence.

| Lindefelt model coefficients                     | 4H-SiC semiconductor material |                        |

|--------------------------------------------------|-------------------------------|------------------------|

|                                                  | n-type                        | p-type                 |

| $A_{n,p}$ [eV·cm]                                | $-1.791 \times 10^{-8}$       | $3.507\times 10^{-8}$  |

| $B_{n,p} [\text{eV} \cdot \text{cm}^{3/4}]$      | $8.927\times 10^{-7}$         | $-2.312\times10^{-6}$  |

| $C_{n,p} [eV \cdot cm^{3/2}]$                    | $-2.2 	imes 10^{-12}$         | $6.74\times10^{-12}$   |

| $D_{n,p}  [\mathrm{eV} \cdot \mathrm{cm}^{3/2}]$ | $6.24\times10^{-12}$          | $-1.07 	imes 10^{-12}$ |

Table 3. 4H-SiC bandgap narrowing doping dependence.

| Parameters description                     | 3C-SiC                  | 4H-SiC                |

|--------------------------------------------|-------------------------|-----------------------|

| N <sub>C</sub> (300 K) [cm <sup>-3</sup> ] | $1.5536 	imes 10^{19}$  | $1.719\times 10^{19}$ |

| N <sub>V</sub> (300 K) [cm <sup>-3</sup> ] | $1.1639 \times 10^{19}$ | $2.509\times10^{19}$  |

Table 4. SiC temperature dependent density of states.

$$E_{bgn}^{val} = \begin{cases} B_n \cdot N_{tot}^{1/4} + D_n \cdot N_{tot}^{1/2}, & N_{D,0} > N_{A,0} \\ A_p \cdot N_{tot}^{1/3} + C_p \cdot N_{tot}^{1/2}, & otherwise \end{cases}$$

(3)

$$\Delta E_g^0 = -E_{bgn}^{cond} + E_{bgn}^{val} \tag{4}$$

To model the intrinsic characteristics of the semiconductor, the temperature dependence of the density of states (DoS) for SiC in Eq. (5) is used. The parameters of **Table 4** determine the

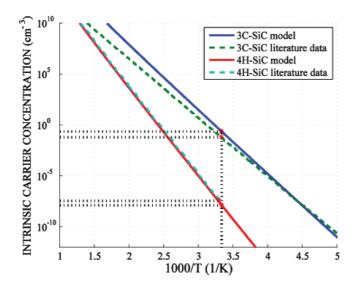

**Figure 5.** The intrinsic carrier concentration as resulting from the model of DoS for both SiC cases in question. Comparison with literature data for 3C-SiC [18] and 4H-SiC [16] is performed. Assuming low doping levels ( $5 \times 10^{15}$  cm<sup>-3</sup>) the bandgap narrowing is considered negligible.

intrinsic carrier concentration of the semiconductor as well as quantities like the effective carrier masses. In **Figure 5**, plotting the intrinsic carrier concentration against the temperature a discrepancy with measurements can be noticed for the case of 3C-SiC. This suggests that the TCAD simulations of 3C-SiC power devices utilizing this model should yield reasonably good results for limited temperature range of 200–500 K.

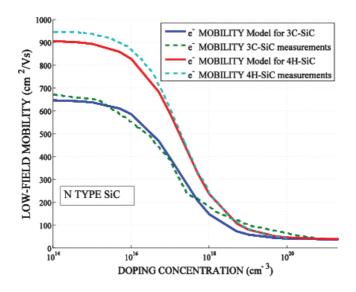

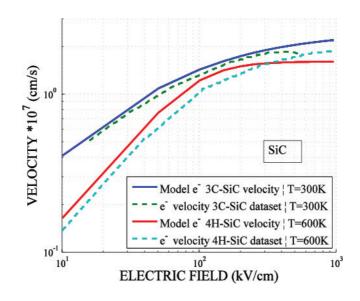

Under low field conditions, the mobility of both types of carriers in SiC also depends on the doping concentration and on temperature. The first dependence is described by the Caughey-Thomas (C-T) model  $\mu_0 = \mu_{min} + (\mu_{max} - \mu_{min})/(1 + (N/N_{ref})^{\alpha})$  as illustrated in **Figure 6**. Each coefficient in the C-T equation changes with temperature as in Eq. (6) and the values in **Table 6**. Currently, there is an uncertainty for the holes' mobility actual value in 3C-SiC. However, the values adopted in **Table 5** are suggested from recent measurements [16, 17]. The mobility of carriers for the temperature range of 250–700 K was described in [12]. In high field conditions, with magnitude of values as shown in **Figure 7**, the mobility and velocity of carriers become inseparable directly affecting each other. The Canali model, Eq. (7) is utilized for these purposes and its parameters for SiC are presented in **Table 7**. In Eq. (8), the holes' saturation velocity determines the range of electric field values at 200 kV/cm < E < 2000 kV/cm [12].

$$N_{C,V}(T) = N_{C,V} 300 \times (T/300)^{3/2}$$

(5)

$$Par = Par_0 \times (T/300K)^{\gamma} \tag{6}$$

$$\mu_0(E) = \frac{(\alpha+1)\mu_{low}}{\alpha + \left[1 + \left(\frac{(\alpha+1)\mu_{low}E}{v_{sat}}\right)^{\beta}\right]^{1/\beta}}$$

(7)

TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors 25 http://dx.doi.org/10.5772/intechopen.76062

Figure 6. Based on experimental data [19], the SiC models utilized result in a very good accuracy. Increased the doping concentration, more scattering occurs and the mobility drops. The maximum carrier mobility values in SiC range and depend on crystal thickness [20] and impurities level.

| Parameter                         | 3C-SiC             |                   | 4H-SiC [perpe      | 4H-SiC [perpendicular to c-axis] |                    | 4H-SiC [parallel to c-axis] |  |

|-----------------------------------|--------------------|-------------------|--------------------|----------------------------------|--------------------|-----------------------------|--|

|                                   | Electrons          | Holes             | Electrons          | Holes                            | Electrons          | Holes                       |  |

| $\mu_{max}$ [cm <sup>2</sup> /Vs] | 650                | 70                | 910                | 114                              | 1100               | 114                         |  |

| $\mu_{min}$ [cm <sup>2</sup> /Vs] | 40                 | 15                | 40                 | 0                                | 40                 | 0                           |  |

| $N_{ref}$ [cm <sup>-3</sup> ]     | $1.5\times10^{17}$ | $5\times 10^{19}$ | $2.0\times10^{17}$ | $2.4\times10^{18}$               | $2.0\times10^{17}$ | $2.4\times10^{18}$          |  |

| α                                 | 0.8                | 0.3               | 0.76               | 0.69                             | 0.76               | 0.69                        |  |

Table 5. SiC parameters for low field mobility and coefficients used to express doping dependence.

| Parameter         | 3C-SiC    |       | 4H-SiC<br>[same for bot | h directions] | Corresponding parameter from Table 5     |

|-------------------|-----------|-------|-------------------------|---------------|------------------------------------------|

|                   | Electrons | Holes | Electrons               | Holes         |                                          |

| γ <sub>max</sub>  | -0.3      | -2.5  | -2.4                    | -2.6          | $\mu_{max}$ [cm <sup>2</sup> /Vs]        |

| $\gamma_{min}$    | -0.5      | -0.5  | -1.536                  | -0.57         | $\mu_{min}  [\mathrm{cm}^2/\mathrm{Vs}]$ |

| γ <sub>Nref</sub> | 2         | 0     | 0.75                    | 2.9           | $N_{ref}$ [cm <sup>-3</sup> ]            |

| γα                | 0         | 0     | 0.722                   | -0.2          | α                                        |

Table 6. SiC parameters for low field mobility and coefficients used to express temperature dependence.

**Figure 7.** The models for SiC electrons' velocity allow accurate TCAD simulations for temperatures up to 600 K. Comparison with literature data for 3C-SiC [21] and 4H-SiC [19] is performed. A doping level of  $5 \times 10^{15}$  cm<sup>-3</sup> is assumed.

| Parameter                   | 3C-SiC         |                   | 4H-SiC                              |                          |                 |

|-----------------------------|----------------|-------------------|-------------------------------------|--------------------------|-----------------|

|                             | Electrons      | Holes             | Electrons [ <sub>*</sub> to c-axis] | Electrons [// to c-axis] | Holes           |

| beta (β <sub>0</sub> )      | 0.75           | 2.5               | 1.2                                 | 1.2                      | 1.2             |

| Ybeta                       | -0.9           | 0                 | 1.0                                 | 1.0                      | 1.0             |

| alpha (α)                   | 0              | 0                 | 0                                   | 0                        | 0               |

| v <sub>sat,0</sub> [cm/sec] | $2.5	imes10^7$ | $1.63 	imes 10^7$ | $2.2 \times 10^7$                   | $1.9 	imes 10^7$         | $2.2\times10^7$ |

| v <sub>sat,exp</sub>        | -0.65          | 1.55              | 0.44                                | 0.44                     | 0.44            |

Table 7. SiC parameters for high field mobility and saturation velocity along with coefficients used to express temperature dependence.

$$v_{sat} = v_{sat,0} \left(\frac{300K}{T}\right)^{v_{sat,\exp}}$$

(8)

#### 2.1.2. Doping and incomplete ionization

Compared to silicon, dopants in wide bandgap semiconductors have larger ionization energies, making activation of the doping species an issue. The dopant impurities are better modeled as traps to account for the phenomenon of incomplete ionization. As shown in **Table 8**, the formed energy levels depend on the polytype and the impurity. To model this behaviour, Eqs. (9) and (10) are utilized, where  $N_{A,D}$  is the doping concentration,  $N_{A,D'}$  is the effective doping concentration,  $E_{A,D}$  and  $E_f$  are the activation energy, and the Fermi level, respectively,  $G_A$  is the degeneracy factor, and  $N_{crit}$  is the value that determines where the

| Impurity       | Species type          | Energy levels [eV] |        |

|----------------|-----------------------|--------------------|--------|

|                |                       | 3C-SiC             | 4H-SiC |

| Nitrogen (N)   | Donor <sup>a</sup>    | 0.057              | 0.071  |

| Vanadium (V)   | Donor <sup>a</sup>    | 0.660              | 0.800  |

| Aluminium (Al) | Acceptor <sup>b</sup> | 0.260              | 0.265  |

| Gallium (Ga)   | Acceptor <sup>b</sup> | 0.343              | 0.300  |

| Boron (B)      | Acceptor <sup>b</sup> | 0.735              | 0.293  |

<sup>b</sup>The formed energy level is considered from the valence band  $(E_V)$ .

Table 8. SiC impurities/shallow traps due to doping.

metallic-type conduction mechanism starts [22]. The degeneracy factor temperature dependence can be expressed by Eq. (11), whilst the typical values for  $g_A$  is 4 and for  $g_D$  is 2 for the impurity levels of acceptors and donors in SiC, respectively [23]:

$$N_{A,D'} = N_{A,D} / (1 + G_A * (E_{A,D} - E_f) / kT) \qquad N_{A,D} < N_{crit}$$

(9)

$$N_{A,D'} = N_{A,D} \qquad \qquad N_{A,D} \ge N_{crit} \tag{10}$$

$$G_{A,D}(T) = g_{A,D} \cdot \exp\left(\frac{\Delta E_{A,D}}{kT}\right)$$

(11)

#### 2.1.3. Impact ionization

The impact ionization coefficients of electrons and holes need to be determined to specify the breakdown voltage [24]. For 3C-SiC, the Chynoweth law  $\alpha(E_{ava}) = \gamma \cdot \alpha \cdot \exp(-\gamma b/E_{ava})$  can be adopted. The parameter values are determined in **Table 9**, following the work of van Overstraeten-de Man [25]. The temperature dependence of these parameters is expressed by determining the optical phonon energy as indicated by  $\gamma = \tanh(\hbar\omega_{op}/2kT_0)/\tanh(\hbar\omega_{op}/2kT)$ .

| Parameters description                          | Parameter<br>name                | 3C-SiC                                             |                                                    | 4H-SiC [* to c-axis] |                                                    | 4H-SiC [// to c-axis] |                        |

|-------------------------------------------------|----------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------|----------------------------------------------------|-----------------------|------------------------|

|                                                 |                                  | Electrons                                          | Holes                                              | Electrons            | Holes                                              | Electrons             | Holes                  |

| Ionization coefficients for electrons and holes | $a_{n,p} \left[ cm^{-1} \right]$ | $1.28 \times 10^{6}$                               | $1.07 \times 10^7$                                 | $1.76 \times 10^8$   | $\begin{array}{c} 3.41 \times \\ 10^8 \end{array}$ | $2.1 \times 10^7$     | 2.96 × 10 <sup>7</sup> |

|                                                 | b <sub>n,p</sub> [V/cm]          | $\begin{array}{c} 5.54 \times \\ 10^6 \end{array}$ | $\begin{array}{c} 1.12 \times \\ 10^7 \end{array}$ | $3.3 	imes 10^7$     | $2.5 \times 10^7$                                  | $1.7 	imes 10^7$      | $1.6 \times 10^7$      |

| Low field range up to this value                | E <sub>0</sub> [V/cm]            | $4.0 	imes 10^5$                                   | $\begin{array}{c} 4.0 \times \\ 10^5 \end{array}$  | _                    | _                                                  | _                     | -                      |

| Optical phonon energy                           | $\hbar\omega_{op}$ [eV]          | 0.120                                              | 0.120                                              | 0.190                | 0.190                                              | 0.190                 | 0.190                  |

**Table 9.** SiC impact ionization coefficients for  $T_0 = 300 K$

Notably, it has been found in [26] that these values are relatively insensitive to temperature variations in the range of 300 K < T < 500 K. For 4H-SiC, a slightly different model is utilized after Hatakeyama's work [27] to effectively describe the anisotropic behaviour of the avalanche coefficients. The avalanche force is considered to have two components to account for the anisotropic structure of 4H-SiC [28], satisfying  $F^2 = F_{//}^2 + F_{\odot}^2$ . Utilizing the projections of these electric field components, the avalanche coefficients can be computed as indicated in Eqs. (12)–(15), with the default value of  $\theta = 1$ :

$$a = a_{\odot}^{\left(\frac{B F_{\odot}}{B_{\odot}F}\right)^2} \cdot a_{//}^{\left(\frac{B F_{//}}{B_{//}F}\right)^2}$$

(12)

$$b = B \sqrt{1 - \theta A^2 \left(\frac{BF_{\theta}F_{//}}{Fb_{\theta}b_{//}}\right)^2}$$

(13)

$$A = \log \frac{a_{//}}{a_{\odot}} \tag{14}$$

$$B = \frac{F}{\sqrt{\left(\frac{F_o}{b_o}\right)^2 + \left(\frac{F_{//}}{b_{//}}\right)^2}}$$

(15)

#### 2.1.4. Generation-recombination

The doping dependence of the SRH lifetime is modeled with Scharfetter in Eq. (16). The bandto-band non-radiative recombination is expressed with the Auger recombination rates,  $R_{net}^A = (C_n n + C_p p) (np - n_{i,eff}^2)$ . As shown in Eqs. (17) and (18), the effect of temperature and doping is accounted for. Typical values for the Scharfetter and Auger models are shown in **Tables 10** and **11**. However, since these are heavily process dependent, they need to be adjusted every time the process conditions change:

| Parameter                                       | SiC                |                     |  |  |

|-------------------------------------------------|--------------------|---------------------|--|--|

|                                                 | Electrons          | Holes               |  |  |

| $\tau_{min}$ [sec]                              | 0                  | 0                   |  |  |

| $\tau_{max}$ [sec]                              | $2.5	imes 10^{-6}$ | $0.5 	imes 10^{-6}$ |  |  |

| $	au_{max}$ [sec] $N_{ref}$ [cm <sup>-3</sup> ] | $1 \times 10^{17}$ | $1 	imes 10^{17}$   |  |  |

| γ                                               | 0.3                | 0.3                 |  |  |

| $T_{\alpha}$                                    | 1.72               | 1.72                |  |  |

| T <sub>coef</sub>                               | 2.55               | 2.55                |  |  |

| E <sub>trap</sub> [eV]                          | 0                  | 0                   |  |  |

Table 10. SiC SRH lifetime parameter set.

| Parameter                 | 3C-SiC             |                      | 4H-SiC               | 4H-SiC                 |  |  |

|---------------------------|--------------------|----------------------|----------------------|------------------------|--|--|

|                           | Electrons          | Holes                | Electrons            | Holes                  |  |  |

| A [cm <sup>6</sup> /sec]  | $0.3	imes10^{-31}$ | $0.2 	imes 10^{-31}$ | $6.7	imes10^{-32}$   | $7.2 	imes 10^{-32}$   |  |  |

| B [cm <sup>6</sup> /sec]  | 0                  | 0                    | $2.45\times10^{-31}$ | $4.5\times10^{-33}$    |  |  |

| C [cm <sup>6</sup> /sec]  | 0                  | 0                    | $-2.2\times10^{-32}$ | $2.63 \times 10^{-32}$ |  |  |

| Н                         | 1.9                | 1.9                  | 3.47                 | 8.26                   |  |  |

| $N_0  [{ m cm}^{-3}]$     | $1.0	imes10^{19}$  |                      | $1.0	imes10^{18}$    |                        |  |  |

| <i>T</i> <sub>0</sub> [K] | 300                | 300                  | 300                  | 300                    |  |  |

Table 11. SiC Auger recombination rates.

$$\tau_{dop} = \tau_{min} + \frac{\tau_{max} - \tau_{min}}{1 + \left(\frac{N_{A,0} + N_{D,0}}{N_{ref}}\right)^{\gamma}}$$

(16)

$$C_n(T,n) = \left(A_n + B_n\left(\frac{T}{T_0}\right) + C_n\left(\frac{T}{T_0}\right)^2\right) \left[1 + H_n \exp\left(-\frac{n}{N0,n}\right)\right]$$

(17)

$$C_p(T,p) = \left(A_p + B_p\left(\frac{T}{T_0}\right) + C_p\left(\frac{T}{T_0}\right)^2\right) \left[1 + H_p \exp\left(-\frac{p}{N0,p}\right)\right]$$

(18)

#### 2.2. Gallium nitride

GaN-based devices utilize GaN, AlGaN and AlN materials. AlGaN is a molar fraction of AlN and GaN. GaN and AlGaN naturally form Wurtzite crystal structures with the ability of forming different Ga and N faces. For this chapter, only the Ga-face is considered. In TCAD, it is necessary to define the material properties of AlN and GaN separately. AlGaN material properties are thereafter approximated through a linear interpolation, depending on the molar fraction of AlN and GaN. A more accurate result can be yielded wherever the molar compounds are known and experimental evaluation of their properties has been performed. In those cases, new material parameters can be made which would reflect the exact molar compound of interest, which in turn would give more accurate simulations.

Similar to modelling SiC, the important parameters include modelling the bandgap, doping and incomplete ionization, impact ionization, mobility and generation-recombination.

#### 2.2.1. Band parameters

Like all III-Nitride semiconductors, GaN and AlN are direct bandgap semiconductors, that is, the maximum valley in their valance band is directly below the minimum conduction valley. Similar to SiC examined earlier,  $E_g$  cannot be assumed constant in value and will vary heavily with temperature and doping concentration. Again, like SiC, thermally exciting GaN leads to lower band gap energies. According to Eq. (1) the variation of bandgap value can be described utilizing the parameters in **Table 12** [29].

| Parameters description | GaN                  | AlN                   |

|------------------------|----------------------|-----------------------|

| $E_g(0)$ [eV]          | 3.507                | 6.23                  |

| $\alpha  [eV/K]$       | $9.1 \times 10^{-4}$ | $1.79 \times 10^{-3}$ |

| β [K]                  | 836                  | $1.462 \times 10^{3}$ |

Table 12. GaN/AlN parameter set related to bandgap.

Further, utilizing Eq. (19), the intrinsic carrier concentration of the GaN material can be calculated. This premises that the DoS and/or the effective carrier masses in this WBG material are known. Equations (20) and (21) adequately describe this temperature dependent procedure. The intrinsic characteristics of GaN can then be given by [30]:

$$n_i = \left(N_c \cdot N_v\right)^{1/2} exp\left(-E_g/(2k_BT)\right) \tag{19}$$

$$N_{c} = 4.82 \ 10^{15} \cdot (m_{\Gamma}/m_{0})^{3/2} T^{3/2} \ (cm^{-3})^{\sim} = 4.3 \times 10^{14} \times T^{3/2} \ (cm^{-3}) \tag{20}$$

$$N_{\rm v} = 8.9 \times 10^{15} \times T^{3/2} \, (\rm cm^{-3}) \tag{21}$$

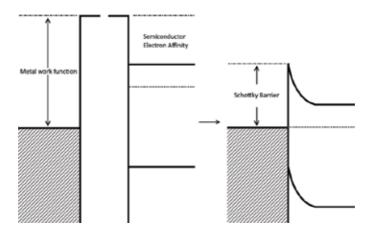

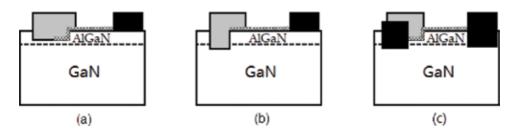

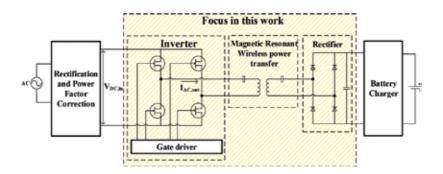

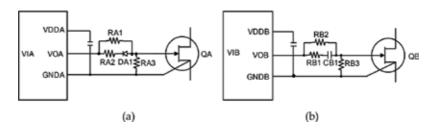

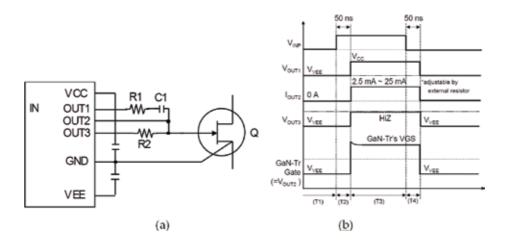

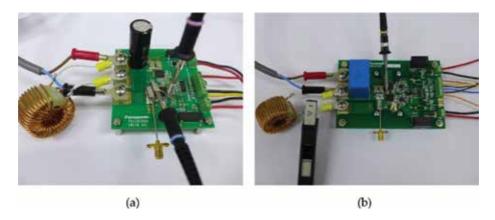

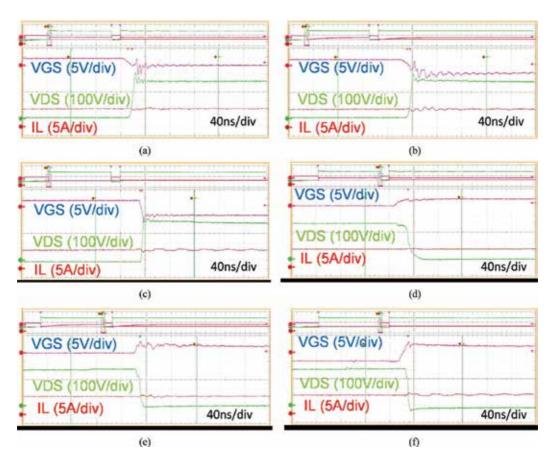

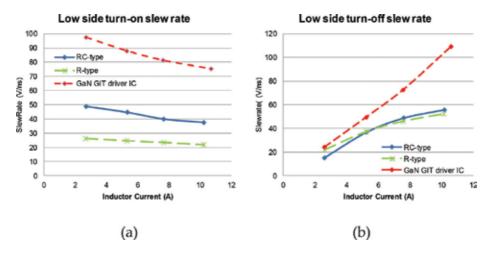

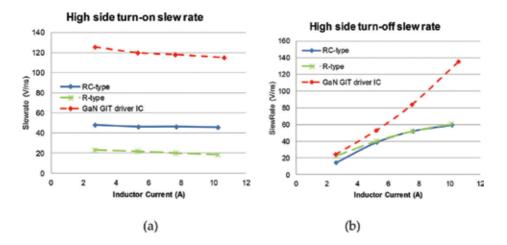

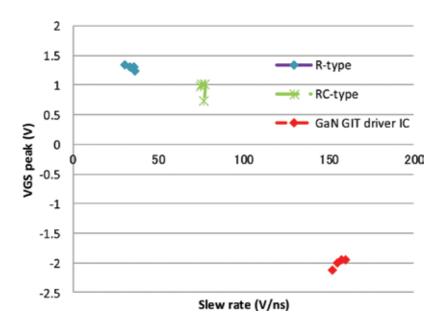

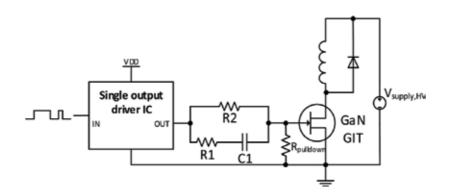

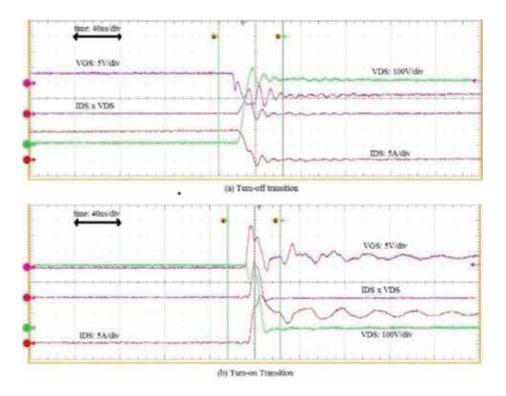

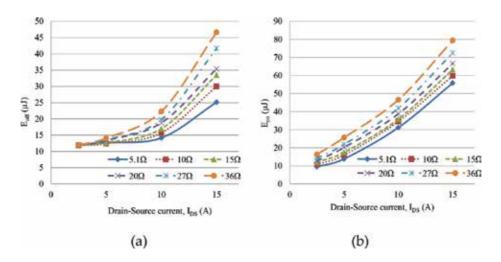

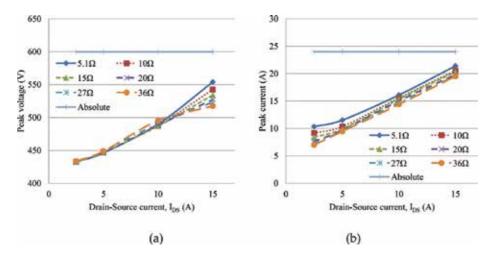

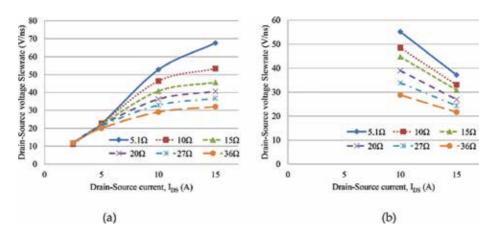

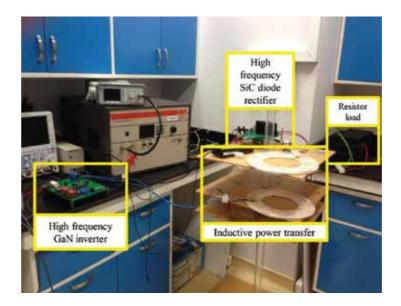

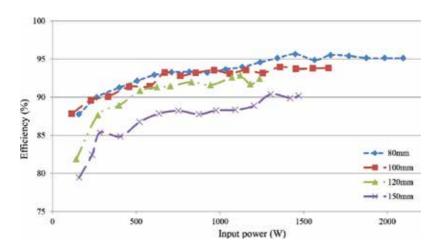

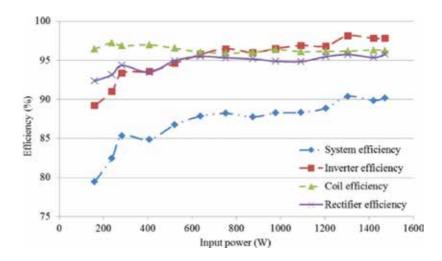

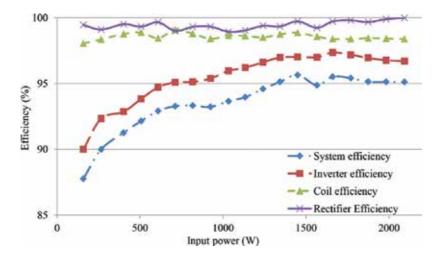

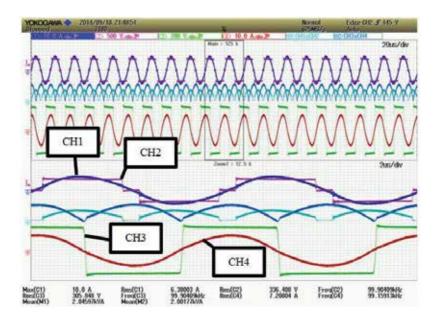

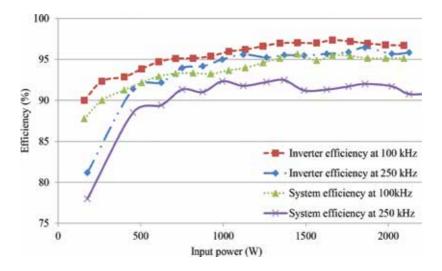

### 2.2.2. Mobility