# IntechOpen

# Network-on-Chip

Architecture, Optimization, and Design Explorations

Edited by Isiaka A. Alimi, Oluyomi Aboderin, Nelson J. Muga and António L. Teixeira

# Network-on-Chip - Architecture, Optimization, and Design Explorations

Edited by Isiaka A. Alimi, Oluyomi Aboderin, Nelson J. Muga and António L. Teixeira

Published in London, United Kingdom

IntechOpen

Supporting open minds since 2005

Network-on-Chip - Architecture, Optimization, and Design Explorations  $http://dx.doi.org/10.5772/intechopen.91110 \\ Edited by Isiaka A. Alimi, Oluyomi Aboderin, Nelson J. Muga and António L. Teixeira$

#### Contributors

Masaru Fukushi, Yota Kurokawa, Erulappan Sakthivel, Rengaraj Madavan, Adebayo E. Abejide, Madhava R. Kota, Sushma Pandey, Oluyomi Aboderin, Mário Lima, António L. Teixeira, Cátia Pinho, Isiaka Ajewale Alimi, Romil K. Patel, Abdelgader M. Abdalla, Nelson J. Muga, Armando N. Pinto, Ramoni A. Gbadamosi, Zhongjing Ren, Jianping Yuan, Peng Yan

#### © The Editor(s) and the Author(s) 2022

The rights of the editor(s) and the author(s) have been asserted in accordance with the Copyright, Designs and Patents Act 1988. All rights to the book as a whole are reserved by INTECHOPEN LIMITED. The book as a whole (compilation) cannot be reproduced, distributed or used for commercial or non-commercial purposes without INTECHOPEN LIMITED's written permission. Enquiries concerning the use of the book should be directed to INTECHOPEN LIMITED rights and permissions department (permissions@intechopen.com).

Violations are liable to prosecution under the governing Copyright Law.

Individual chapters of this publication are distributed under the terms of the Creative Commons Attribution 3.0 Unported License which permits commercial use, distribution and reproduction of the individual chapters, provided the original author(s) and source publication are appropriately acknowledged. If so indicated, certain images may not be included under the Creative Commons license. In such cases users will need to obtain permission from the license holder to reproduce the material. More details and guidelines concerning content reuse and adaptation can be found at http://www.intechopen.com/copyright-policy.html.

#### Notice

Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published chapters. The publisher assumes no responsibility for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained in the book.

First published in London, United Kingdom, 2022 by IntechOpen IntechOpen is the global imprint of INTECHOPEN LIMITED, registered in England and Wales, registration number: 11086078, 5 Princes Gate Court, London, SW7 2QJ, United Kingdom Printed in Croatia

British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library

Additional hard and PDF copies can be obtained from orders@intechopen.com

Network-on-Chip - Architecture, Optimization, and Design Explorations Edited by Isiaka A. Alimi, Oluyomi Aboderin, Nelson J. Muga and António L. Teixeira p. cm.

Print ISBN 978-1-83968-148-6

Online ISBN 978-1-83968-158-5

eBook (PDF) ISBN 978-1-83968-159-2

# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

5,700+

141,000+

180M+

Open access books available

International authors and editors

Downloads

156

Countries delivered to

Our authors are among the

Top 1%

most cited scientists

12.2%

Contributors from top 500 universities

Selection of our books indexed in the Book Citation Index (BKCI) in Web of Science Core Collection™

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

### Meet the editors

Isiaka A. Alimi received his Ph.D. in Telecommunications Engineering from the University of Aveiro, Portugal. He was with the Federal Radio Corporation of Nigeria as a senior engineer (RF transmission and management) and the Department of Electrical and Electronics Engineering, Federal University of Technology, Akure, Nigeria, as a lecturer. He is currently a researcher at the Instituto de Telecomunicações, Aveiro, Portugal, where he

has been participating in various R&D activities. He has authored/co-authored more than forty technical papers, nine book chapters, and has co-edited one book. His research interests include optical communications, microwave photonics, network security, fixed-mobile broadband (wired and wireless technologies) convergence, and their applications for effective resources management in access networks. He is a member of the Institute of Electrical and Electronics Engineers (IEEE).

Oluyomi Aboderin obtained a Ph.D. in Telecommunications Engineering from the University of Porto, Portugal. He also obtained a master's degree in Personal Mobile and Satellite Communications from the University of Bradford, United Kingdom, and a bachelor's degree from the Ladoke Akintola University of Technology, Nigeria. He joined the National Space Research and Development Agency in 2005 and is currently an assistant direc-

tor with the agency, in the frequency coordination and management team. He was a researcher with Instituto de Telecommunicações, Aveiro, Portugal, and has been participating in various research and development activities. He has published more than ten technical papers, including a patent. His research interests include satellite channel modeling, frequency management, antenna design, underwater communications, and microwave photonics.

Nelson Muga graduated in Physics from the University of Porto, Portugal, in 2002. He received a master's degree in Applied Physics in 2006, and a Ph.D. in Physical Engineering in 2011, both from the University of Aveiro, Portugal. He has been a lecturer in the Physics Department, the University of Aveiro since 2016, where he teaches courses related to optics, optoelectronics, and photonics. Currently, he is an auxiliary researcher at the Insti-

tuto de Telecomunicações, Aveiro, where, over the years, he has participated as a researcher in more than twenty-five R&D projects, developing expertise in the field of high-speed optical communications and quantum-secure optical communication systems and technologies. He has published more than forty papers in international journals and more than sixty international conference proceedings. He is a senior member of the Optical Society.

Antonio Teixeira obtained a Ph.D., partly developed at the University of Rochester, USA, from the University of Aveiro, Portugal, in 1999. He holds an Executive Certificate in Management and Leadership from the MIT Sloan School of Management, Massachusetts, USA, and a post-graduate degree in Quality Management in Higher Education. He joined the University of Aveiro in 1999 and is presently a full professor and a senior research-

er in the Instituto de Telecomunicações. Since 2014, he has been the dean of the Doctoral School, University of Aveiro. Dr. Teixeira has worked at several industrial organizations, including Nokia Siemens Networks, Coriant, and PICadvanced, a startup in photonics that he cofounded that employs more than forty highly skilled persons. He holds eleven patents and has published more than 400 papers. He has supervised more than seventy MSc and fifteen Ph.D. students and has participated in more than thirty-five national and international projects.

# Contents

| Preface                                                                                                                                                                                                                                                                   | XIII |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Section 1                                                                                                                                                                                                                                                                 |      |

| Process and Component Optimization                                                                                                                                                                                                                                        | 1    |

| Chapter 1 Direct and External Hybrid Modulation Approaches for Access Networks                                                                                                                                                                                            | 3    |

| by Adebayo E. Abejide, Madhava R. Kota, Sushma Pandey,<br>Oluyomi Aboderin, Cátia Pinho, Mário Lima and António Teixeira                                                                                                                                                  |      |

| Chapter 2 MAS: Maximum Energy-Aware Sense Amplifier Link for Asynchronous Network on Chip by Erulappan Sakthivel and Rengaraj Madavan                                                                                                                                     | 25   |

| Section 2 Network Architecture and Design                                                                                                                                                                                                                                 | 37   |

| Chapter 3 Network-on-Chip Topologies: Potentials, Technical Challenges, Recent Advances and Research Direction by Isiaka A. Alimi, Romil K. Patel, Oluyomi Aboderin, Abdelgader M. Abdalla, Ramoni A. Gbadamosi, Nelson J. Muga, Armando N. Pinto and António L. Teixeira | 39   |

| Section 3 Microstructure Fabrication and Routing Optimization                                                                                                                                                                                                             | 65   |

| <b>Chapter 4</b> A Novel Approach for the Design of Fault-Tolerant Routing Algorithms in NoCs: Passage of Faulty Nodes, Not Always Detour by Masaru Fukushi and Yota Kurokawa                                                                                             | 67   |

| Chapter 5 Digital Control of Active Network Microstructures on Silicon Wafers by Zhongjing Ren, Jianping Yuan and Peng Yan                                                                                                                                                | 85   |

# Preface

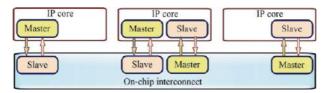

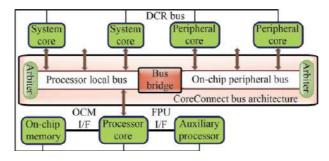

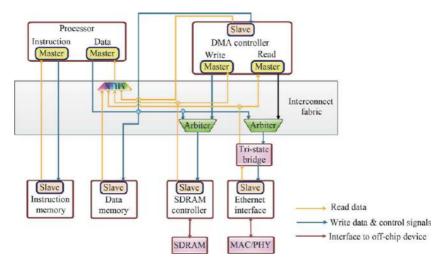

On-chip communication has been experiencing unprecedented pressure due to the huge amount of intellectual property (IP) cores that can now be integrated on a single chip. For traditional bus-based interconnections, the integration results in scalability and contention issues for on-chip communication. Based on this, they are limited and unable to effectively support the required inter-component communication in the System-on-Chip (SoC). Consequently, the major challenges in many core-based SoCs are related to scalability, flexibility, and a high-performance communication backbone.

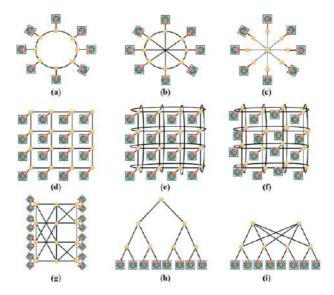

Network-on-Chip (NoC) has emerged as an efficient solution for offering the required architectural flexibility and parallelism to support the associated massive cores and IPs. In an NoC system, communication between the cores is a router-based packet-switched transmission. Based on this, for an optimum trade-off between flexibility and energy efficiency, there has been an increase in the implementation of NoC architectures for on-chip communications in embedded multicore processors such as Multiprocessor SoCs (MPSoCs), Chip Multiprocessors (CMPs), and Graphics Processing Units (GPUs). In addition, multicore processing is attractive for power reduction in general-purpose computing and embedded systems.

This book covers the fundamental concepts and the state of the art of NoC architecture. This comprises the exploration of process and component optimization. It also focuses on the cost-effective and appropriate combination of components and processes. In this context, hybrid modulation can be employed for Photonic Integrated Circuits (PICs) to ensure high-performance communication. A traffic-aware sense amplifier can also be employed in an NoC system to alleviate energy consumption. Furthermore, the book focuses on various network architecture and designs for NoC systems. In this regard, recent advances in design-friendly, scalable, flexible, and high-performance interconnection architectures are presented along with the associated technical challenges and research direction for design optimization. Moreover, microstructure fabrication and routing optimization are also covered in this book, as the employed routing algorithm can significantly influence the overall network performance metrics regarding latency and throughput.

In general, this book not only presents underlying concepts, features, and related evolutions but also clarifies the fundamental technical principles of on-chip communications with good insights into future NoC systems. The information presented is easy to follow, concise, and comprehensible. It comprises both theoretical and practical areas of system implementation. This makes it suitable for students, researchers, and professional engineers. It is also a good reference for all interested readers who wish to keep abreast of the current trends in on-chip communications, especially NoC systems.

The editors would like to acknowledge and appreciate all the contributing authors. Their works and innovations in different areas of NoC systems are highly appreciated. The editors would also like to thank IntechOpen for the invitation to participate in this project.

Isiaka A. Alimi, Oluyomi Aboderin and Nelson J. Muga Instituto de Telecomunicações, Aveiro, Portugal

#### António L. Teixeira

Department of Electronics, Telecommunications and Informatics, University of Aveiro and the Instituto de Telecomunicações, Aveiro, Portugal

# Section 1 Process and Component Optimization

#### **Chapter 1**

# Direct and External Hybrid Modulation Approaches for Access Networks

Adebayo E. Abejide, Madhava R. Kota, Sushma Pandey, Oluyomi Aboderin, Cátia Pinho, Mário Lima and António Teixeira

#### **Abstract**

The demand for low-cost high-speed transmission is a major challenge for 5G future networks. To meet this optical communication demand, holistic and painstaking approaches are required in designing a simplified system model. Since the demands for high bandwidth are growing at unprecedented speed as we approach the Zettabyte era, it is crucial to minimize chromatic dispersion (CD) associated to high bit-rate signals. Mitigating CD electronically comes at high cost which may not be compatible with 5G. Photonic Integrated Circuit (PIC) as an enabler for fast speed optical transmission is still undergoing its growth stage and its major speed and efficiency have not yet been attained. However, proper and right combination of components and approaches can potentiate this technology in a more costefficient way. Hybrid modulation (HM)-PIC presents a simplified approach in terms of cost and efficiency for 5G networks. Hybridization of existing modulation components and approaches in PIC can enhance the generation of high bit-rate signals without the need for electrical CD compensation. A detailed study of hybrid multilevel signal modulation concept as a valuable solution for Data Centers (DC) high data-rate signals and next-generation Passive Optical Networks (PONs) is proposed.

**Keywords:** photonic integrated circuits (PIC), hybrid modulation (HM), direct modulation laser (DML), external modulation laser (EML), simplified high bit-rate signal generation, chromatic dispersion (CD), insertion loss (IL), chirp managed lasers (CML), optical spectrum reshaper (OSR)

#### 1. Introduction

In the era of explosive demand for bandwidth and complex broadband transmission attributed to the fifth-generation (5G) and beyond, strategic positioning of fiber optics communications is imperative considering its huge advantages in terms of high-speed transmission, simplified design and low cost implementation [1].

Fiber Optics communication, which is carried out through photon, has been a promising approach that can conveniently guarantee the requirements of high data transmission. However, the existing technologies will require complete

overhauling, upgrading, or redesigning for effective results [2]. Unarguably the 5th and 6th generations of wireless networks cannot sufficiently guarantee their expected output in terms of speed, latency and spectral efficiency without improved channel architectures.

Therefore, there is an urgent need to further optimize optical properties to meet the current and future demands for high-speed data communications [3]. Fiber optics on its own with peak-to-peak throughput of 100 Gb/s is unique among other communication channels, and as of today, its capacity in terms of speed and convenience of communication has not been fully utilized [1].

Similarly, PIC as an enabler for optical communications presents a promising approach for conveniences of communications in terms of low footprint, low cost implementation, and very high speed [2, 4]. Therefore, increasing data rate and mobility in the evolving technologies require an increase of data traveling in the networks, introducing new requirements (e.g., speed and latency) for the components, e.g., PIC building blocks (BB). Although, PIC components under terahertz speed is a promising technique to guarantee the requirements of future networks, the maturation of the integrated photonics is still ongoing.

Furthermore, to strengthen the position of fiber optical communications for the emergence of hyperscale future transmission such as hyperscale data centers (HDCs) and to continually improve the amount of data transmission over optical networks through modulation and multiplexing approaches, this chapter will address a detailed description of DML and EML modulation schemes, and improved hybrid approaches, a valuable solution to attain the overcoming requirements of high-speed signal transmissions.

Conventional approaches are carried out through direct modulation laser (DML) and external modulation laser (EML) respectively which cannot guarantee the demands of future networks due to their respective limitations [2, 5, 6]. Although DML is simple in design and can generate high power budget when properly optimized but, the signal is degraded due to high CD, induced adiabatic chirp, phase noise, and low extinction ratio (ER). Consequently, these limit DML transmissions to a short distance of about 10 km and its inability to cope with high bit-rate transmissions [5–7].

EML on the order hand outperforms DML with reduced chirp and better reach. Nevertheless, the signal is also limited due to size, low optical power and high driving voltage among others [2, 8, 9]. Hence, a hybrid combination and optimization of these modulation processes can be seen as a powerful approach.

With the HM method, high bit-rate signals can be generated in a simplified way with a low footprint, low energy consumption and less complexity in meeting the demand for future networks [2].

This chapter provides a detailed study of the development and optimization of a simplified optical transceiver for high data rate 5G optical transmission, in order to manage future competitive markets necessities in its migration to 100G and 400G Ethernet, by replacing the single-mode 10G-SFP+ used for 4G networks. Moreover, the access and aggregation layers patterned with Dense Wavelength Division Multiplexing (DWDM) transceivers having bit-rate as high as 400G designed for metro access, metro convergence and core layer access networks, are also studied.

With HM approach, simplified and high bit-rate intensity modulated signals can be generated without electrical pulse shaping, digital to analog conversion (DAC), and digital signal processing (DSP) compensation [2].

The remaining part of this chapter is arranged as follows: in section 2, details signal modulation approach for PIC is discussed follow by section 3 where we presented the novel HM approach and the results of our simulations. We draw the conclusion in section 4.

#### 2. Signal modulation in PIC

The crucial function of modulators in optical communications is the conversion of the electrical information input signal into its corresponding optical domain which is placed on the optical signal as a carrier before being launched into an optical communications channel. This process is carried out in the optical transmitter, where an optical signal from an optical source such as a semiconductor laser or light-emitting diode (LED) is either directly or externally modulated. Optical signal has three major properties which are amplitude, frequency and phase. However, the message electrical signal is biased to manipulate any of these optical properties so that information can be sent along optical channels [2, 9].

Modulation of the optical carrier properties mentioned above could be done directly or externally [5]. Direct modulation is achieved using a DML [8], while the external modulation, which is equally referred to as external modulation laser (EML), can be either through electro-refractive using Mach Zehnder Interferometer (MZI) [9] or electro-absorption using an electro-absorption modulator (EAM) [7, 9].

The simplicity of design and cost [9, 10] make DML a preferred choice, none-theless several constraints make it undesirable for high bitrate and long-distance transmission [7]. These constraints include low bandwidth, low efficiency, CD caused by induced chirp which imposes signal phase noise, refractive index change of the active layer by carrier density modulation and relatively low ER [5, 6]. DML induced chirp can be transient or adiabatic. Chirp due to transient gives a nonlinear gain which occurs during the bit transitions, while the adiabatic chirp is the spontaneous emission that occurs in the laser, which is responsible for the blue-shifting of bit 1 relative to bit 0 [11]. As a result, the increase of bit-rate in DML causes the signal to suffer a very pronounced pulse broadening due to CD [6], mainly when the bit-rate is increased beyond 10 Gb/s [12]. The chirp in DML is mainly influenced by the linewidth enhancement factor, which is also known as Henry factor limiting within 2 and 8 for DFB laser, and consequently, the signal of 10 Gb/s transmission could not go beyond 10 km [13].

On the other hand, external modulation approaches can achieve high ER, high data-rate, and lower modulation distortion. Unfortunately, this comes with additional system complexity and cost compared to direct modulation [14]. For the external modulation, EAM offers lower cost and size combining with a considerably higher speed when compared to MZI [9, 15]. EAM can achieve better speed with low CD as a result of its zero or negative chirp [6] with the inherent advantage of low driving voltage and the possibility of monolithic integration with a DFB laser on a single waveguide, which reduces channel insertion loss (IL) [9, 16, 17]. Furthermore, EAM optical modulation does not affect the laser properties unlike DML [7] and its low CD can achieve improved speed (25–40 Gb/s) and longer distance (10–40 km) [7, 9]. Additional details regarding the two technologies are provided in the subsections 2.1 and 2.2. Presented results were attained by VPIphotonics® transmission simulations.

#### 2.1 DML signal generation

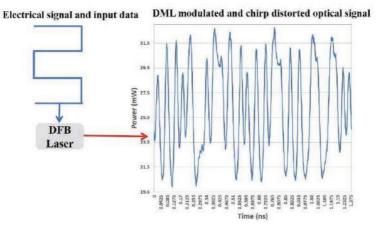

In this approach, an electrical signal is directly injected into the lasing cavity in an attempt to manipulate the stimulated emission present in the laser cavity. By this, a high-frequency electromagnetic signal with information could be sent via optical channel after modulation [9, 14]. **Figure 1** gives an illustration of how the DML approach can be achieved and its chirp effects.

Practically, semiconductor lasers such as distributed feedback laser (DFB), constricted-mesa lasers and Fabry-Perot (FP) lasers are the major lasers used for

**Figure 1.**DML showing electrical signals without chirp before modulation and optical signal after modulation with chirping effect.

DML purposes. It is important to note that DML is simple and cost efficient but can only be applied with low bit-rate and short-reach as a result of chirp due to spectral broadening associated with the biasing current during modulation. This is due to accompanying phase modulation (PM) to the desired intensity modulation (IM) during this process [18]. The level of the chirping imposed on the modulated pulse largely depends on the driving condition ( $I_{\rm bias}$  and modulation current ( $\Delta I$ )) and the laser type.

#### 2.1.1 DML chirping effects

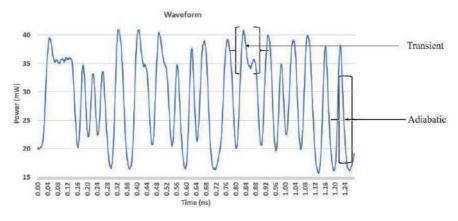

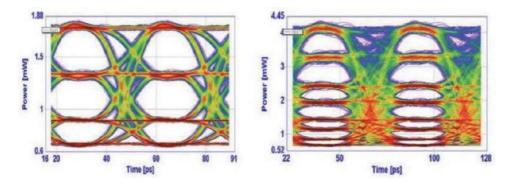

The chirp associated with DML can be subdivided into transient and adiabatic chirp as depicted in **Figure 2**. The presence of chirp in the modulated pulse leads to high CD and invariably inter-symbol-interference (ISI) which adversely weakens the reach and effects of DML transmission.

According to [19], transient chirp is associated with the relatively small frequency difference between the steady-state of signal pulse levels of ones and zeros. This frequency difference leads to ringing and significantly obvious overshooting of optical output power and frequency deviations.

Figure 2.

DML power time domain response showing transient and adiabatic chirp.

Adiabatic chirp at the same time can be described with the damping oscillations and large frequency differences between pulse ones and zeros.

Compensating the chirp and CD in DML comes with its own cost and complexity. Some of these approaches are the use of dispersion compensation fiber (DCF), electrical signal compensations through decision feedback equalizer (DFE), feedforward equalizer (FFE), continuous-time linear equalizer (CTLE), digital signal processing (DSP), electrical pulse shaping and finally, optical CD compensation through optical spectrum reshape (OSR) [20]. This OSR method is better detailed in the subsection 3.3.

Nevertheless, progressive works to reduce the effect of chirp on DML show improved results. For instance, in [21], an InGaA1As/InGaA1As multi-quantum well (MQW)-DML was grown on an n-doped InP substrate by shortening the laser cavity length to less than 150  $\mu m$  via positioning of a passive waveguide in the front of the DFB laser. The DML was operated at 45 mA driving current with 43 Gb/s bitrate, the optical signal obtained after 40 km presents a clear eye signal at 25 °C which shows an improved bit-rate possibility higher than 10 Gb/s over DML.

Similarly, the research work in [22] also presents a 40 Gb/s DML optical signal that used passive feedback laser (PFL) realized around 1300 nm and 1550 nm wavelength region. In this work, DFB and integrated passive feedback section (IPF) were combined enabling the suppression and control of the phase feedback field with the modulation performance of the stationary operating laser.

Other works in [23–25] also present similar improvements in the design of DML with higher bit-rate and improved fast speed transmission. The authors in [23] used InP-on-Si to achieve 45 Gb/s and 25 GHz 3-dB modulation bandwidth at a relaxation oscillation frequency of 10 GHz using NRZ encoder. The fabricated laser has two sections of around 250  $\mu m$  each with an active region on InGaAsP separate confinement hetero-structure (SCH). A clear eye diagram after a 2 km transmission of 45 Gb/s was obtained with BER lower than 7% Hard Decision (HD) forward error correction (FEC) and received optical power (ROP) around -7 dBm.

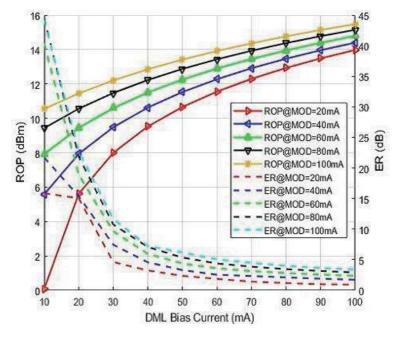

#### 2.1.2 DML signal optimization

To further investigate the behavior of DML, we carried out a simulation study of a rate equation model of a semiconductor DFB laser. In order to reduce the effect of the unwanted transient chirp on the modulated signal, it is highly advised to bias the laser far away from the current threshold [9, 26], allowing to obtain high optical output power after modulation. Although, this is a trade-off with the optical signal ER. In our case, the laser current threshold is obtained around 10 mA and as we biased away from this point, the output optical signal increases with reduced transient chirp while the signal ER reduces.

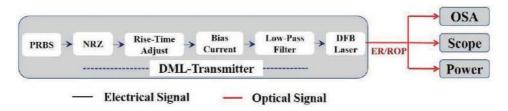

The block diagram for an intensity DML is presented in **Figure 3** and the DML parameters used are summarized in **Table 1**.

**Figure 3.** Block diagram of a DML characterization bench.

| Simulation Parameters              | Value   |

|------------------------------------|---------|

| BitRate                            | 10 Gb/s |

| Wavelength                         | 1.57 μm |

| Laser Bias Current                 | 90 mA   |

| Laser Confinement Factor           | 0.5     |

| Henry Linewidth Enhancement Factor | 3.0     |

**Table 1.** *DML simulation parameters.*

A non-return to zero (NRZ) electrical modulation scheme is supplied with pseudorandom binary sequence through modified Wichman-Hill generator with length M bits = TimeWindow\*Bit-Rate, which is applied on the DFB laser while biasing at given current in order to modulate its amplitude [27]. The transmitted optical pulse after modulation for the giving rate equation laser is expressed by Eq. (1).

$$A(t)_{DML} = I_{bias} + \sum_{k=-\infty}^{\infty} A_D I_{pulse}(t - kT)$$

(1)

Where  $A(t)_{DML}$  is the modulated optical pulse from the DML transmitter,  $I_{bias}$  is the bias current,  $A_D$  is the PRBS data sequence of the form zeros and ones, each indexing with k,  $I_{pulse}$  is the encoding signaling format used (return to zero (RZ), NRZ, etc.), and T the bit period.

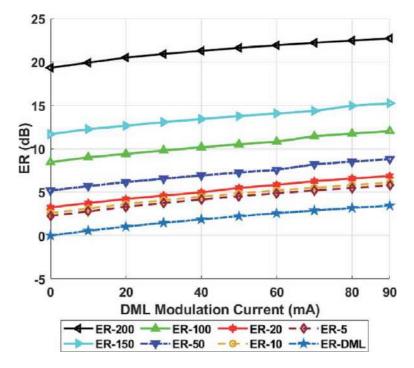

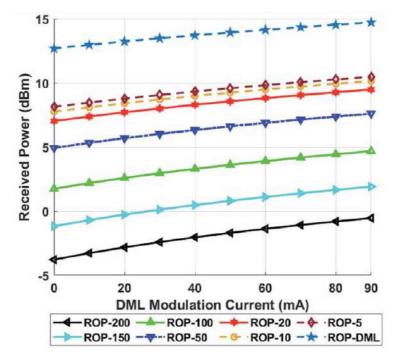

The received optical power (ROP) and ER at different laser modulation current and bias are depicted in **Figure 4**. In section 3, this obtained result will be optimized through our simplified HM approach.

**Figure 4.** *ER and ROP variation against DML biasing current.*

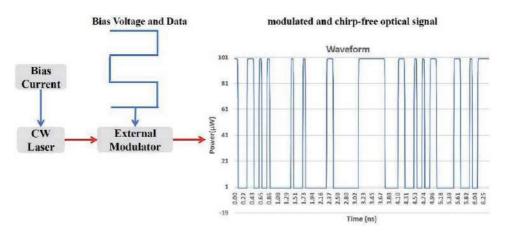

#### 2.2 EML signal generation

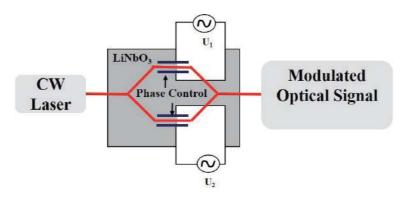

EML signal generation as an alternative to DML can eliminate significantly the frequency chirp effect associated with direct modulation scheme [9]. The procedure requires a continuous wave laser (CW-laser) providing constant optical signal into the external modulator and an external electrical signal is applied to manipulate any of the desired properties (intensity, phase and frequency) of the light. A standard EML operation mode is depicted in **Figure 5**, comprising the CW laser, external modulator and the external electrical driving voltage.

As mentioned in the introduction section, two main approaches of external optical modulation are: i) the electro-refractive (LiNBO3 MZM); and ii) the electro-absorption (EAM) [13]. We shall briefly discuss design approaches and the mode of operations of these devices.

#### 2.2.1 MZM

The overall behavior of the MZM as presented in **Figure 6** largely depends on its design and configuration, e.g., based on the lithium niobate crystal. A good design MZM has high ER with low chirp, which requires high driving voltage. The amount

**Figure 5.** Block diagram of an external modulation laser.

**Figure 6.**Typical mode of operation of a MZM modulation scheme.

of driving voltage will then result in a large dependence of device's efficiency [22]. This voltage effect can be translated by MZM power transfer function in Eq. (2).

$$P_0(t) = \alpha_M P_i \cos \left\{ \frac{\pi V(t)}{2V_{\pi}} \right\} \tag{2}$$

Where  $P_0(t)$  is the transmitted optical power from the output of the interferometer,  $\alpha_M$  is the modulator total IL,  $P_i$  is the input optical power from the CW laser to the modulator, V(t) is the time-dependent externally applied electric voltage, and  $V_\pi$  the driving voltage to exert a  $\pi$  phase shift on the light wave carrier along the optical path of the modulator. The major drawback comparing with EAM modulation schemes is its bigger size and high driving voltage requirements, which makes it more expensive to design and with larger footprint in the integrated circuit [9].

#### 2.2.2 EAM

EAM is considered an attractive modulation approach for fast-speed optical communications due to its low driving voltage, high bandwidth, high modulation efficiency and the possibility of monolithic integration with other semiconductor devices [28, 29]. EAM is an intensity modulator that changes the absorption properties of the carrier optical signal through the application of voltage V(t) around the band edge of the waveguides [9, 30].

Unlike MZM that modulates both intensity and phase of the carrier signal, EAM as an intensity modulator shows additional advantages, e.g., its linearity in the amplitude multilevel modulation, which offers lower total harmonic distortion when comparing to the MZM [9]. Nevertheless, MZM can achieve higher ER, an EAM with similar ER would imply increase size and therefore increase IL [9, 14].

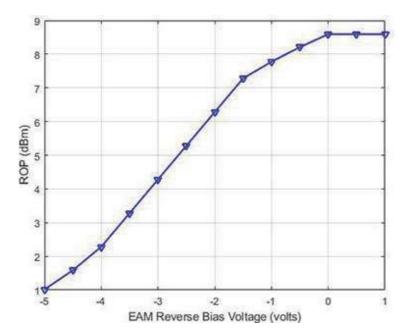

The driving of EAM is attained with negative bias voltage to guarantee an efficient light absorption of the modulator [9]. To work in the linear region of the EAM we choose the driving voltage range [-4 V to -1.5 V], see **Figure 7**.

Figure 7. EAM ROP vs. V curve. Linear region can be spotted between -4 V and -1.5 V (laser power = 10 dBm).

Biasing the modulator must be kept within the linear region to prevent signal distortion [30]. However, voltage biasing here presents a trade-off between modulation efficiency (eye-opening) and the EAM linearity limit. With higher amplitude, EAM linear region can be extended but this will sacrifice signal efficiency with the distorted eye. In our case for 50  $\mu m$  long EAM, the bias voltage is fixed at -3 V with a linear region between -4 V and -1.5 V and the voltage swing of 1.5 V.

In the design of EAM, two major approaches are employed: i) a bulk process through Franz-Keldysh Effect, and ii) a Multi-Quantum Well (MQW) through Quantum Confined Stack Effect (QCSE) [9, 31]. Investigations show that MQW-EAM is preferred over Bulk-EAM due to its large absorption coefficient [16, 28, 31–34], leading to higher ER [35].

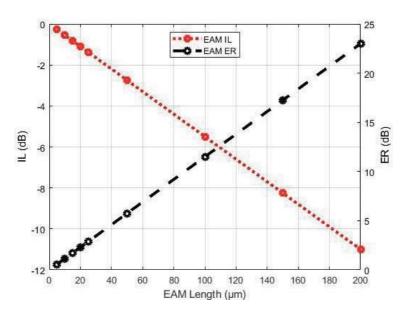

Considering EAM parameters from published studies [2, 32, 35–38], we simulated the modulation amplitude transfer function T(t). EAM inherent properties used as a figure of merit for a wavelength of 1.57  $\mu m$  and EAM of 200  $\mu m$  in length, were 0.055 dB of IL and 0.115 dB of ER per 1  $\mu m$  length of EAM. Therefore, an increase of EAM ER (and thus EAM length) is given at the expense of an IL increase. This is a major setback for the use of EAM in EML modulation schemes.

Furthermore, we simulated T(t) parameters interpolation to mimic the behavior of 200  $\mu$ m EAM and obtained T(t) against V(t) for different EAM length at 1.57  $\mu$ m optical wavelength based on the properties of EAM length stated above.

The obtained results of EAM length versus its IL and ER are provided in **Figure 8**.

The compromise between EAM IL and ER, by changing EAM size, allow us to reach the necessary requirements of our optical transmitter, essential information to model our hybrid transmitter as presented in the section 3.

Operation of EML through the EAM intensity modulator stated here can be expressed by Eq. (3).

$$A(t)_{EML} = T(t).A(t)_{cw} \tag{3}$$

Figure 8. EAM ER and IL versus EAM lengths. For the ER values, the EAM was biased at -4 V and modulated at 0 V.

Where  $A(t)_{EML}$  is the modulated optical signal output from EAM, T(t), the complex field-intensity transmission function which depends on the length of EAM and the bias voltage while  $A(t)_{cw}$  is the constant optical carrier signal supplied by the CW laser. T(t) can be specified in dB by squaring its magnitude giving by

$$T(t)_{dB} = 10.\log\left(\left|T(t)\right|^2\right) \tag{4}$$

The modulating voltage v(t) and the bias voltage  $V_o$  which are used for electrical driving of the modulator are related to T(t) according to Eqs. (5) and (6).

$$V(t) = V_o + v(t) \tag{5}$$

$$T(t) = T(t)_{dR} \cdot V(t) \tag{6}$$

#### 3. Hybrid modulation (HM)

An obvious treat on conventional communication procedures with the current BB which leads to high system impairment and overloads has led scientific community to think further on the prospect of hybrid combination of processes and components [39]. This approach can be implemented monolithically in an InP-based platform, allowing higher spectral efficiency and the ability to generate high bit-rate signals [40].

Different limitation can be addressed for DML and EML modulation schemes. For instance, DML can only be used for relatively lower speed ≤25 Gb/s and cannot be transmitted beyond 10 km for data-center interconnect (DCI) and passive optical networks (PON) systems [7]. On the other hand, external modulation through EAM is limited by high IL values to address requirements of high ER [2]. Combining the advantages versus limitations of these two modulation schemes can result in improvements of the overall signal generation for DCI and PON systems, by mitigating the problems of transmission loss and group velocity dispersion (GVD).

Past works on optimization of transmission efficiency are associated with costly and complex system designs [22–25]. Hence, a procedure to reduce or eliminate these limiting factors are vital to the success of 5G deployment. Since PIC is still undergoing its maturity stage, its best design, functionality and efficiency are still under research. Several approaches used for impairment compensation can be optimized through hybrid combinations of BBs. In this work, we have conducted extensive studies and simulations of procedures for signal generations through direct and external modulation schemes. DML limitations have been discussed in section 2.1. External modulation on the other hand presents an attractive alternative to DML although, nevertheless with the constrain of high IL, which requires a laser with enough output power to overcome this loss.

Thus, HM concept appears as a useful approach, by exploring the advantages of both direct and external modulation approaches and components functionalities to produce a full integrated system. One major obstacle in the proposed hybrid combination is the presence of short noise dominated by photons from the DML due to spontaneous emission and the electron–hole recombination which significantly reduces the signal-to-noise ratio (SNR) of the hybrid transmitter [9]. We have provided a measure to reduce this noise and also reduce the transient chirp in the DML pulse through optical signal reshaper (OSR) approach which will be presented later in this section.

#### 3.1 HM-model

Modulated optical signal from DML is launched into the optical signal input of the characterized EAM under study in order to re-modulate the optical signal for intensity signal generation. The T(t) earlier described in Eq. (6) that depends on the driving bias voltage and length of the modulator is loaded as a data file through VPIphotonics transmission maker optical simulator to control the EAM [41]. Therefore, for HM-model, Eq. (3) can be rewritten as presented in Eq. (7)

$$A(t)_{HM} = T(t) \cdot A(t)_{DML} \tag{7}$$

From the Eq. (3) We have replaced the  $A(t)_{cw}$  with  $A(t)_{DML}$  obtained from Eq. (1) which is the modulated optical signal launched from the DML and  $A(t)_{HM}$  is the output of the hybrid transmitter.

T(t) enables us to control and decide on the length of the modulator that is sufficient to guarantee the desire ER and with the biasing of the DML current, we can adjust the power budget to compensate the IL imposed by EAM as a result of modulator length.

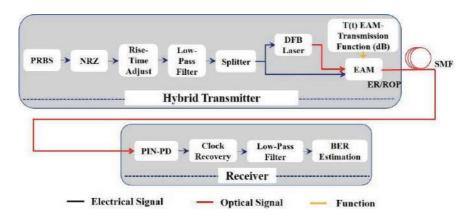

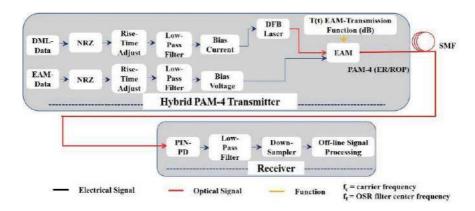

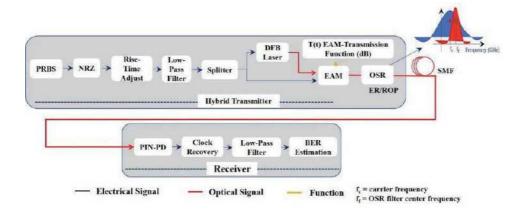

The corresponding schematic is presented in **Figure 9**. It consists of PRBS and NRZ electrical signal encoder used for driving DML. In the case of HM, the electrical signal is split into two to drive both DML and EAM. the EAM amplitude is configured with reverse bias voltage of -3 V which fall within the EAM linear region.

The obtained signal  $A(t)_{EAM}$  can be optimized with high ER and power budget sufficient for DCI and PON. The optimization of our hybrid modulator was done with optical wavelength at 1.57  $\mu$ m where we obtained the parameters for EAM characterization.

The measured ER and ROP by changing the length of EAM and modulation current at fixed bias (90 mA) current of DML are presented in **Figure 10** and **Figure 11** respectively. The DML ROP and ER before launching the optical signal for intensity modulation are also highlighted on the graphs.

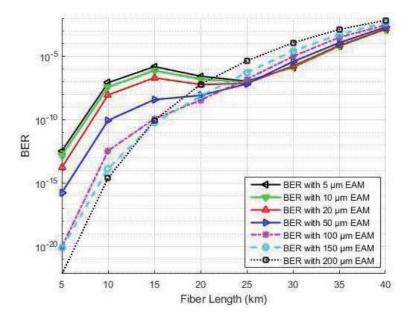

We further launched the optical signal at different EAM lengths tested into optical distribution networks (ODN) ranging from 5–40 km in order to study the behavior of the signals and responses to dispersion and non-linearity in the fiber, see **Figure 12**. With increased EAM length, the signals present an improved error rate from the 5 km starting point up to 20 km which is attributed to high ER.

**Figure 9.**Simulation setup for HM approach.

Figure 10. ER at hybrid transmitter's output for different EAM-length against DML modulation current: EAM bias,  $V_o = -3 \, V$ , EAM voltage swing,  $v(t) = 2 \, V$ , DML Bias = 90 mA.

Figure 11. ROP at hybrid transmitter's output for different EAM-length against DML modulation current: EAM bias,  $V_o = -3$  V, EAM voltage swing, v(t) = 2 V, DML Bias = 90 mA.

Figure 12.

BER and ROP versus fiber length for optical signals stemming from EAM with different lengths.

However, since higher ER also contributes to higher IL coupled with the attenuation in the fiber, the signal with lower EAM length (EAM = 5  $\mu$ m) gives a better error rate than when EAM length is 200  $\mu$ m as we continue to increase the length of the fiber as presented in **Figure 12**. At 40 km all the signals from different EAM lengths tested were received at an error rate less than  $10^{-3}$ .

#### 3.2 Simplified high bit-rate multilevel signal generation

Short reach fiber optic communication such as PON, short-reach video on demand (VoD) and DCI have recently advanced the demand for bandwidth [42]. This demands more efficient and advanced high spectral modulation format to replace the conventional NRZ line code [43] in order to guarantee high data rate beyond 50 Gb/s per channel [41, 44]. IEEE 802.3 group quad small form-factor pluggable (QSFP) 400 Gb/s specifications for short-reach data center communication systems have been studied progressively. Better data rate usage such as 56 Gb/s per channel can help to reduce system design complexity and cost [44–46]. Studies show that access, aggregation and core networks bandwidth demand in 5G can be adequately guaranteed with 400 Gb/s PAM-4 signal generations with either 56 Gb/s 8-channel or 100 Gb/s 4-channel networks [47, 48]. With this provision, some key requirements of 5G networks such as low cost, high performance and high bandwidth can be adequately guaranteed.

PAM-4 is a multi-order modulation approach which presents a bit-rate twice of the NRZ signal line code under the same baud-rate using four levels for signal transmission with two bits of logical information per each clock period [48]. However, PAM-4 presents a high degree of complexity in the signal generation, coupled with its sensitivity to amplitude noise which leads to a high signal to noise ratio (SNR) [45]. This is because PAM-4 signal have four levels with three eyes, which implies that, its signal is generated with an amplitude (A) of A/3 compared to NRZ that has a SNR = A. With this deficiency, PAM-4 signal is at least three times more sensitive to amplitude noise than NRZ.

To generate a PAM-4 signal for optical communication however, some complex system designs are used. In [48], physical coding sub-layer (PCS) is used to support forward error correction (FEC) at both transmitter and receiver for signal coding/ encoding, scrambling/descrambling, signal alignment, signal sorting and control. Another important signal efficiency enhancement procedure is the use of electrical digital to analog converter (DAC) at the transmitter and receiver [43]. DAC usage also comes with some degree of nonlinearity and power greediness that can limit their usefulness for multi-level modulation scheme like PAM-4 in a cost effective system [48]. If nonlinearity of signal is not eliminated or reduced, it usually leads to signal distortion, which will require additional pre-distortion management procedures such as static pre-distortion (SPD) and dynamic pre-distortion (DPD) for non-linearity compensation [49]. The digital signal processing (DSP) for distortion and dispersion compensation as presented in [49, 50] to eliminate power fading high-frequency signals have further complexity in conventional PAM-4 signal generations that contradict 5G requirements for low cost signal generation approaches.

In [51], feedforward equalizer (FFE) and decision feedback equalizer (DFE) are employed at both transmitter and receiver to cancel the multi-level signal ISI and this is accomplished with system complexity and cost. To mitigate some of the complexity in PAM-4 signal generations in order to meet the demand for low cost, energy-efficient and low footprint demand for 5G networks, optical DAC PAM-4 signal generation was used in [44] with high tolerance to modulation nonlinearity. In terms of distance covered also, modulation through DML with high bit-rate signal shows several limitations due to the high chirp associated with its signal coupled with the lagging of lower PAM-4 eye while transmitting with high bit-rate and high modulation current [46]. Although, DML approach shows the simplest and most cost-effective measures but highly limited to low bit-rate and shot reach.

However, in our approach to eliminate these aforementioned limitations in PAM- 4 signal generation, unlike the conventional signal generation with EAM where electrical PAM-4 signal is employed to generate optical PAM-4 signal, the concept of HM approaches for NRZ signal generation we presented in [2] is further employed to generate optical PAM-4 signal. The approach is optimized in a simplified way to generate the signal for short reach transmissions without signaling, nonlinearity and CD compensation. The complete simulation setup is presented in **Figure 13**. We conducted further optimization of our HM model to design 28-GBaud PAM-4 signal and in fact, the same approach was tailored towards

**Figure 13.** Schematic of the simplified multilevel (PAM-N) signal generation approach through HM model.

Figure 14. Eye diagram of 28 GBaud PAM-4 and 20 GBaud PAM-8 signals generated with simplified HM approach. Here the PAM-4 signal has an ER = 4.5 dB and PAM-8 signal with ER = 7.5 dB, both signals having ROP higher than 4 dBm.

generating a simplified 20-GBaud PAM-8 signal eliminating the conventional complexity of electrical signal coding and pulse shaping.

Both transmitters show an optical launch power of more than 4 dBm with 5 dB and 7.5 dB ER respectively. At the receiver, the multilevel signals are decoded through direct detection approach with a PIN photodetector. The eye diagrams of both PAM-4 and PAM-8 signals generated with this approach are presented in **Figure 14**. The results of transmission over 8 km of both the 28 GBaud PAM-4 and 20 GBaud PAM-8 obtained through offline digital signal processing using Gaussian approximation give error analysis below  $10^{-3}$ .

#### 3.3 DML CML-OSR for hybrid signal compensation

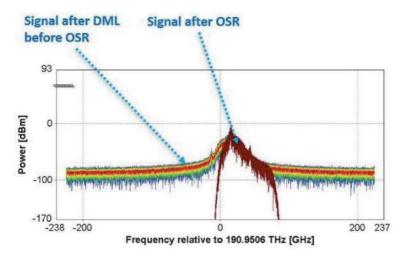

The major effect of DML is the associated phase modulation to the intensity modulation, which results in CD and then ISI. In the HM model, some degree of chirp is still present in the modulated signal, which introduces limitations. With the concept of chirp managed lasers (CML) through optical signal reshaper (OSR), the transient chip from the DML can be reduced. More also, since our DML optimization earlier presented is tailored towards improving the optical signal power output and reducing the transient chirp by biasing away from the threshold. This reduces the signal ER. With the concept of CML, the ER of the DML optical signal can be optimized as well as the transient chirp. An update to the schematic in **Figure 9** is presented in **Figure 15** including a Gaussian optical filter optimized as an OSR.

The entire CML-OSR approach can be studied in [52–55]. The concept of CML decouples optical signal power and chirp of the DML signal [53], which is achieved by configuring the Gaussian filter as a band-pass filter (BPF) having a central frequency higher than the frequency of the carrier signal. This enables the filter to undergo signal edge filtering by suppressing the 1-bit while attenuating the 0-bit of the distorted NRZ optical pulse from DML. The filter is configured with a 3 dB bandwidth lower than the bandwidth of the carrier signal which distorts the signal but at the same time cut-off most of the high-frequency noises associated with the optical signal pulse. Hence, the bandwidth is highly significant to the overall performance of the OSR but care must be taken in using this approach for hybrid multilevel signal generations (e.g., PAM-4 and PAM-8) if the OSR bandwidth is further reduced or if the filter central frequency is further increased. The behavior of this approach is shown in **Figure 16** while the simulation parameter is also presented in **Table 2**. Applying this model on our generated HM optical signal

**Figure 15.** *Hybrid simulation approach* + *CML-OSR.*

Figure 16. CML-OSR showing DML signals before and after OSR filtering.

| Filter Parameters       | Value        |

|-------------------------|--------------|

| Filter Type             | BandPass     |

| Transfer Function       | Gaussian     |

| Filter Center Frequency | 190.99e12 Hz |

| Filter Bandwidth        | 60 GHz       |

| Gaussian Order          | 4            |

Table 2. CML-OSR simulation parameters.

improves the signal ER which further improves the overall performance of the final optical signals from the hybrid transmitter. More also, the filter significantly reduced the transient chirp associated with the DML signal. We applied this concept to both the binary and multilevel signals generated in our earlier sections and significant improvement in terms of reach was observed. With OSR, we were able

to transmit a binary 40 Gb/s HM signal beyond 40 km and both 28 GBaud PAM-4 and 20 GBaud PAM-8 signals respectively up to 10 km.

#### 4. Conclusion

We have proposed and demonstrated the concept of simplified high bit-rate signal generation with a HM approach in this chapter. The current 5G and the beyond technologies specifically target such a model with less complexity but unprecedented spectral efficiency in order to reduce the capital expenditure (CAPEX) and operation expenditure (OPEX) of signal transmission and at the same time guarantee the speed requirements of the application over optical communication networks. Through simulations, we have demonstrated and shown that there is a clear path to achieve 5G backhauling without the need for CD pre and post compensation for high bitrate signal generation in short and medium reach networks. We also showed that proper optimization can improve signal launch power and eliminate the necessity of expensive optical power amplifier for high bitrate signal transmission. HM clearly simplified signal generations as we have presented in this chapter with right combination of process and components. Further research is ongoing to implement this model on a PIC so that we can perform a real-life laboratory test of the chip and investigate other areas of optimizations.

#### Acknowledgements

This work is supported by the project Virtual Fiber Box, with reference number POCI-01-0247- FEDER-033910, funded by the European Regional Development Fund (FEDER), through the Operational Program Competitiveness and Internationalization (COMPETE 2020), of Portugal 2020 framework (P2020).

#### **Author details**

Adebayo E. Abejide<sup>1,2\*</sup>, Madhava R. Kota<sup>1,2</sup>, Sushma Pandey<sup>1,2</sup>, Oluyomi Aboderin<sup>1</sup>, Cátia Pinho<sup>1,3</sup>, Mário Lima<sup>1,2</sup> and António Teixeira<sup>1,2</sup>

- 1 Instituto de Telecomunicações (IT), University of Aveiro, Aveiro, Portugal

- 2 Department of Electronics, Telecommunications and Informatics (DETI), University of Aveiro, Aveiro, Portugal

- 3 PICadvanced, PCI-Creative Science Park via do Conhecimento, Edifício Central, Ílhavo, Portugal

#### **IntechOpen**

© 2021 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. (c) BY

<sup>\*</sup>Address all correspondence to: adebayo@ua.pt

#### References

- [1] Chowdhurry, Mostafa Zaman, et al. "The Role of Optical Wireless Communication Technologies in 5G/6G and IoT Solutions: Prospects, Directions and Challenges." Applied Sciences 9.20 (2019): 4367.

- [2] Adebayo E. Abejide, et al. "Hybrid Modulation Approach for Next Generations Optical Access Networks." Proceedings of CSNDSP Portugal, July 2020.

- [3] E. Saini, R. Bhatia and S. Prakash, "High speed broadband communication system for moving trains using Free Space Optics," 2016 International Conference on Computational Techniques in Information and Communication Technologies (ICCTICT), New Delhi, 2016, pp. 47–50.

- [4] A Teixeira, "Photonic Integrated Circuits for NG-PON2 ONU Transceivers" Optical Fiber Communication Conference (OFC), 2019.

- [5] Christophe Peucheret, "Direct and External Modulation of Light". DTU Fotonik, Department of Photonic Engineering, Technical University of Denmark, Denmark. November, 2009.

- [6] Fumio Koyama, Kenichi Iga, "Frequency Chirping in External Modulators". Journal of Lightwave Technology, Vol. 6, No. 1, January 1988.

- [7] EML vs DML for Datacenter and Client Side Transceivers. [Online]. Available: https://www.neophotonics.com.

- [8] Robbert Van der Linden. "Adaptive Modulation Techniques for Passive Optical Networks". Doctorate Thesis, Eindhoen University of Technology, Netherlands. April, 2018.

- [9] Le Nguyen Binh. "Optical Fiber Communication with Matlab and Simulink Models. Second Edition". Taylor and Francis Group, LLC, 2015.

- [10] Ning Hua Zhu Et al. "Direct Modulated Semiconductor Lasers". IEEE Journal of Selected Topics in Quantum Electronics. Vol. 24, No. 1, January 2018.

- [11] Z. F. Fan, "Chirp Managed Lasers: A New Technology for 10Gb/s Optical Transmitters," pp. 39–41, 2007.

- [12] International Telecommunication Union ITU-T. "PON transmission technologies above 10 Gb/s: Transmission Systems and Media, Digital Systems and Networks". Series G, Supplement 64, February, 2018.

- [13] H. Venghaus and N. Grote, "Fibre Opti Communication: Key Devices". Second Edition. Springer International Publishing, Switzerland, 2017.

- [14] Govind P. Agrawal, Fiber-Optics Communication Systems, Third Edition.

- [15] Dimension- "Directly Modulated Lasers on Silicon: Deliverable Report D 2.1", Report on System Specifications, Research and Innovation Actions (RIA), H2020-ICT-27-2015 Photonics KET. July, 2016.

- [16] Juan Camilo Velasquez Micolta, "Next Generation Optical Access Networks and Coexistence with Legacy PONs", Universitat Politecnica De Catalunya, Barcelona. July, 2019.

- [17] Hidekazu et al, "EAM-Integrated DFB Laser Modules with more than 40-GHz Bandwidth", IEEE Photonics Technology Letters. Vol.13, No. 9, September, 2001.

- [18] Yu, J., Jia, Z., Huang, M. F., Haris, M., Ji, P. N., Wang, T., & Chang, G. K. (2009). Applications of 40-Gb/s chirpmanaged laser in access and metro networks. Journal of Lightwave Technology, 27(3), 253–265.

[19] Tomkos, Ioannis & Chowdhury, D. & Conradi, J. & Culverhouse, D. & Ennser, K. & Giroux, C. & Hallock, B. & Kennedy, T. & Kruse, A. & Lascar, N. & Roudas, I. & Sharma, M. & Vodhanel, R.S. & Wang, C.-C. (2001). Demonstration of negative dispersion fibers for DWDM metropolitan area networks. Selected Topics in Quantum Electronics, IEEE Journal of. 7. 439–460. 10.1109/2944.962268.

[20] i, Philip N., Jianjun Yu, Ting Wang, Xueyan Zheng, Yasuhiro Matsui, Daniel Mahgerefteh, Kevin McCallion, Zhencan Frank Fan, and Parviz Tayebati. "Chirp-managed 42.8 Gbit/s transmission over 20 km standard SMF without DCF using directly modulated laser." In 33rd European Conference and Exhibition of Optical Communication, pp. 1–2. VDE, 2007.

[21] dokoro, Takashi & Kobayashi, Wataru & Fujisawa, Takeshi & Yamanaka, Takayuki & Kano, Fatima. (2011). High-Speed Modulation Lasers for 100GbE Applications. Optics InfoBase Conference Papers. 10.1364/OFC.2011.OWD1.

[22] Troppenz, U. & Kreissl, Jochen & Moehrle, Martin & Bornholdt, C. & Rehbein, W. & Sartorius, B. & Woods, Ian & Schell, Martin. (2011). 40 Gbit/s Directly Modulated Lasers: Physics and Application. Proceedings of SPIE - The International Society for Optical Engineering. 7953. 10.1117/12.876137.

[23] M. Shahin, K. Ma, A. Abbasi, G. Roelkens, G. Morthier, 45 Gb/s Direct Modulation of Two-Section InP-on-Si DFB Laser Diodes, IEEE Photonics Technology Letters, 30(8), p.685–687 doi:10.1109/LPT.2018.2811906 (2018).

[24] K. Otsubo, M. Matsuda, S. Okumura, A. Uetake, M. Ekawa and T. Yamamoto, "Low-driving-current high-speed direct modulation up to 40 Gb/s using 1.3-µm semi-insulating buried-heterostructure AlGaInAs-MQW

distributed reflector (DR) lasers," 2009 Conference on Optical Fiber Communication - incudes post deadline papers, San Diego, CA, 2009, pp. 1–3.

[25] M. C. Wu, C. Chang-Hasnain, E. K. Lau and X. Zhao, "High-Speed Modulation of Optical Injection-Locked Semiconductor Lasers," OFC/NFOEC 2008–2008 Conference on Optical Fiber Communication/National Fiber Optic Engineers Conference, San Diego, CA, 2008, pp. 1–3, doi: 10.1109/OFC.2008.4528483.

[26] Chan, Chun-Kit, Wei Jia, and Zhixin Liu. "Advanced modulation format generation using high-speed directly modulated lasers for optical metro/access systems." In 2011 Asia Communications and Photonics Conference and Exhibition (ACP), pp. 1–12. IEEE, 2011.

[27] R Coates, G. Janacek, and G. Lever, "Monte Carlo Simulation and Random Number Generation", IEEE J. Selected Areas Communication, Vol. 6, Pp. 58–66, 1988.

[28] Rashed, Ahmed Nabih Zaki. "Recent developments and signal processing of low driving voltage and high modulation efficiency electroabsorption modulators (EAMs)." International Journal of Image, Graphics and Signal Processing 4, no. 4 (2012): 11.

[29] M Theurer et al, "56Gb/s L-band InGaAIAs Ridge Waveguide Electro-Absorption Modulated Laser with Integrated SOA", Wiley Online Library. December 3, 2015.

[30] W.-J. Huang, C.-C. Wei, and J. Chen, "Optical dac for generation of pam-4 using parallel electro-absorption modulators," in ECOC 2016; 42nd European Conference on Optical Communication. VDE, 2016, pp. 1–3.

[31] Dazeng Feng et al, "High-Speed GeSi Electro-Absorption Modulator on

- SOI Waveguide Platform" IEEE Journal of Selected Topics in Quantum Electronics. November, 2013.

- [32] Moritz Friedrich, "Polarization Multiplexed Photonic Integrated Circuits for 100Gb/s and Beyond" Universitat Berlin, July. 2018.

- [33] Sheikhi, M. H., S. A. Emamghoreishi, S. Javadpoor, and M. K. Moravvej-Farshi. "A new theoretical design optimization of multiple quantum-well electroabsorption modulator." In IEEE/LEOS 3rd International Conference on Numerical Simulation of Semiconductor Optoelectronic Devices, 2003. Proceedings, pp. 17–18. IEEE, 2003.

- [34] Smit, Meint, Xaveer Leijtens, Huub Ambrosius, Erwin Bente, Jos Van der Tol, Barry Smalbrugge, Tjibbe De Vries et al. "An introduction to InP-based generic integration technology." Semiconductor Science and Technology 29, no. 8 (2014): 083001.

- [35] Mastronardi L, Banakar M, Khokhar AZ, Hattasan N, Rutirawut T, Bucio TD, Grabska KM, Littlejohns C, Bazin A, Mashanovich G, Gardes FY. High-speed Si/GeSi hetero-structure Electro Absorption Modulator. Opt Express. 2018 Mar 19;26(6):6663–6673. doi: 10.1364/OE.26.006663. PMID: 29609353.

- [36] M. Baier et al., "112 Gb/s PDM-PAM4 Generation and 80 km

Transmission Using a Novel

Monolithically Integrated

Dual-Polarization ElectroAbsorption Modulator InP PIC," 2017

European.

- [37] D. Feng et al., "High-Speed GeSi Electroabsorption Modulator on the SOI Waveguide Platform," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 19, no. 6, pp. 64–73, Nov.-Dec. 2013, Art no. 3401710, doi: 10.1109/JSTQE.2013.2278881.

- [38] M. Trajkovic, F. Blache, H. Debregeas, K. A. Williams and X. J. M. Leijtens, "Increasing the Speed of an InP-Based Integration Platform by Introducing High Speed Electroabsorption Modulators," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 25, no. 5, pp. 1–8, Sept.-Oct. 2019, Art no. 3400208, doi: 10.1109/JSTQE.2019.2913727.

- [39] Ding, Liang, Radhakrishnan L. Nagarajan, and Roberto Coccioli. "Compact optical transceiver by hybrid multichip integration." U.S.Patent 9,921,379, issued March 20, 2018.

- [40] Zhang, Jing, Grigorij Muliuk, Joan Juvert, Sulakshna Kumari, Jeroen Goyvaerts, Bahawal Haq, Camiel Op de Beeck et al. "III-V-on-Si photonic integrated circuits realized using microtransfer-printing." APL photonics 4, no. 11 (2019): 110803.

- [41] VPIPhotonics Software, "ModulatorEA\_Measured", Version 10.0, Berlin Germany, 2019 [Online]. Available: https://www.vpiphotonics.com/index.php.

- [42] T. Salgals, I. Kurbatska, S. Spolitis, V. Bobrovs, and G. Ivanovs, "Research of mpam and duobinary modulation formats for use in highspeed wdm-pon systems," in Telecommunication Systems-Principles and Applications of Wireless-Optical Technologies. IntechOpen, 2019.

- [43] A. Samani, E. El-Fiky, M. Morsy-Osman, R. Li, D. Patel, T. Hoang, M. Jacques, M. Chagnon, N. Abadía, and D. V. Plant, "Silicon photonic machzehnder modulator architectures for on chip pam-4 signal generation," *Journal of Lightwave Technology*, vol. 37, no. 13, pp. 2989–2999, 2019.

- [44] W.-J. Huang, C.-C. Wei, and J. Chen, "Optical dac for generation of pam-4 using parallel electro-absorption modulators," in ECOC 2016; 42nd

- European Conference on Optical Communication. VDE, 2016, pp. 1–3.

- [45] Tekronix. "Pam-4 signaling in high speed serial technology: Test, analysis, and debug," Tektronix, 2018.

- [46] Y. Matsui, T. Pham, T. Sudo, G. Carey, B. Young, J. Xu, C. Cole, and C. Roxlo, "28-gbaud pam-4 and 56-gb/s nrz performance comparison using 1310-nm al-bh dfb laser," Journal of Lightwave Technology, vol. 34, no. 11, pp. 2677–2683, 2016.

- [47] K. Nakahara, R. Hirai, T. Kitatani, N. Kikuchi, T. Fukui, K. Okamoto, Y. Sakuma, K. R. Tamura, and S. Tanaka, "Superior ber transmission of 106-gb/s/lane skewless pam-4 over 10 km by utilizing 1.3-µm directly modulated ingaalasmqw bh lasers and incoherent multiplexing of two nrz signals," in 2018 Optical Fiber Communications Conference and Exposition (OFC). IEEE, 2018, pp. 1–3.

- [48] C. Mobile, C. Telecom, C. Unicom, Huawei, FiberHome, AccelinK,

- [49] Hisense, S. E. ans Source Photonics, iNNOLIGHT, K. TECHNOLOGIES, SPIRENT, MACOM, and Inphi, "50G PAM-4 Technical White Paper," Huawei, Tech. Rep., 2010.

- [50] H. Li, G. Balamurugan, M. Sakib, J. Sun, J. Driscoll, R. Kumar, H. Jayatilleka, H. Rong, J. Jaussi, and B. Casper, "A 112 gb/s pam-4 transmitter with silicon photonics microring modulator and cmos driver," in 2019 Optical Fiber Communications Conference and Exhibition (OFC). IEEE, 2019, pp. 1–3.

- [51] Q. Guo, B. Hua, C. Ju, Z. Zhang, Y. Chen, Z. Tu, and X. Huang, "Experiment demonstration of im-dd based 50-gb/s pam-4 tdm-pon downstream scheme enabled by transmitter pre-emphasis and mlse," in 2018 23rd Opto-Electronics and Communications Conference (OECC). IEEE, 2018, pp. 1–2.

- [52] A. Roshan-Zamir, T. Iwai, Y.-H. Fan, A. Kumar, H.-W. Yang, L. Sledjeski, J. Hamilton, S. Chandramouli, A. Aude, and S. Palermo, "A 56-gb/s pam-4 receiver with low-overhead techniques for threshold and edge-based dfe fir-and iir-tap adaptation in 6y5-nm cmos," IEEE Journal of Solid-State Circuits, vol. 54, no. 3, pp. 672–684, 2018.

- [53] Pan, Yue, and Yanping Xi. "Monolithically integrated chirpmanaged laser (CML) based on a resonant tunneling optical spectrum reshaper filter." In 2016 Asia Communications and Photonics Conference (ACP), pp. 1–3. IEEE, 2016.

- [54] Zhu, Zenyuan, and Yanping Xi. "Optimized Design of Chirp Managed Lasers with Dispersion Precompensation by Integral Layer-Peeling Algorithm." In Asia Communications and Photonics Conference, pp. AF2A-54. Optical Society of America, 2016.

- [55] Karar, Abdullah S., John C. Cartledge, and Kim Roberts. "Transmission over 608 km of standard single-mode fiber using a 10.709-Gb/s chirp managed laser and electronic dispersion precompensation." IEEE Photonics Technology Letters 24, no. 9 (2012): 760–762.

#### Chapter 2

# MAS: Maximum Energy-Aware Sense Amplifier Link for Asynchronous Network on Chip

Erulappan Sakthivel and Rengaraj Madavan

#### **Abstract**

A real-time multiprocessor chip model is also called a Network-on-Chip (NoC), and deals a promising architecture for future systems-on-chips. Even though a lot of Double Tail Sense Amplifiers are used in architectural approach, the existing DTSA with transceiver exhibits a difficulty of consuming more energy than its gouged design during various traffic condition. Novel Low Power pulse Triggered Flip Flop with DTSA is designed in this research to eliminate the difficulty. The Traffic Aware Sense amplifier MAS consists of Sense amplifiers (SA's), Traffic Generator, and Estimator. Among various SA'S suitable (DTSA and NLPTF -DTSA) SA are selected and information transferred to the receiver. The performance of both DTSA with Transceiver and NLPTF-DTSA with transceiver compared under various traffic conditions. The proposed design (NLPTF-DTSA) is observed on TSMC 90 nm technology, showing 5.92 Gb/s data rate and 0.51 W total link power.

**Keywords:** network-on-chip (NoC), double tail sense amplifier (DTSA), low power pulse triggered flip flop (LPTF)

#### 1. Introduction

NoC may be a flourishing area for designing current application like Image processing, Signal Processing multimedia, Medical applications telecommunication, and real-time task [1]. Conservative investigation mainly focuses on low power, ultra-speed, and scalability in NoC [2]. Algorithmic [3] and architectural models [4] are made and instigated into the NoC to provide additional performance improvement than current NoC design. Existing NoC designer's shows much progress on this architectural level model by introducing outside or inside sense amplifier (SA) in on-chip communication [5]. In addition to the transmitter section (TXS) with pre-emphasis capacitance (PEC) for high speed and energy reduction in on-chip communication, it requires DC bias circuits at the receiver section (RXS). To overcome this issue, voltage sense amplifier is presented and tested in 90 nm Complementary metal-oxide-semiconductor (CMOS) cross coupled module [6]. In small circuit application user can't identify the worth of voltage SA so it is refined into Double Tail Sense Amplifiers (DTSA). This DTSA with transceiver consists of PEC at the transmitter and DTSA at RXS [7]. A low power consumption model is developed and implemented in many real-time applications. Clock Gating (CG) low power design approach at RTL TSMC 45 nm CMOS application is tested in [8].

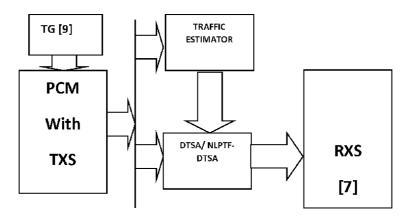

CMOS Very-large-scale integration (VLSI) design has taken us to real working chips that rely on controlled charge recovery to operate at suggestively lower power dissipation levels than their existing counterparts The Novel Low Power pulse Triggered Flip Flop with DTSA (NLPTF) is designed by using two N-type metaloxide-semiconductor (NMOS) transistor with an inverted clock signal as an input [9]. The output is taken from the transistor and given to the P-type metal-oxidesemiconductor (PMOS) transistor. The gate output of the PMOS transistor is given to the DTSA as an input and observes the output changes and power usage [10]. In [11] the performance improvement achieved in networks with respect to Network traffic modeling based on synthetic traffic The real-time traffic data are generated and estimated in on-chip communication, according to that TE new approach introduced for Quality of service (QoS) in [12]. This proposed design we followed above Traffic generator and TE in Traffic model and NLPTF-DTSA. The reconfigurable topology is applied in on-chip networks for performance improvement in [13]. To achieve performance improvement than [7], Maximum Energy-Aware sense amplifier (MAS) circuitry is introduced which consists of Traffic Generator (TG), Traffic Estimator (TE), capturing energy recovery [14] and NLPTF-DTSA. Clock gating (CG) Concept discussed in Sakthivel et al. [15].

The rest of this Chapter is ordered as follows. Subdivision 2 addresses the NoC system model. Proposed work and its module details are discussed in subdivision 3. The proposed results of various architectures are presented in subdivision 4. Finally, the conclusion is presented in subdivision 5.

#### 2. System model

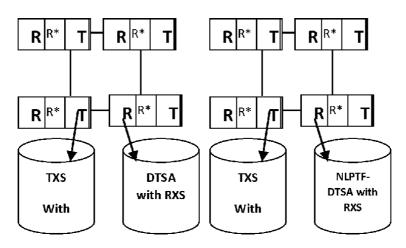

For improved data communication in NoC, conventional transceiver consists of PEC in TXS and DTSA circuit in TXS. Schinkel et al. Transceiver for NoC's and proposed Design is shown in **Figure 1**. The use of capacitance in TXS is to shrink in power dissipation. In NoC Circuitry communication disturbance occurs because of noise and crosstalk [16]. The transceiver with DIT (differential interconnect twist) affords a high-performance perfection. Early-stage, bidirectional interconnects are used. The EM field solver is used to investigate interconnects. The CMOS with 1.2 V, 6 m technology is used for interconnects as in [7]. **Table 1** shows Conventional Strategies.

**Figure 1.**Conventional and proposed Transceiver configuration.

| Circuitry | EXISTING | TAS design             |  |

|-----------|----------|------------------------|--|

| [7]       | DTSA     | TG [12], TE [12], DTSA |  |

| [18]      | NLPTF    | NLPTF-DTSA             |  |

**Table 1.**Conventional Strategies.

#### 3. Proposed work

**Figure 2** shows a basic diagram of proposed design, which consist of following modules organized such as PEC with TXS, TE, Controller, NLPTF-DTSA, and RXS. The proposed work consists of four stages namely selection, analysis, and design and performance comparison. In the first stage of our work is suitable SA'(DTSA and NLPTF-DTSA) is selected among various sense amplifier circuitry [18] and second stage selected SA's with the transceiver (DTSA and NLPTF-DTSA) high traffic (HT) and low traffic (LT) conditions examined. In the third stage, we compared NLPTF-DTSA for complete transceiver with [7].

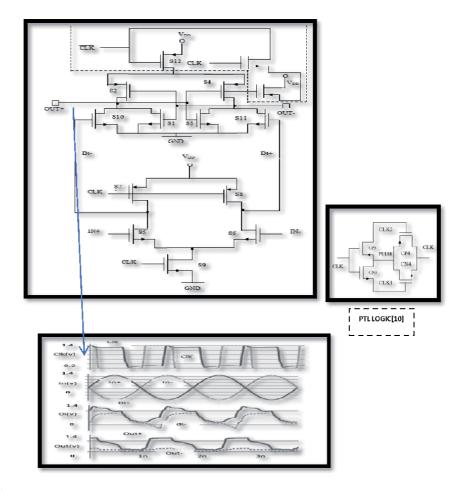

#### 3.1 NLPTF-DTSA circuit

The NLPTF-DTSA [18] is as shown in **Figure 3**. NLPTF -DTSA is used to solve the troubles associated with conventional Pulsed Flip Flop (P-FF) designs. The basic procedure of NLPTF -DTSA is plummeting the number of NMOS transistors in the discharging path. The next step NLPTF -DTSA is supporting a system to enhance the strength pull down by allocation value in to "1." The new transistor stacking circuitry is opposed to transistor S2 which is distant from the discharging path. Transistor S2, in conjunction through an extra transistor N3, forms a pass transistor logic (PTL) size of two AND gates of transistor S1. Since the inputs of the two AND logic gates are matching, the output node is reserved at zero time. When input signal 1 and input signal 2 are equal to "0", temporary floating at the node is basically risk-free. By the rising edge limits of the clock unit, both transistors S1 and S2 be turned resting on. This design is subsequently turned on transistor S3 by an instance width. The switching power is less at each node due to weakening voltage swing [10]. The functional diagram of NLPTF-DTSA and simulation results are shown in **Figure 3**.

**Figure 2.**Proposed Transceiver Block diagram.

Figure 3.

(a) The functional diagram of the V-DTSA module and (b) simulation result

#### 3.2 TXS with PEC

The technical concepts of TXS with PEC are similar to that of Schinkel et al.

#### 3.3 Low swing transmitter

The series capacitance in transmitter is used to drive the bus and reduces the swing factor. The technical parameters of the full swing (FS), multi VDD mode (MVM) capacitive low swing transmitter (CLS) are tabulated in the **Table 2**.

#### 3.4 Optimal swing receiver

In a transceiver circuit, SA is the best data receiver when compared to the conventional comparator [7]. To avoid transistor stack, the SA circuit is split into two tails and fed with separate supply voltage.

To gain maximum power reduction in NoC architecture, NLPTF [10] technique is implemented in DTSA module.

#### 3.5 TG and TE

The Statistical Traffic model [12] is implemented in this approach. By which various traffic condition (image, Data) applied into SA's with Transceiver.

| Modes | Inter connect            | Technology                    | Supply<br>voltage             | Voltage<br>swing | Driver size              |

|-------|--------------------------|-------------------------------|-------------------------------|------------------|--------------------------|

| FS    | Shielded single<br>ended | 1.2 v, 6 metal, 90 nm<br>CMOS | 1.2 V                         | 1.2 V            | Wn = 8 μm<br>Wp = 20 μm  |

| MVM   | DIT                      | 2 mm, Rwire = $400 \Omega$    | V <sub>DDH</sub> = 1. 2 V     | 120 mv           | Wn = 8 μm<br>Wp = 20 μm  |

|       |                          |                               | V <sub>DDL</sub> =<br>1. 08 V |                  | -                        |

| CLS   | DIT                      | _                             | 1.2 V                         | 120 mv           | Wn = 1.6 μm<br>Wp = 4 μm |

**Table 2.**Different modes comparison.

Figure 4.

The functional diagram of the Complete Transceiver Circuit.

**Figure 5.**Complete Transceiver simulation result.

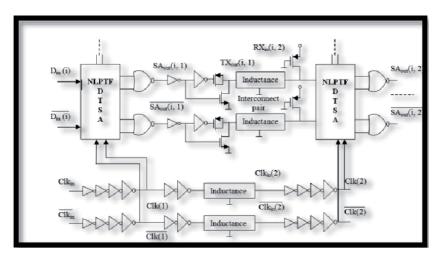

#### 3.6 Complete transceiver

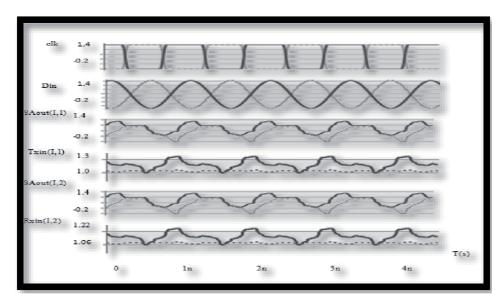

The complete transceiver circuit is made of transmitter connected to the receiver via DIT [7]. The complete transceiver architecture is shown in the **Figure 4**. And the experimental results of complete transceiver in **Figure 5**.

#### 4. Results and discussions

The performance parameters of the DTSA and NLPTF-DTSA with transceiver are examined using 90 nm technologies. Synopsys Design Compiler is used for Gate level net list creation. Synopsys™ Prime Power is used for Power analysis [17]. The switching factors are reported by the proposed work and examined in Intel® 3.1 GHz LGA 1155 Core i3–2100 Processor, and a system with Window Xp. The technical level similar to [7] carried out various modes such as FS, MVM, and CLS.

The NoC model synthesized code is made to evaluate 90 nm TSMC CMOS technology under the operating frequency of 500 MHZ, 1.2 V supply voltages and 0.5 switching factor. The Sleep mode and Active mode power consumption are tested.

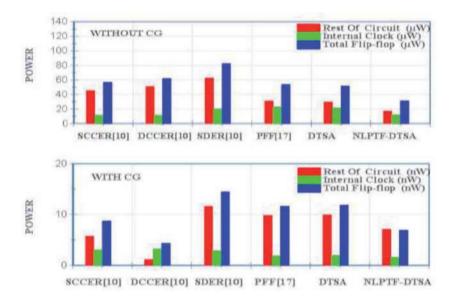

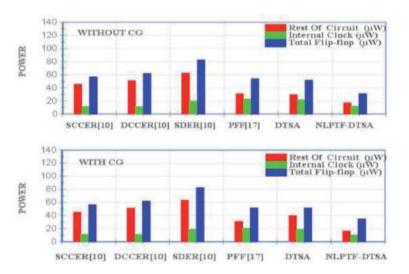

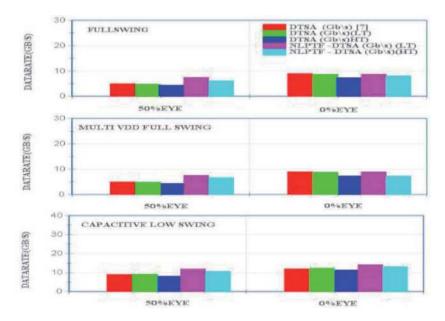

\* With CG and without CG The results are presented in **Figures 6** and 7. It is inferred that the proposed NLPTF-DTSA gives a greater result in terms of power as related with DTSA modules such as single-ended conditional capturing energy recovery (SCCER) [10], DCCER [10], static differential energy recovery (SDER) [10], pulsed flip flop (PFF) [18], NLPTF-DTSA. A mathematical expression for technical evaluation is similar to [19].

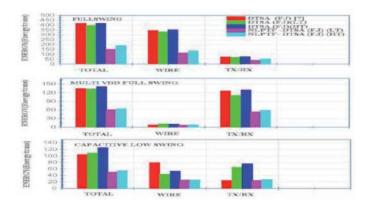

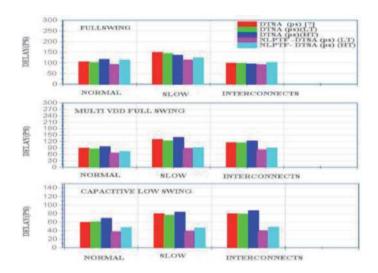

The energy consumption, delay, data Rate and static power consumption results are presented in **Figures 8–11**. The DTSA, NLPTF-DTSA circuitry results are estimated under HT and LT. The overall comparison of various parameters (Energy consumption, delay, data Rate and static power consumption) with current work is shown in **Table 3**. The overall results of proposed design give greater results than conservative design.

**Figure 6.**Power comparison in Sleep mode.

**Figure 7.**Power comparison in Active mode.

**Figure 8.** *Energy comparison of DTSA modules.*

**Figure 9.**Delay comparison of DTSA modules.

**Figure 10.**Data Rate comparison of DTSA modules.

Figure 11.

Static Power comparison of DTSA modules.

| Work             | Module<br>name | Traffic<br>mode | Data rate GB/S<br>(data rate<br>improvement %) | Link<br>power (W) | Latency (10 mm of<br>interconnect) single/<br>five stage operation |

|------------------|----------------|-----------------|------------------------------------------------|-------------------|--------------------------------------------------------------------|

| [7]              | DTSA           | _               | 5.0 (80%)                                      | 0.8               | 300/1500                                                           |

| Proposed<br>work | DTSA           | LT              | 4.9 (78.4%)                                    | 0.98              | 345/1725                                                           |

| Proposed<br>work | DTSA           | НТ              | 4.0 (64%)                                      | 1.32              | 487/2435                                                           |

| Proposed<br>work | NLPTF-<br>DTSA | Average         | 5.92 (94.72%)                                  | 0.51              | 497/2485                                                           |

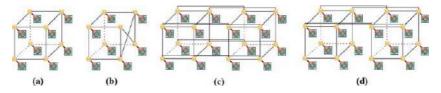

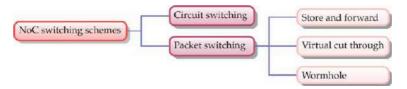

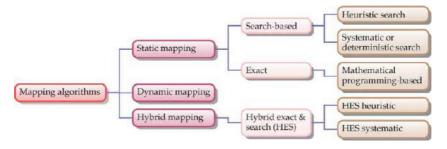

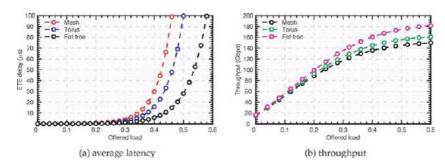

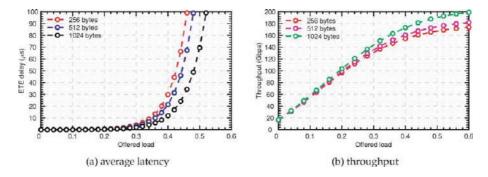

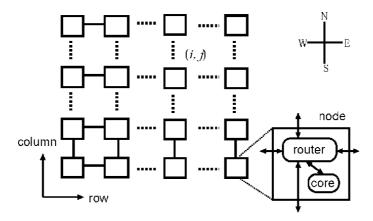

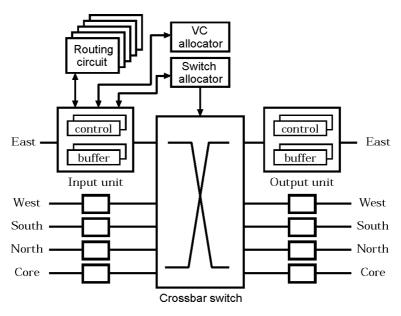

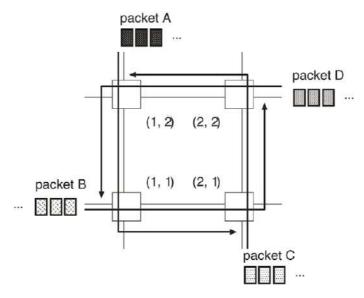

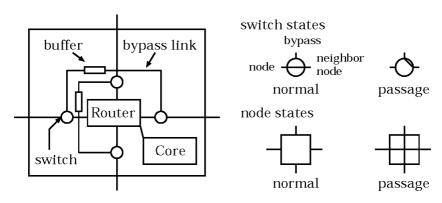

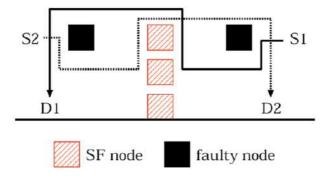

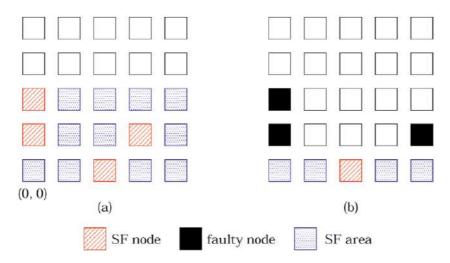

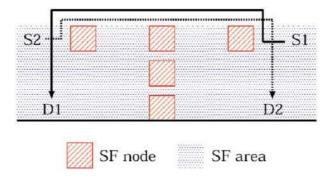

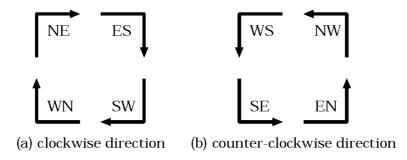

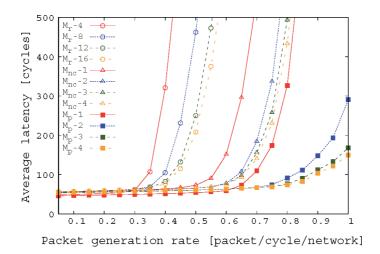

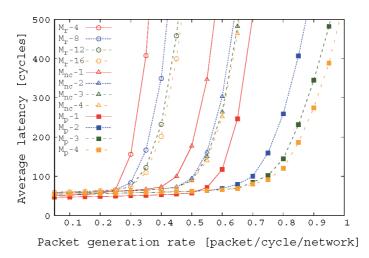

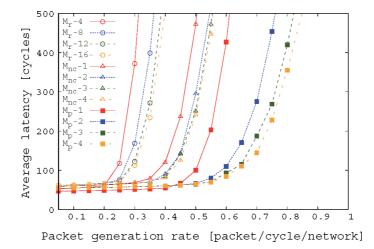

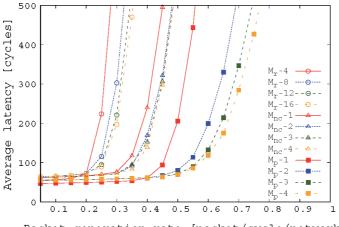

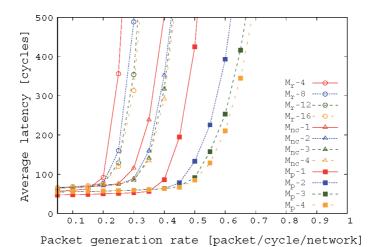

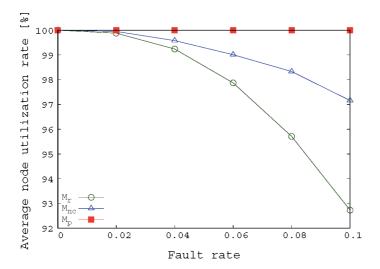

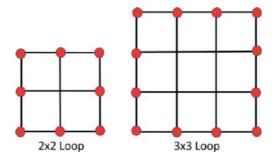

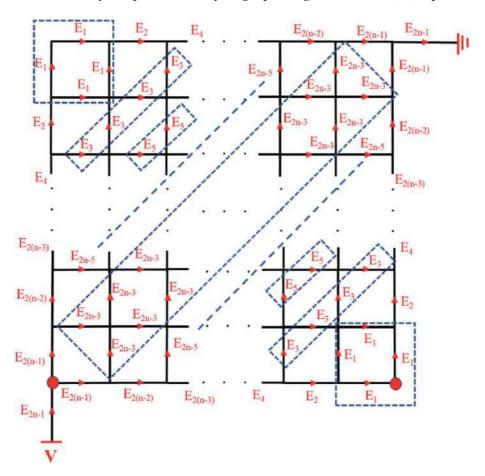

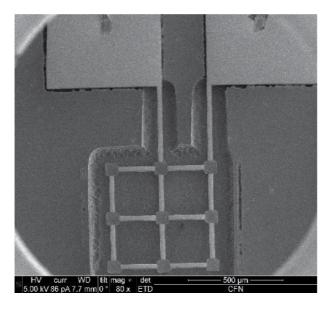

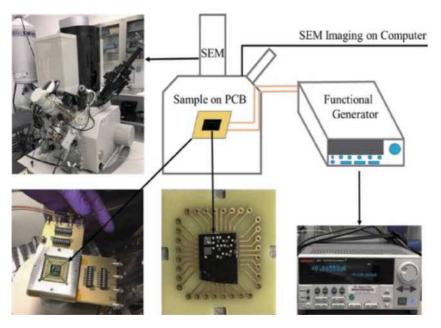

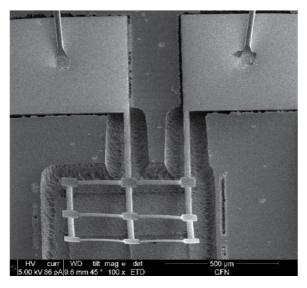

**Table 3.** *The overall transceiver performance comparison.*