# Advanced DC-DC Power Converters and Switching Converters

Edited by Salvatore Musumeci Printed Edition of the Special Issue Published in *Energies*

www.mdpi.com/journal/energies

## Advanced DC-DC Power Converters and Switching Converters

## Advanced DC-DC Power Converters and Switching Converters

Editor

Salvatore Musumeci

$\texttt{MDPI} \bullet \texttt{Basel} \bullet \texttt{Beijing} \bullet \texttt{Wuhan} \bullet \texttt{Barcelona} \bullet \texttt{Belgrade} \bullet \texttt{Manchester} \bullet \texttt{Tokyo} \bullet \texttt{Cluj} \bullet \texttt{Tianjin}$

*Editor* Salvatore Musumeci Politecnico di Torino Italy

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Energies* (ISSN 1996-1073) (available at: https://www.mdpi.com/journal/energies/special\_issues/DC-DC\_Converter\_Switching\_Converters).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-0446-9 (Hbk) ISBN 978-3-0365-0447-6 (PDF)

© 2021 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Editor                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Advanced DC-DC Power Converters and Switching Converters"                                                                                                                                                                                                                                                                                             |

| Shin-Ju Chen, Sung-Pei Yang, Chao-Ming Huang and Yu-Hua Chen         Interleaved High Step-Up DC-DC Converter with Voltage-Lift and Voltage-Stack Techniques         for Photovoltaic Systems †         Reprinted from: Energies 2020, 13, 2537, doi:10.3390/en13102537                                                                                           |

| Binxin Zhu, Hui Hu, Hui Wang and Yang Li         A Multi-Input-Port Bidirectional DC/DC Converter for DC Microgrid Energy Storage         System Applications         Reprinted from: Energies 2020, 13, 2810, doi:0.3390/en13112810                                                                                                                              |

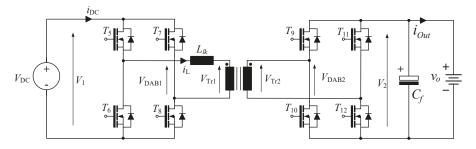

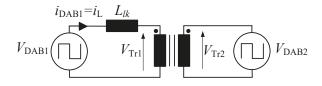

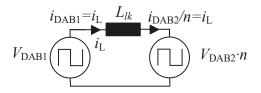

| Nuraina Syahira Mohd Sharifuddin, Nadia M. L. Tan and Hirofumi AkagiEvaluation of a Three-Phase Bidirectional Isolated DC-DC Converter with Varying TransformerConfigurations Using Phase-Shift Modulation and Burst-Mode SwitchingReprinted from: Energies 2020, 13, 2836, doi:10.3390/en13112836Reprinted from: Energies 2020, 13, 2836, doi:10.3390/en13112836 |

| Michal Frivaldsky, Slavomir Kascak, Jan Morgos and Michal Prazenica<br>From Non-Modular to Modular Concept of Bidirectional Buck/Boost Converter for<br>Microgrid Applications<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 3287, doi:10.3390/en13123287                                                                                          |

| Jelena Loncarski, Vito Giuseppe Monopoli, Giuseppe Leonardo Cascella andFrancesco CupertinoSiC-MOSFET and Si-IGBT-Based dc-dc Interleaved Converters for EV Chargers: Approach forEfficiency Comparison with Minimum Switching Losses Based on Complete Parasitic ModelingReprinted from: Energies 2020, 13, 4585, doi:0.3390/en1317458579                        |

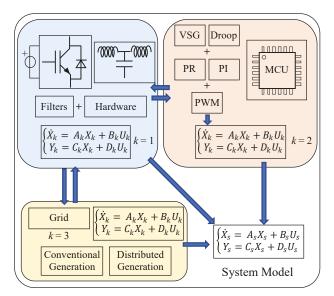

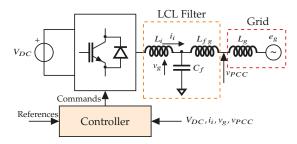

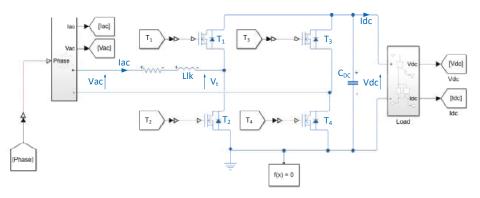

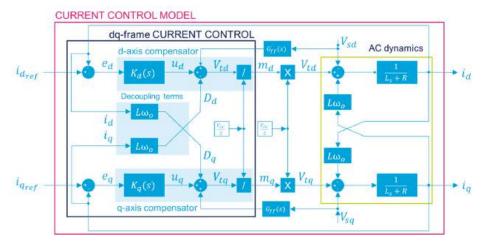

| Fabio Mandrile, Salvatore Musumeci, Enrico Carpaneto, Radu Bojoi, Tomislav Dragičevićand Frede BlaabjergState-Space Modeling Techniques of Emerging Grid-Connected ConvertersReprinted from: Energies 2020, 13, 4824, doi:10.3390/en13184824ConvertersReprinted from: Energies 2020, 13, 4824, doi:10.3390/en13184824                                             |

| Fabio Corti, Antonino Laudani, Gabriele Maria Lozito and Alberto ReattiComputationally Efficient Modeling of DC-DC Converters for PV ApplicationsReprinted from: Energies 2020, 13, 5100, doi:10.3390/en13195100Reprinted from: Energies 2020, 13, 5100, doi:10.3390/en13195100                                                                                   |

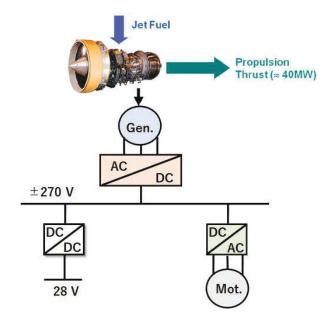

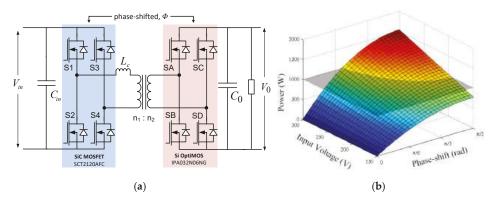

| Antonio Lamantia, Francesco Giuliani and Alberto Castellazzi<br>Power Scalable Bi-Directional DC-DC Conversion Solutions for Future Aircraft Applications<br>Reprinted from: <i>Energies</i> 2020, 13, 5470, doi:10.3390/en13205470                                                                                                                               |

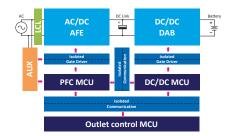

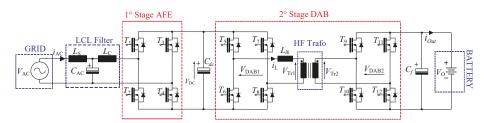

| Giuseppe Aiello, Mario Cacciato, Francesco Gennaro, Santi Agatino Rizzo,<br>Giuseppe Scarcella and Giacomo Scelba<br>A Tool for Evaluating the Performance of SiC-Based Bidirectional Battery Chargers for<br>Automotive Applications<br>Reprinted from: <i>Energies</i> 2020, <i>13</i> , 6733, doi:10.3390/en13246733                                           |

|                                                                                                                                                                                                                                                                                                                                                                   |

### About the Editor

**Salvatore Musumeci**, Ph.D., was born in Giarre, Italy. He received his M.S. in Electrical Engineering and Ph.D. in Electrical Engineering from the University of Catania, Catania, Italy, in 1991 and 1995, respectively. From 1996 to 2001 he worked in the R&D Department of STMicroelectronics (Catania, Italy). From 2001 to 2017, he was involved in several research collaborations with the Department of Electrical Electronic and Systems Engineering, University of Catania (Italy). Since 2018, he has been Assistant Professor of Power Electronics, Electrical Machines, and Drives at the Energy Department of Politecnico di Torino (Italy). He is involved in the Power Electronics Innovation Center (PEIC), a new competence center of Politecnico di Torino (PoliTO) focused on power electronics. His research interests are advanced power devices, switching power converter applications, high-efficiency industrial motors, magnetic materials and their applications, battery management systems, and automotive power electronics applications.

## Preface to "Advanced DC-DC Power Converters and Switching Converters"

Nowadays, power electronics is an enabling technology in the energy development scenario. Furthermore, power electronics is strictly linked with several fields of technological growth, such as consumer electronics, IT and communications, electrical networks, utilities, industrial drives and robotics, and transportation and automotive sectors. Moreover, the widespread use of power electronics enables cost savings and minimization of losses in several technology applications required for sustainable economic growth. The topologies of DC-DC power converters and switching converters are under continuous development and deserve special attention to highlight the advantages and disadvantages for use increasingly oriented towards green and sustainable development. DC-DC converter topologies are developed in consideration of higher efficiency, reliable control switching strategies, and fault-tolerant configurations. Several types of switching converter topologies are involved in isolated DC-DC converter and nonisolated DC-DC converter solutions operating in hard-switching and soft-switching conditions. Switching converters have applications in a broad range of areas in both low and high power densities. The articles presented in the Special Issue titled "Advanced DC-DC Power Converters and Switching Converters" consolidate the work on the investigation of the switching converter topology considering the technological advances offered by innovative wide-bandgap devices and performance optimization methods in control strategies used and also in the design of the passive components such as high-frequency isolation transformers. The articles concern switching converter topics such as the following:

- New switching converter topologies for power electronics applications;

- Control and optimization of switching converter circuits;

- Innovative power devices in switching converter applications;

- Advanced DC–DC converters for power supply applications;

- Switching converters in smart grid applications and energy transmission systems;

- Advanced switching converters for renewable energy conversion;

- Advanced DC–DC converters for energy storage systems;

- Switching converters in automotive and traction systems.

From an overview of the articles presented, the issues of the role of converters in the generation of renewable energy and optimization in smart electricity grids together with the problems of recharging batteries for both energy storage systems and electric traction are predominant. As can be seen from the contributions offered, the key role of new semiconductor devices and advanced converter topologies allows a significant contribution to improving energy efficiency. Due to global problems such as the greenhouse effect, energy shortages, and sustainable mobility, a considerable effort is required towards the use of renewable energy and electrical transmission, storage, and implementation systems in the development of livable urban agglomerations and global life quality. Energy conversion via switching converters plays a crucial role in the development of these necessary technological needs. The studies and results presented, while not exhaustive, move in the direction of a further step towards continuous improvement to which we are all called in our research work. Each small research contribution acts in the growth of the quality of life for the well-being of present and especially future generations.

Salvatore Musumeci

#### Article

## Interleaved High Step-Up DC–DC Converter with Voltage-Lift and Voltage-Stack Techniques for Photovoltaic Systems <sup>†</sup>

#### Shin-Ju Chen<sup>1</sup>, Sung-Pei Yang<sup>1,2,\*</sup>, Chao-Ming Huang<sup>1</sup> and Yu-Hua Chen<sup>1</sup>

- <sup>1</sup> Department of Electrical Engineering, Kun Shan University, Tainan 710303, Taiwan; sjchen@mail.ksu.edu.tw (S.-J.C.); h7440@ms21.hinet.net (C.-M.H.); e124667833@gmail.com (Y.-H.C.)

- <sup>2</sup> Green Energy Technology Research Center, Kun Shan University, Tainan 710303, Taiwan

- \* Correspondence: spyang@mail.ksu.edu.tw; Tel.: +886-6-205-1906; Fax: +886-6-205-0298

- + This present work is an extension of our paper "High step-up interleaved converter with three-winding coupled inductors and voltage multiplier cells" presented to IEEE ICIT 2019 conference, 13–15 February 2019, Melbourne, Australia.

Received: 13 April 2020; Accepted: 14 May 2020; Published: 16 May 2020

**Abstract:** A novel interleaved high step-up DC–DC converter applied for applications in photovoltaic systems is proposed in this paper. The proposed configuration is composed of three-winding coupled inductors, voltage multiplier cells and a clamp circuit. The step-up voltage gain is effectively increased, owing to the voltage-stack and voltage-lift techniques using the voltage multiplier cells. The leakage inductor energy is recycled by the clamp circuit to avoid the voltage surge on a power switch. The low-voltage-rated power switches with low on-state resistances and costs can be used to decrease the conduction losses and increase the conversion efficiency when the voltage. The reverse-recovery problems of diodes are mitigated by the leakage inductances of the coupled inductors. Moreover, both the input current ripple and the current stress on each power switch are reduced, owing to the interleaved operation. The operating principle and steady-state analysis of the proposed converter are thoroughly presented herein. A controller network is designed to diminish the effect of the variations of input voltage and output load on the output voltage. Finally, the experimental results for a 1 kW prototype with 28–380 V voltage conversion are shown to demonstrate its effectiveness and performance.

Keywords: interleaved operation; three-winding coupled inductor; high step-up DC-DC converter

#### 1. Introduction

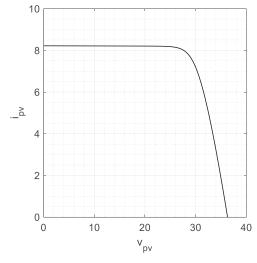

Because of the fast exhaustion of fossil fuels and the global warming problem, much research has been developed to cope with green energy sources, such as the fuel cells, photovoltaic power (PV power) or wind power. Generally, a single-phase 220 Vac grid-connected photovoltaic system requires a DC bus voltage of 380–420 V to provide the requirement for a full-bridge DC–AC inverter. Regrettably, the output voltages of individual PV modules are ordinarily lower than 40 V in household applications [1]. Thus, a high step-up DC–DC converter is necessary to serve as a voltage boosting cell between the PV modules and the AC power generation unit [2–4].

For a traditional boost converter, an extreme duty ratio operation has to be realized to obtain a high voltage gain. However, it will result in large current ripples, high conduction losses, reverse-recovery problems for diodes, and electromagnetic interference problems [5]. In addition, the voltage stresses on the power switches and diodes are equal to the high output voltage. Thus, high-voltage-rated MOSFETs with high on-state resistance and diodes with high forward voltage drop should be used,

which leads to lower efficiency due to high conduction losses. To proceed, isolated power converters, such as a conventional flyback DC–DC converter, can derive a high voltage gain by adopting a high transformer turns ratio, which results in a large leakage inductance. A large leakage inductance will cause a much higher voltage spike on the power switch and more power dissipations. Consequently, the aforementioned converters are not proper for use in a high step-up voltage gain application.

To overcome the above problems in high voltage gain applications, many high step-up converters have been presented in the literature. Coupled inductors have been adopted to obtain a high voltage gain in the non-isolated converters, because the turns ratio can be served as a control freedom to enlarge the voltage gain [6–10]. Recently, a three-winding coupled inductor has also been applied to a lot of high step-up DC–DC converters to achieve higher voltage gains [11–13]. In [14–19], the switched-inductor and/or switched-capacitor step-up converters are presented to derive a high voltage gain, owing to their simpler structure and operation. A double-duty technique was applied in the high step-up voltage gain applications with two distinct duty ratios for the power switches in [20,21]. The parallel structure on the input side with interleaved operation can be utilized to increase the power level and reduce the input current ripple. The voltage multiplier cells were also applied to the interleaved high step-up converters in [22–24]. The built-in transformer technique for obtaining a high step-up conversion ratio is presented in [25–27]. The interleaved DC–DC converters with three-winding coupled inductors in [28–30] exhibited a high voltage gain and better current sharing performance simultaneously.

An IA novel interleaved high step-up DC–DC converter is proposed in this paper. It contains three-winding coupled inductors, voltage multiplier cells and a clamp circuit. The voltage-stack and voltage-lift techniques are adopted to extend the voltage gain by means of the voltage multiplier cells. The clamp circuit is utilized to recycle the leakage inductor energy and clamp the voltage stress of power switches. The advantages of the proposed high step-up converter are as follows:

- By designing a proper turns ratio for the coupled inductors, the high voltage conversion ratio can be obtained whilst operating at an appropriate duty ratio.

- (2) The voltage stresses on the power switches are greatly less than the output voltage, so the power switches with lower on-state resistances are utilized to decrease the conduction losses.

- (3) The power switches achieve zero-current switching at turn on, and the switching losses can thereby be reduced.

- (4) The diode reverse-recovery problem is effectively alleviated by the leakage inductances of the coupled inductors.

- (5) The leakage inductor energy can be recycled to suppress the voltage spikes on the power switches.

A prototype of 1 kW was implemented in the laboratory to verify the theoretical analysis and the performance of the proposed interleaved high step-up converter. The remainder of this paper is organized as follows. In Section 2, the circuit description is given, and the operating principle is presented in detail simultaneously. Section 3 shows the steady-state analysis. The performance comparison with existing converters is also presented. The closed-loop controller design is provided in Section 4. Section 5 provides the experimental results of a laboratory prototype. Finally, the conclusion of this paper is given in Section 6.

#### 2. Circuit Description and Operating Principle

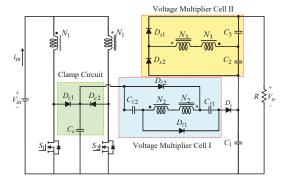

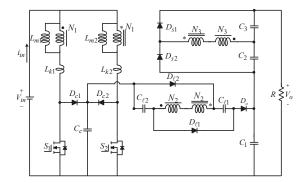

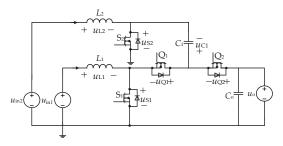

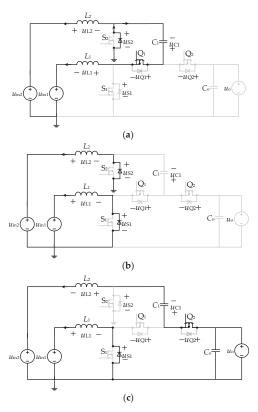

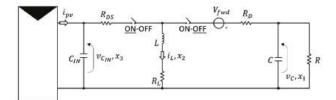

Figure 1 shows the circuit topology of the proposed converter. Two three-winding coupled inductors with the same number of turns are included in the proposed converter. The primary, secondary and tertiary windings are denoted by  $N_1$ ,  $N_2$  and  $N_3$ , respectively. The coupling reference is indicated by and \*. The primary windings are parallel connected to process the large input current and serve as the filter inductors in the conventional boost converter. The secondary windings are connected in series to constitute the voltage multiplier cell I, which is inserted between the clamp circuit and the output high voltage side to lift the output voltage. The tertiary windings are in series

connection to constitute the voltage multiplier cell II, which is stacked on the output capacitor  $C_1$  to enlarge the voltage conversion ratio.

Figure 1. Circuit configuration of the proposed converter.

The coupled inductor is modeled as an ideal transformer with a defined turns ratio, which is in parallel with a magnetizing inductor and in series with a leakage inductor. $L_{m1}$  and  $L_{m2}$  represent the magnetizing inductances, while  $L_{k1}$  and  $L_{k2}$  represent the leakage inductances. Assuming that the number of turns  $N_3$  is equal to  $N_2$ . n is defined as the turns ratio with  $n = N_2/N_1 = N_3/N_1$ . The equivalent circuit of the proposed converter is illustrated in Figure 2, where  $S_1$  and  $S_2$  are the power switches;  $D_{c1}$  and  $D_{c2}$  are the clamp diodes;  $C_c$  is the clamp capacitor;  $D_{\ell 1}$  and  $D_{\ell 2}$  are the lift diodes;  $C_{\ell 1}$  and  $C_{\ell 2}$  are the lift capacitors;  $D_{s1}$  and  $D_{s2}$  are the switched diodes;  $C_1$ ,  $C_2$  and  $C_3$  are the output capacitors;  $D_o$  is the output diode;  $V_{in}$  is the input voltage;  $V_o$  is the output voltage; and R is the output load.

Figure 2. Equivalent circuit of the proposed converter.

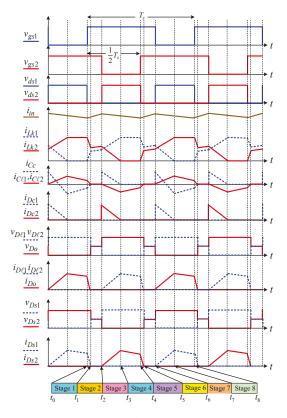

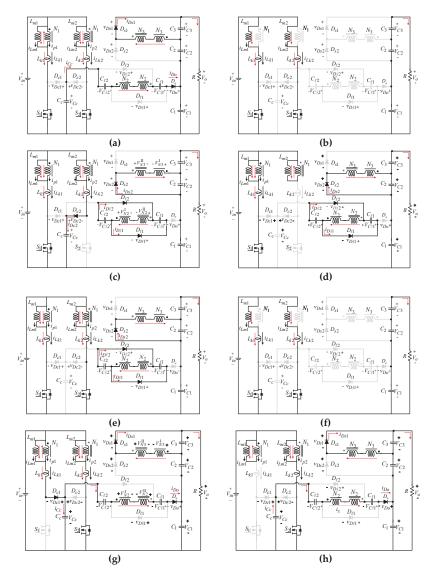

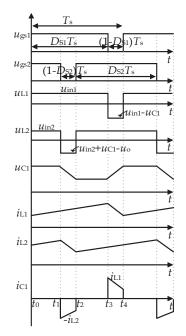

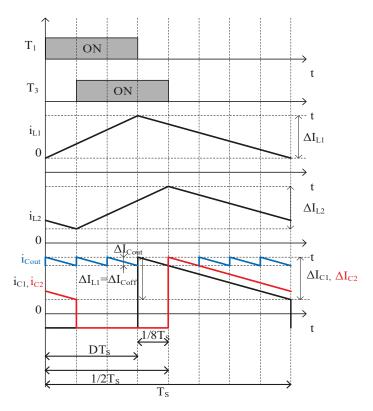

The proposed converter operates in continuous conduction mode (CCM). The gate signals of the power switches are interleaved with 180 phase shift, the duty ratios are the same, and they are greater than 0.5. The theoretical waveforms are shown in Figure 3. In CCM operation, the operating mode of the proposed converter can be partitioned into eight stages over one switching period. Figure 4 shows the corresponding circuit models for the eight operating stages.

Figure 3. Theoretical waveforms of the proposed converter.

**Stage 1** [ $t_0 \sim t_1$ ]: The equivalent circuit of this stage is depicted in Figure 4a. At  $t = t_0$ , the power switch  $S_1$  starts to turn on with zero-current switching (ZCS) operation, owing to the leakage inductance  $L_{k1}$ , and  $S_2$  is still in a turn-on state. The diodes  $D_{c1}$ ,  $D_{c2}$ ,  $D_{\ell 1}$ ,  $D_{\ell 2}$  and  $D_{s2}$  are reversed biased, and  $D_o$  as well as  $D_{s1}$  are still turned on. The current through  $L_{k1}$  increases rapidly from zero, while the currents through the secondary and tertiary windings of the coupled inductors decrease. The current falling rates through  $D_o$  and  $D_{s1}$  are controlled by the leakage inductances  $L_{k1}$  and  $L_{k2}$ , such that the diode reverse recovery problem is alleviated. The stored energy in the magnetizing inductor  $L_{m1}$  is transferred to the output side via the secondary and tertiary windings of the coupled inductors. The following equations are valid:

$$i_{p2} = -i_{p1} = n(i_{Do} + i_{Ds1}) \tag{1}$$

$$i_{Lk1} = i_{Lm1} + i_{p1} = i_{Lm1} - n(i_{Do} + i_{Ds1})$$

<sup>(2)</sup>

As the leakage inductor current  $i_{Lk1}$  reaches the magnetizing inductor current  $i_{Lm1}$ , this stage ends. At the same time, the currents through the diodes  $D_o$  and  $D_{s1}$  fall to zero, and  $D_o$  and  $D_{s1}$  are turned off with ZCS operation.

**Stage 2** [ $t_1 \sim t_2$ ]: The power switches  $S_1$  and  $S_2$  remain in a turn-on state, and all of the diodes are in a turn-off state. Figure 4b depicts the corresponding operating circuit. The currents through

inductors  $L_{m1}$ ,  $L_{k1}$ ,  $L_{m2}$  and  $L_{k2}$  increase linearly because these inductors are charged from the input DC source. The leakage inductor currents are as follows.

$$i_{Lk1}(t) = i_{Lk1}(t_1) + \frac{V_{in}}{L_{m1} + L_{k1}}(t - t_1)$$

(3)

$$i_{Lk2}(t) = i_{Lk2}(t_1) + \frac{V_{in}}{L_{m2} + L_{k2}}(t - t_1)$$

(4)

This stage ends when  $S_2$  is turned off.

**Stage 3** [ $t_2 \sim t_3$ ]: In this stage, the switch  $S_2$  is in a turn-off state, and  $S_1$  keeps conducting. The operating circuit is illustrated in Figure 4c. The clamp capacitor  $C_c$  is charged by the current  $i_{Lk2}$  via the clamp diode  $D_{c2}$ . The leakage inductor energy is released to the capacitor  $C_c$ . The current  $i_{Lk2}$  decreases linearly. The voltage across the switch  $S_2$  is clamped by the capacitor voltage  $V_{Cc}$ . The energy stored in  $L_{m2}$  is released to the capacitors  $C_{\ell 1}$ ,  $C_{\ell 2}$  and  $C_2$  via the secondary and tertiary windings of the coupled inductors. The lift capacitors  $C_{\ell 1}$  and  $C_{\ell 2}$  are charged by the lift diode currents  $i_{D\ell 1}$  and  $i_{D\ell 2}$ , respectively. At the same time, the output capacitor  $C_2$  is charged by the current  $i_{Ds2}$ . The following equations are valid:

$$i_{p1} = -i_{p2} = ni_{Ds2} + n(i_{D\ell 1} + i_{D\ell 2})$$

(5)

$$i_{Lk2} = i_{Lm2} - ni_{Ds2} - n(i_{D\ell 1} + i_{D\ell 2})$$

(6)

The stage finishes as  $i_{Lk2}$  falls to zero at  $t = t_3$ , and the clamp diode  $D_{c2}$  becomes reverse-biased under ZCS operation. Thus, there is no reverse recovery loss for  $D_{c2}$ .

**Stage 4** [ $t_3 \sim t_4$ ]: At the beginning time, the clamp diode  $D_{c2}$  is naturally turned off when the leakage inductor energy stored in  $L_{k2}$  has fully released to the clamp capacitor  $C_c$ . The operating circuit is illustrated in Figure 4d. Magnetizing inductor  $L_{m2}$  still transfers its energy to charge  $C_{\ell1}$ ,  $C_{\ell2}$  and  $C_2$  via the secondary and tertiary windings of the coupled inductors. The current through the power switch  $S_1$  is the summation of the currents in the magnetizing inductors  $L_{m1}$  and  $L_{m2}$ . The following equations are held in this stage:

$$i_{Lm2} = n(i_{D\ell 1} + i_{D\ell 2}) + ni_{Ds2} \tag{7}$$

$$i_{S1} = i_{Lm1} + i_{Lm2} \tag{8}$$

This stage finishes when the turn-on signal is applied to  $S_2$ .

**Stage 5** [ $t_4 \sim t_5$ ]: In this stage, the operating circuit is depicted in Figure 4e. The switch  $S_2$  turns on at time  $t_4$  under ZCS condition, owing to the leakage inductance  $L_{k2}$ , and  $S_1$  is still conducting. The current  $i_{Lk2}$  increases rapidly from zero, and the currents in the secondary and tertiary windings of the coupled inductors decrease. The current falling rates through  $D_{\ell 1}$ ,  $D_{\ell 2}$  and  $D_{s2}$  are dominated by  $L_{k1}$  and  $L_{k2}$ , such that the diode reverse recovery problem is mitigated. As the leakage inductor current  $i_{Lk2}$  reaches  $i_{Lm2}$ , this stage ends at  $t = t_5$ . At the same time, the currents through  $D_{\ell 1}$ ,  $D_{\ell 2}$  and  $D_{s2}$  fall to zero, and these diodes are naturally turned off with ZCS operation.

**Stage 6** [ $t_5 \sim t_6$ ]: The switches  $S_1$  and  $S_2$  are conducting in this interval. All of the diodes are in a turn-off state. The operating circuit is depicted in Figure 4f. The operating modes of stages 1 and 6 are similar. At the end of this stage the switch  $S_1$  is turned off.

**Stage 7** [ $t_6 \sim t_7$ ]: The switch  $S_1$  is turned off at time  $t_6$ . The operating circuit is illustrated in Figure 4g. One part of the leakage inductor energy stored in  $L_{k1}$  is released to the clamped capacitor  $C_c$ , and another part of the leakage inductor energy is recycled to the output side. The leakage inductor current  $i_{Lk1}$  is falling. The input voltage  $V_{in}$ ,  $C_{\ell 2}$  and  $C_{\ell 1}$  are in series connection to transfer energy to the output capacitor  $C_1$  via diodes  $D_{c1}$  and  $D_o$ , as well as the primary and secondary windings of the coupled inductors, thus extending the voltage on the output capacitor  $C_1$ . The stored energy in  $L_{m1}$  is delivered to the secondary and tertiary windings of the coupled inductors, such that output capacitor  $C_3$  is charged by the diode current  $i_{Ds1}$ , and  $C_1$  is charged by the diode current  $i_{Do}$ . As the leakage

inductor current  $i_{Lk1}$  drops to zero, the diode  $D_{c1}$  becomes reverse-biased and turns off at time  $t_7$  under ZCS condition. Thus, there is no reverse recovery loss for  $D_{c1}$ . At this moment, this stage ends.

**Stage 8** [ $t_7 \sim t_8$ ]: Figure 4h illustrates the operating circuit. At the beginning time, the leakage inductor energy stored in  $L_{k1}$  has completely released. Magnetizing inductor  $L_{m1}$  still transfers energy to the capacitors  $C_1$  and  $C_3$  via the secondary and tertiary windings of the coupled inductors. The capacitors  $C_c$ ,  $C_{\ell 1}$ ,  $C_{\ell 2}$  and the secondary windings are connected in series to transfer their energy to the output capacitor  $C_1$ . The current in the switch  $S_2$  is the summation of the currents  $i_{Lm1}$  and  $i_{Lm2}$ . The switch  $S_1$  is turned on at the end of this stage. Then, a new switching period begins to start.

Figure 4. Operating stages of the proposed converter. (a) Stage 1, (b) Stage 2, (c) Stage 3, (d) Stage 4, (e) Stage 5, (f) Stage 6, (g) Stage 7, (h) Stage 8.

#### 3. Steady-State Analysis

#### 3.1. Voltage Gain Derivation

To briefly describe the voltage gain derivation, the following assumptions are used:

- All of the semiconductors are regarded as ideal. The on-state resistance of the switches and the forward voltage drop of the diodes are ignored.

- (2) The leakage inductances are neglected.

- (3) The magnetizing inductances of the coupled inductors are regarded as the same; that is,  $L_{m1} = L_{m2} = L_m$ .

All of the capacitors are large enough. As a result, the voltages across them are considered constant during one switching period. Based on the volt-second balance principle of the magnetizing inductance  $L_{m1}$ , the voltage on the clamp capacitor  $C_c$  can be derived as

$$V_{Cc} = \frac{1}{1 - D} V_{in} \tag{9}$$

where D is the operating duty ratio. The result in Equation (9) is identical to the output voltage of a conventional boost converter.

Let the voltages across the secondary and tertiary windings of the coupled inductors be denoted by  $V_{N2}^{I}$  and  $V_{N3'}^{I}$ ,  $V_{N2}^{II}$  and  $V_{N3}^{II}$ , respectively. According to Kirchhoff's Voltage Low (KVL), the voltages across the lift capacitors  $C_{\ell 1}$  and  $C_{\ell 2}$  can be calculated from stage 3 as

$$V_{C\ell 1} = V_{C\ell 2} = V_{N2}^{\rm I} - V_{N2}^{\rm II} = nV_{in} - n(V_{in} - V_{Cc}) = nV_{Cc}$$

(10)

Moreover, it also yields

$$V_{C2} = V_{N3}^{\rm I} - V_{N3}^{\rm II} = nV_{in} - n(V_{in} - V_{Cc}) = nV_{Cc}$$

(11)

Substituting Equation (9) into Equations (10) and (11), the capacitor voltages are rewritten as

$$V_{C\ell 1} = V_{C\ell 2} = \frac{n}{1 - D} V_{in}$$

(12)

$$V_{C2} = \frac{n}{1 - D} V_{in} \tag{13}$$

By applying KVL in stage 7, the voltage  $V_{C3}$  across the output capacitor  $C_3$  can be derived as

$$V_{C3} = V_{N3}^{II} - V_{N3}^{I} = nV_{Cc} = \frac{n}{1 - D}V_{in}$$

(14)

Moreover, the voltage across the output capacitor  $C_1$  is derived as

$$V_{C1} = V_{N2}^{II} - V_{N2}^{I} + V_{Cc} + V_{C\ell 1} + V_{C\ell 2} = \frac{3n+1}{1-D}V_{in}$$

(15)

According to (13)–(15), the output voltage can be obtained as follows:

$$V_o = V_{C1} + V_{C2} + V_{C3} = \frac{5n+1}{1-D} V_{in}$$

(16)

Hence, we have the ideal voltage gain M of the proposed converter as

$$M = \frac{V_o}{V_{in}} = \frac{5n+1}{1-D}$$

(17)

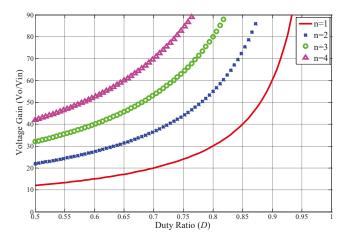

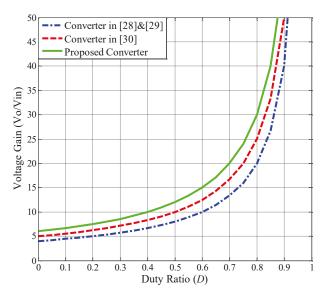

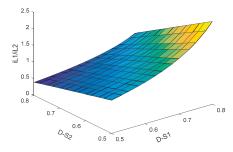

The plot of voltage gain M versus turns ratio n and duty ratio D is drawn in Figure 5. It shows that the turns ratio has a significant impact on the step-up voltage gain. In addition, the high voltage gain can be achieved without any extreme duty ratio or high turns ratio in the proposed converter. When the duty ratio is merely 0.6 and turns ratio n = 1, the voltage gain is calculated as 15.

Figure 5. Voltage gain curve versus duty ratio with different turns ratio.

#### 3.2. Voltage Stresses on Semiconductor Devices

The steady-state analysis reveals that the voltage on the power switches and the clamp diodes during their off-state are all equal to the voltage on the clamp capacitor. From Equations (9) and (17), the voltage stresses are given by

$$V_{S1} = V_{S2} = V_{Dc1} = V_{Dc2} = V_{Cc} = \frac{1}{1 - D} V_{in} = \frac{1}{5n + 1} V_o$$

(18)

Moreover, the voltage stress on the switching diode  $D_{s1}$  can be derived as

$$V_{Ds1} = V_{C2} + V_{C3} = \frac{2n}{1-D} V_{in} = \frac{2n}{5n+1} V_o$$

(19)

The voltage stress on the output diode  $D_0$  is given by

$$V_{Do} = V_{C1} - V_{C\ell 1} - V_{Cc} = \frac{2n}{1 - D} V_{in} = \frac{2n}{5n + 1} V_o$$

(20)

Similarly, the voltage stresses on the diodes  $D_{s2}$ ,  $D_{\ell 1}$  and  $D_{\ell 2}$  can be derived as

$$V_{Ds2} = V_{D\ell 1} = V_{D\ell 2} = \frac{2n}{1 - D} V_{in} = \frac{2n}{5n + 1} V_o$$

(21)

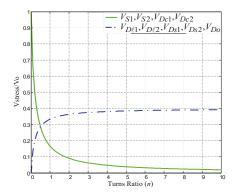

From Equations (18)–(21), the relationship between the normalized voltage stresses on semiconductor devices and the turns ratio of the coupled inductors is shown in Figure 6.

Figure 6. Normalized voltage stresses on semiconductor devices.

As the turns ratio increases, the voltage stresses on  $S_1$ ,  $S_2$ ,  $D_{c1}$  and  $D_{c2}$  decrease, and the voltage stresses on the other diodes become large. It is worth noting that the voltage stresses are lower than the output voltage. As a result, power MOSFETs with low  $R_{ds(ON)}$  and diodes with low forward voltage drop can be employed to reduce the on-state losses and improve the conversion efficiency.

#### 3.3. Design Considerations

#### 3.3.1. Design of Coupled Inductors

The turns ratio of the coupled inductors is designed from Equation (17). Once the duty ratio has been selected, the turns ratio n can be properly designed by

$$n = \frac{N_3}{N_1} = \frac{N_2}{N_1} = \frac{(1-D)V_o}{5V_{in}} - \frac{1}{5}$$

(22)

Once the turns ratio of the coupled inductor is obtained, the magnetizing inductance can be determined from the CCM operation mode and an acceptable current ripple. The current ripple on the magnetizing inductor is identical, and given by

$$\Delta i_{Lm} = \frac{V_{in}D}{L_m f_s} \tag{23}$$

where  $f_s$  is the switching frequency. The average magnetizing current can be derived as

$$I_{Lm} = \frac{P_o}{2V_{in}} = \frac{V_o^2}{2V_{in}R}$$

(24)

where  $P_0$  is the output power. For CCM operation, the following condition holds:

$$I_{Lm} - \frac{1}{2}\Delta i_{Lm} > 0 \tag{25}$$

Substituting Equations (23) and (24) into (25), the condition of magnetizing inductance for CCM operation is expressed as

$$L_{\rm m} > \frac{V_{in}^2 D}{P_o f_s} = \frac{D(1-D)^2 V_o^2}{(5n+1)^2 P_o f_s} = \frac{D(1-D)^2 R}{(5n+1)^2 f_s}$$

(26)

#### 3.3.2. Design of Capacitors

The capacitors are determined to limit their voltage ripples to within an acceptable range. The output capacitor  $C_1$  is discharged by the average load current  $I_0$  from Stage 2 to Stage 6. Thus, its voltage ripple can be derived as

$$\Delta V_{\rm C1} = \frac{DI_o}{C_1 f_{\rm s}} \tag{27}$$

Substituting Equations (15) and (17) into (27), the required capacitance is calculated as

$$C_1 = \frac{(5n+1)D}{(3n+1)Rf_s(\Delta V_{C1}/V_{C1})}$$

(28)

which is expressed by the specified voltage ripple on the output capacitor  $C_1$ . Similarly, one can obtain the design of the following capacitors in terms of their own specified voltage ripples:

$$C_2 = C_3 = \frac{(5n+1)D}{nRf_s(\Delta V_{Ci}/V_{Ci})}, \ i = 2, \ 3$$

<sup>(29)</sup>

$$C_c = \frac{5n+1}{Rf_s(\Delta V_{Cc}/V_{Cc})} \tag{30}$$

#### 3.4. Performance Comparison

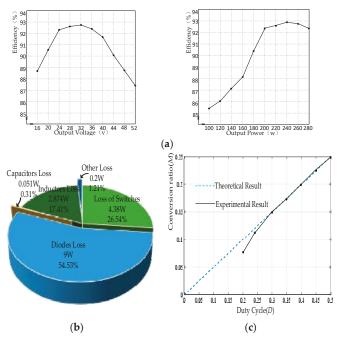

Table 1 shows the performance comparison between the proposed converter and some interleaved high step-up converters published in [28–30], including voltage gain, voltage stress on switches, maximum diode voltage stress and the quantities of the devices. In these comparative converters, three-winding coupled inductors are employed to achieve high step-up voltage gain. Figure 7 shows the voltage gain comparison with turns ratio n = 1. As can be seen, the proposed converter has the highest voltage gain. In addition, it also has the lowest voltage stresses on the switches and diodes. The voltage stresses on the semiconductor devices are lower than the high output voltage, which results in the use of switches with low on-resistance and diodes with low forward voltage drop to reduce the conduction losses and improve the conversion efficiency. As a result, it is clear that the proposed converter is very suitable for applications requiring high efficiency and a high step-up voltage conversion ratio.

$$C_{\ell 1} = C_{\ell 2} = \frac{5n+1}{nRf_{s}(\Delta V_{C\ell j}/V_{C\ell j})}, j = 1,2$$

(31)

| Converter                          | Converter in [28]                  | Converter in [29]        | Converter in [30]                 | Proposed Converter                                   |

|------------------------------------|------------------------------------|--------------------------|-----------------------------------|------------------------------------------------------|

| Voltage gain                       | $\frac{2n+2}{1-D}$                 | $\frac{2n+2}{1-D}$       | $\frac{3n+1}{1}$                  | $\frac{5n+1}{1-D}$                                   |

| Voltage stress on switches         | $\frac{1}{\overline{V}_o^D}{2n+2}$ | $\frac{V_o^D}{2n+2}$     | $\frac{1 \overline{V}_o^D}{3n+1}$ |                                                      |

| Maximum diode voltage stress       | $\frac{(2n+1)V_o}{2n+2}$           | $\frac{(2n+1)V_o}{2n+2}$ | $\frac{3n+1}{\frac{2nV_o}{3n+1}}$ | $\frac{\overline{5n+1}}{2nV_o}$<br>$\overline{5n+1}$ |

| Quantities of switches             | 2                                  | 2                        | 2                                 | 2                                                    |

| Quantities of diodes               | 6                                  | 6                        | 8                                 | 7                                                    |

| Quantities of capacitors           | 5                                  | 5                        | 7                                 | 6                                                    |

| Quantities of coupled inductors    | 2                                  | 2                        | 2                                 | 2                                                    |

| Maximal efficiency at output power | 95.8% at 500W                      | 97.2% at 400W            | 97% at 524W                       | 98% at 100W                                          |

Table 1. Performance comparison of characteristics.

**Figure 7.** Voltage gain comparison with turns ratio n = 1.

#### 4. Controller Design

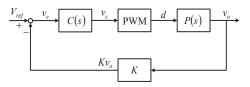

For the purposes of the output voltage regulation, regardless of the variations of input voltage and output load, the voltage-mode feedback control system was built as shown in Figure 8. Blocks C(s) and PWM represent the controller and pulse-width modulator, respectively. Block P(s) denotes the converter power stage. Block K denotes the sensor gain.

Figure 8. Control system block diagram.

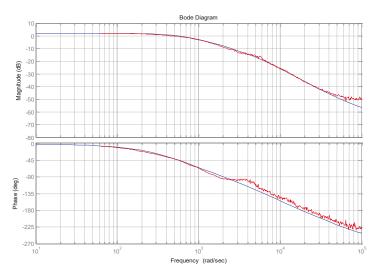

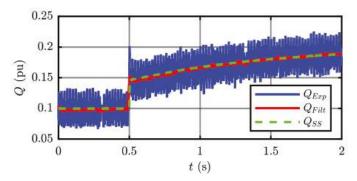

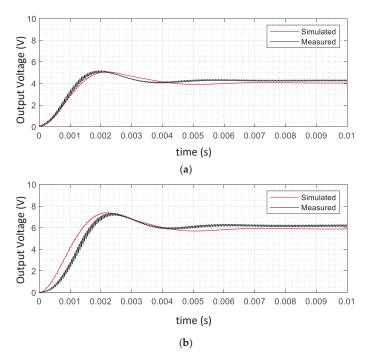

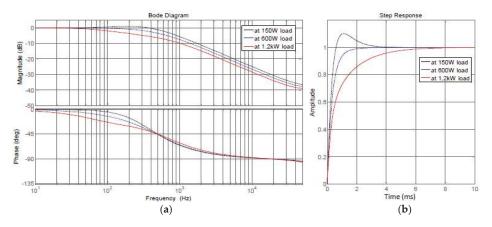

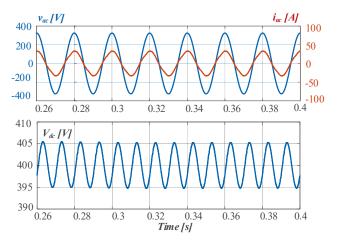

A small-signal model was investigated through the frequency response with experimental measurements for the prototype converter. The electrical specifications and component parameters of the prototype converter are shown in Table 2. The experimental frequency response at the operating point of half load was measured by an NF FRA5012 frequency response analyzer. The Bode plot of the measured transfer function from control to scaled output voltage ( $\tilde{v}_c$  to  $K\tilde{v}_o$ ) is shown in Figure 9 with red curves. The corresponding transfer function can be obtained by the curve-fitting method, and it is given by

$$G(s) = \frac{K\widetilde{v}_o(s)}{\widetilde{v}_c(s)} = \frac{138.3(s - 45000)}{(s + 700)(s + 7000)}$$

(32)

| Parameter/Description                                                                            | Specification/Value |  |  |

|--------------------------------------------------------------------------------------------------|---------------------|--|--|

| Input voltage V <sub>in</sub>                                                                    | 28 V                |  |  |

| Output voltage $V_o$                                                                             | 380 V               |  |  |

| Rated output power $P_{o}$                                                                       | 1000 W              |  |  |

| Switching frequency $f_s$                                                                        | 50 kHz              |  |  |

| Magnetizing inductance $L_m$                                                                     | 69 µH               |  |  |

| Leakage inductance $L_k$                                                                         | 0.7 μΗ              |  |  |

| Turns ratio <i>n</i>                                                                             | 1                   |  |  |

| Power switches $S_1$ and $S_2$                                                                   | IRFP4668            |  |  |

| Diodes $D_{C1}$ , $D_{C2}$ , $D_{\ell 1}$ , $D_{\ell 2}$ , $D_{S1}$ , $D_{S2}$ and $D_{\varrho}$ | 60CPQ150            |  |  |

| Clamp capacitor $C_C$                                                                            | 147 µF              |  |  |

| Lift capacitors $C_{\ell 1}$ and $C_{\ell 2}$                                                    | 147 µF              |  |  |

| Output capacitors $C_1$ , $C_2$ and $C_3$                                                        | 120 µF              |  |  |

Table 2. Electrical specifications and parameters of the prototype converter.

Figure 9. Comparison between measured (red) and curve-fitting (blue).

The Bode plot of the curve-fitting transfer function in Equation (32), together with the measured results, is shown in Figure 9. Comparing the magnitude and phase curves, it can be seen that the curves agree well with each other. Thus, the curve-fitting transfer function expressed in Equation (32) can be used for the controller design.

Based on the *K*-factor method [31], a type III controller [32] with three-pole and two-zero was designed for the closed-loop control system. One of the poles of the controller was located at the origin to achieve the zero steady-state error, while the other two poles were positioned below the desired crossover frequency to attenuate the switching noises in the feedback loop. In addition, the zeros and gain of the controller were adjusted to achieve the desired phase margin at the crossover frequency. The controller transfer function was designed as

$$C(s) = 3.3 \times 10^6 \frac{(s + 2659)(s + 2673)}{s(s + 1.49 \times 10^4)^2}$$

(33)

Energies 2020, 13, 2537

The controller was implemented by the operational amplifier circuit, as shown in Figure 10, and its transfer function is given by

$$\frac{\widetilde{v}_{c}(s)}{K\widetilde{v}_{o}(s)} = -\frac{R_{1} + R_{3}}{R_{1}R_{3}C_{2}} \frac{\left(s + \frac{1}{R_{2}C_{1}}\right)\left(s + \frac{1}{(R_{1} + R_{3})C_{3}}\right)}{s\left(s + \frac{1}{R_{2}C_{1}C_{2}/(C_{1} + C_{2})}\right)\left(s + \frac{1}{R_{3}C_{3}}\right)}$$

$$\begin{array}{c}

C_{2} \\

R_{3} & C_{3} \\

Kv_{o} & R_{1} \\

V_{ref} & + \end{array}$$

$$(34)$$

Figure 10. Controller circuit.

V<sub>ref</sub> –

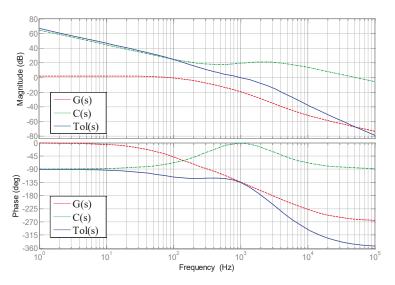

The Bode plots of the plant G(s), the controller C(s) and the loop gain Tol(s) = G(s)C(s) are shown in Figure 11. As a result, a crossover frequency of 1 kHz and a phase margin of 45° were achieved for the output voltage controlled system.

Figure 11. Bode plots of plant, controller and loop gain.

#### 5. Experimental Verification

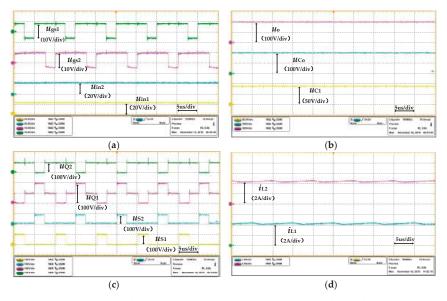

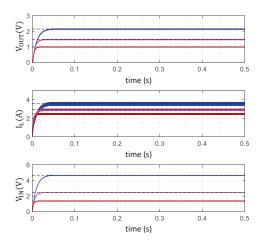

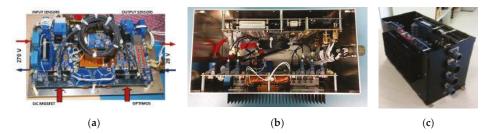

An experimental prototype with maximal output power 1 kW was implemented and tested to verify the performance of the proposed converter. Table 2 shows the components and parameters of the prototype converter [33]. Figures 12–16 show the simulated results using IsSpice software and the experimental results under full load 1 kW condition, as described below.

Figure 12. Waveforms of  $v_{gs1}$ ,  $v_{gs2}$ ,  $V_{in}$  and  $V_o$ . (a) Simulated results. (b) Experimental results.

**Figure 13.** Waveforms of  $v_{gs1}$ ,  $v_{gs2}$ ,  $v_{ds1}$  and  $v_{ds2}$ . (a) Simulated results. (b) Experimental results.

**Figure 14.** Waveforms of  $i_{in}$ ,  $i_{Lk1}$  and  $i_{Lk2}$ . (a) Simulated results. (b) Experimental results.

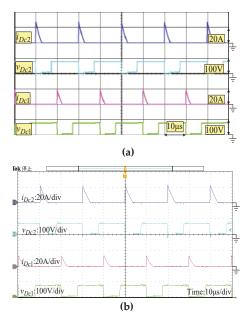

Figure 15. Waveforms of  $i_{Dc1}$ ,  $v_{Dc1}$ ,  $i_{Dc2}$  and  $v_{Dc2}$ . (a) Simulated results. (b) Experimental results.

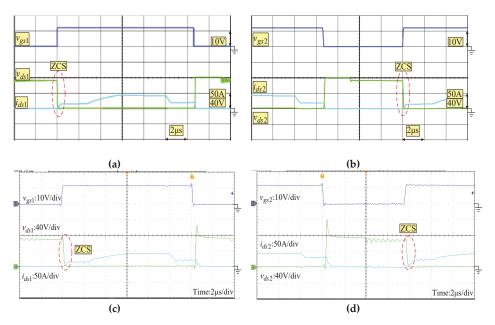

**Figure 16.** Waveforms of the ZCS turn-on for switches  $S_1$  and  $S_2$ . (**a**) and (**b**) simulated results. (**c**) and (**d**) experimental results.

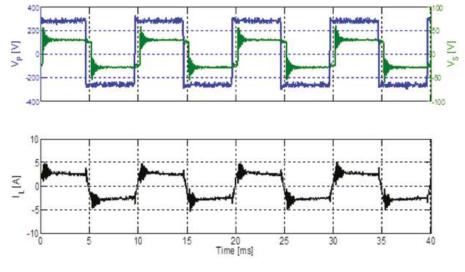

Figure 12 shows the waveforms of  $V_{in}$ ,  $V_o$ , and the gate signals  $v_{gs1}$  and  $v_{gs2}$ , for the switches  $S_1$  and  $S_2$  with interleaved operation. It can be seen that the high voltage gain was over 13 times; however, the duty ratios of the switches were not extremely large.

Figure 13 illustrates the gate signals and the drain-source voltage waveforms  $v_{ds1}$  and  $v_{ds2}$  for the switches  $S_1$  and  $S_2$ . It was observed that the voltage stress on  $S_1$  and  $S_2$  was only about 63 V, which is  $V_o/6$ . The switch voltage stress was much lower than the output voltage. This result meets with that of the steady-state analysis in Equation (18). Therefore, the power switch with a low voltage rating and low on-resistance can be chosen to reduce the conduction losses.

Figure 14 represents the input current  $i_{in}$  and the leakage inductor currents  $i_{Lk1}$  and  $i_{Lk2}$ . Since the input current  $i_{in}$  is equal to  $i_{Lk1}$  plus  $i_{Lk2}$ , one can see that the interleaved operation helps the ripple current cancellation. Consequently, the input current ripple is really small. The ripple current reduction is helpful for the lifetime of green energy sources. Moreover, a good input current sharing capability can be observed by the leakage inductor currents for the two phases of the proposed converter.

Figure 15 exhibits the currents and voltage waveforms on the clamped diodes  $D_{c1}$  and  $D_{c2}$ . One can see that the voltage stress on the diodes is about 63 V, which is only one-sixth of the output voltage. The experimental results show good agreement with the theoretical result in (18). In addition, as can be seen, the currents  $i_{Dc1}$  and  $i_{Dc2}$  fell to zero, and then the considered diodes turned off with the ZCS operation, which is consistent with the operating analysis in stages 3 and 7. Thus, there are no reverse-recovery losses for the clamped diodes  $D_{c1}$  and  $D_{c2}$ .

In Figure 16, the simulated and experimental waveforms of the voltages and the currents on the switches  $S_1$  and  $S_2$  are illustrated. It can be seen that the power switches can achieve ZCS turn-on operation. The switching losses are reduced accordingly for high efficiency.

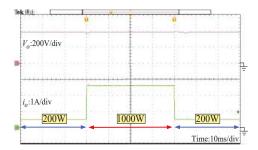

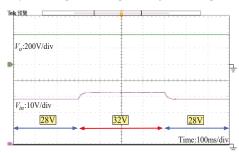

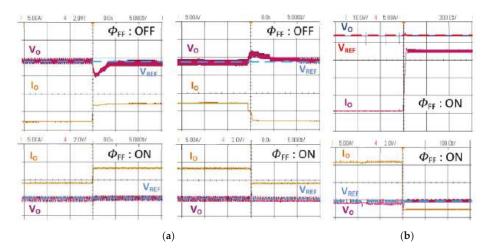

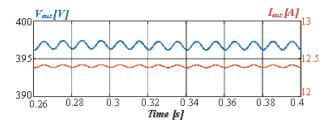

Figure 17 shows the dynamic response of the output voltage under the load variation between 200W and 1000W using a dc electronic load. The dynamic response of the output voltage under the input voltage varying from 28 V to 32 V, and vice versa, is shown in Figure 18. As shown in the figures, the output voltage is insensitive to the load change and input voltage variation. It means that the

well dynamic performance of the output voltage regulation can be provided with the closed-loop controller design.

Figure 17. Dynamic response of output voltage under step load variation.

Figure 18. Dynamic response of output voltage under input voltage variation.

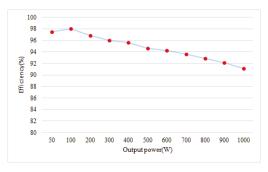

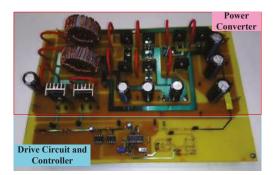

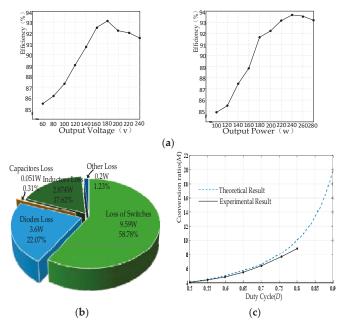

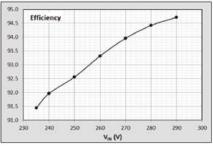

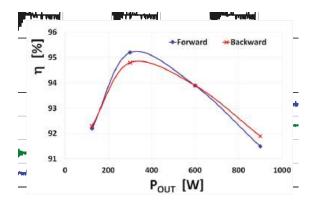

Figure 19 represents the conversion efficiency of the prototype converter under various output powers. A high precision power analyzer (HIOKI 3390) was employed to measure the power conversion efficiency, which is the ratio of the measured output power over the measured input power, Pout/Pin. The measured maximum conversion efficiency was up to 98%, which was obtained at the output power of 100 W. Moreover, the conversion efficiency was 91.08% at the full-load condition. At higher output power, the on-state conduction losses of switching devices are high. Then, the efficiency decreases. The photograph of the laboratory prototype is illustrated in Figure 20.

Figure 19. Power conversion efficiency.

Figure 20. Photograph of the laboratory prototype.

#### 6. Conclusions

The three-winding coupled inductors and voltage multiplier cells, and the voltage-lift and voltage-stack techniques were utilized to create a novel high step-up DC–DC converter configuration, which is suitable for applications in PV generation systems. The proposed high step-up converter gets high voltage gain conversion with proper duty ratio operation and low voltage stresses on the switches and diodes. Switches with smaller on-resistance and diodes with lower forward voltage drop can thereby be used to reduce the conduction losses. The interleaved operation reduces the input current ripple. Moreover, the diode reverse-recovery loss is alleviated due to the leakage inductances of the coupled inductors. The leakage inductor energy is absorbed and recycled to improve efficiency. This paper presented the operating principle and steady-state analysis of the proposed converter. The closed-loop controller is also well designed for the output voltage regulation, regardless of the variations in the input voltage or output load. Finally, a 1 kW laboratory prototype was tested to verify the performance and the presented analysis. The experimental results showed that the proposed converter is suitable for high efficiency and high voltage gain in DC–DC conversion.

Author Contributions: S.-J.C. and S.-P.Y.: analysis and design. Y.-H.C.: experiment. C.-M.H.: supervision and inspection. S.-J.C. and S.-P.Y.: writing and editing. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was financially supported by the Green Energy Technology Research Center from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education (MOE) in Taiwan, and the Ministry of Science and Technology, Taiwan, under grant numbers MOST 108-2221-E-168-004.

Conflicts of Interest: The authors declare that there is no conflict of interest.

#### References

- Ajami, A.; Ardi, H.; Farakhor, A. A novel high step-up DC-DC converter based on integrating coupled inductor and switched-capacitor techniques for renewable energy applications. *IEEE Trans. Power Electron.* 2015, 30, 4255–4263. [CrossRef]

- Yang, B.; Li, W.; Zhao, Y.; He, X. Design and analysis of a grid connected PV power system. *IEEE Trans. Power Electron.* 2010, 25, 992–1000. [CrossRef]

- Carrasco, J.M.; Franquelo, L.G.; Bialasiewicz, J.T.; Galvan, E.; PortilloGuisado, R.C.; Prats, M.A.M.; Leon, J.I.; Moreno-Alfonso, N. Power-electronic systems for the grid integration of renewable energy sources: A survey. *IEEE Trans. Ind. Electron.* 2006, 53, 1002–1016. [CrossRef]

- Andrade, A.M.; Schuch, L.; Martins, M.L.S. Analysis and design of high-efficiency hybrid high step-up DC-DC converter for distributed PV generation systems. *IEEE Trans. Ind. Electron.* 2019, 66, 3860–3868. [CrossRef]

- Tofoli, F.L.; Pereira, D.C.; Paula, W.J.; Junior, D.S.O. Survey on non-isolated high-voltage step-up DC–DC topologies based on the boost converter. *IET Power Electron.* 2015, *8*, 2044–2057. [CrossRef]

- Wong, Y.S.; Chen, J.F.; Liu, K.B.; Hsieh, Y.P. A novel high step-up DC-DC converter with coupled inductor and switched clamp capacitor techniques for photovoltaic systems. *Energies* 2017, 10, 378–394. [CrossRef]

- Hu, X.; Gong, C. A high voltage gain DC-DC converter integrating coupled-inductor and diode-capacitor techniques. *IEEE Trans. Power Electron.* 2014, 29, 789–800.

- Farakhor, A.; Abapour, M.; Sabahi, M.; Farkoush, S.G.; Oh, S.R.; Rhee, S.B. A study on an improved three-winding coupled inductor based dc/dc boost converter with continuous input current. *Energies* 2020, 13, 1780. [CrossRef]

- 9. Tseng, K.C.; Lin, J.T.; Huang, C.C. High step-up converter with three-winding coupled inductor for fuel cell energy source applications. *IEEE Trans. Power Electron.* **2015**, *30*, 574–581. [CrossRef]

- 10. Yu, D.; Yang, J.; Xu, R.; Xia, Z.; Iu, H.H.; Fernando, T. A family of module-integrated high step-up converters with dual coupled inductors. *IEEE Access* 2018, *6*, 16256–16266. [CrossRef]

- Azizkandi, M.E.; Sedaghati, F.; Shayeghi, H.; Blaabjerg, F. Two- and three-winding coupled-inductor-based high step-up DC–DC converters for sustainable energy applications. *IET Power Electron.* 2020, 13, 144–156.

- Gao, Y.; Liu, H.; Ai, J. Novel high step-up DC–DC converter with three-winding-coupled-inductors and its derivatives for a distributed generation system. *Energies* 2018, *11*, 3428. [CrossRef]

- Azizkandi, M.E.; Sedaghati, F.; Shayeghi, H.; Blaabjerg, F. A high voltage gain DC–DC converter based on three winding coupled inductor and voltage multiplier cell. *IEEE Tran. Power Electron.* 2020, 35, 4558–4567. [CrossRef]

- Wei, C.L.; Shih, M.H. Design of a switched-capacitor DC-DC converter with a wide input voltage range. *IEEE Trans. Circuits Syst.* 2013, 60, 1648–1656. [CrossRef]

- 15. Tang, Y.; Fu, D.; Wang, T.; Xu, Z. Hybrid switched-inductor converters for high step-up conversion. *IEEE Trans. Ind. Electron.* **2015**, *62*, 1480–1490. [CrossRef]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Switched-capacitor/switched-inductor structures for getting transformerless hybrid DC–DC PWM converters. *IEEE Trans. Circuits Syst.* 2008, 55, 687–696. [CrossRef]

- 17. Salvador, M.A.; Lazzarin, T.B.; Coelho, R.F. High step-up DC-DC converter with active switched-inductor and passive switched-capacitor networks. *IEEE Trans. Ind. Electron.* **2018**, *65*, 5644–5654. [CrossRef]

- Gu, Y.; Chen, Y.; Zhang, B.; Qiu, D.; Xie, F. High step-up DC–DC converter with active switched LC-network for photovoltaic systems. *IEEE Trans. Energy Convers.* 2019, 34, 321–329. [CrossRef]

- 19. Duong, T.D.; Nguyen, M.K.; Tran, T.T.; Lim, Y.C.; Choi, J.H. Transformerless high step-up DC-DC converters with switched-capacitor network. *Electronics* **2019**, *8*, 1420. [CrossRef]

- Lakshmi, M.; Hemamalini, S. Nonisolated high gain DC-DC converter for DC microgrids. *IEEE Trans. Ind. Electron.* 2018, 65, 1205–1212. [CrossRef]

- Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padamanaban, S.; Maroti, P.K.; Alammari, R. High gain transformer-less double-duty-triple-mode DC/DC converter for DC microgrid. *IEEE Access* 2019, 7, 36353–36370. [CrossRef]

- Tseng, K.C.; Chen, C.T.; Cheng, C.A. A high-efficiency high step-up interleaved converter with a voltage multiplier for electric vehicle power management applications. J. Power Electron. 2016, 16, 414–424. [CrossRef]

- Zhou, W.B.; Zhu, X.; Luo, Q.M.; Chen, S. Interleaved non-isolated high step-up dc/dc converter based on the diode-capacitor multiplier. *IET Power Electron.* 2014, 7, 390–397. [CrossRef]

- 24. Li, W.; Zhao, Y.; Deng, Y.; He, X. Interleaved converter with voltage multiplier cell for high step-up and high-efficiency conversion. *IEEE Trans. Power Electron.* **2010**, *25*, 2397–2408. [CrossRef]

- Li, W.; Xiang, X.; Li, C.; Li, W.; He, X. Interleaved high step-up ZVT converter with built-in transformer voltage doubler cell for distributed PV generation system. *IEEE Trans. Power Electron.* 2013, 28, 300–313. [CrossRef]

- 26. Li, W.; Xiang, X.; Hu, Y.; He, X. High step-up interleaved converter with built-in transformer voltage multiplier cells for sustainable energy applications. *IEEE Trans. Power Electron.* **2014**, *29*, 2829–2836. [CrossRef]

- Nouri, T.; Vosoughi, N.; Hosseini, S.H.; Babaei, E.; Sabahi, M. An interleaved high step-up converter with coupled inductor and built-in transformer voltage multiplier cell techniques. *IEEE Trans. Ind. Electron.* 2019, 66, 1894–1905. [CrossRef]

- Li, W.; Zhao, Y.; Wu, J.; He, X. Interleaved high step-up converter with winding-cross-coupled inductors and voltage multiplier cells. *IEEE Trans. Power Electron.* 2012, *27*, 133–143. [CrossRef]

- He, L.; Liao, Y. An advanced current-autobalance high step-up converter with a multicoupled inductor and voltage multiplier for a renewable power generation system. *IEEE Trans. Power Electron.* 2016, 31, 6992–7005.

- Nouri, T.; Hosseini, S.H.; Babaei, E.; Ebrahimi, J. Interleaved high step-up DC–DC converter based on three-winding high-frequency coupled inductor and voltage multiplier cell. *IET Power Electron.* 2015, *8*, 175–189. [CrossRef]

- Venable, D. The K factor: A new mathematical tool for stability analysis and synthesis. *Proc. Powercon* 1983, 10. Available online: http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.196.6850&rep=rep1&type=pdf (accessed on 10 May 2020).

- 32. Cao, L. Type III compensator design for power converters. Power Electron. Technol. 2011, 1, 20–25.

- Chen, S.J.; Yang, S.P.; Huang, C.M.; Chen, Y.H. High step-up interleaved converter with three-winding coupled inductors and voltage multiplier cells. In Proceedings of the 20th IEEE International Conference on Industrial Technology (ICIT), Melbourne, VIC, Australia, 13–15 February 2019; pp. 458–463.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

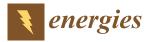

### Article A Multi-Input-Port Bidirectional DC/DC Converter for DC Microgrid Energy Storage System Applications

#### Binxin Zhu<sup>1,2,\*</sup>, Hui Hu<sup>1,2</sup>, Hui Wang<sup>1,2</sup> and Yang Li<sup>3</sup>

- <sup>1</sup> College of Electrical Engineering and New Energy, China Three Gorges University, Yichang 443000, China; huhuictgu@163.com (H.H.); wanghui@ctgu.edu.cn (H.W.)

- <sup>2</sup> Hubei Provincial Key Laboratory for Operation and Control of Cascaded Hydropower Station, China Three Gorges University, Yichang 443000, China

- <sup>3</sup> School of Automation, Wuhan University of Technology, Wuhan 430000, China; yang.li@whut.edu.cn

- \* Correspondence: zhubinxin@ctgu.edu.cn; Tel.: +86-1719-765-0066

Received: 23 April 2020; Accepted: 26 May 2020; Published: 1 June 2020

**Abstract:** A multi-input-port bidirectional DC/DC converter is proposed in this paper for the energy storage systems in DC microgrid. The converter can connect various energy storage batteries to the DC bus at the same time. The proposed converter also has the advantages of low switch voltage stress and high voltage conversion gain. The working principle and performance characteristics of the converter were analyzed in detail, and a 200 W, two-input-port experimental prototype was built. The experimental results are consistent with the theoretical analysis.

Keywords: DC/DC converter; multi-input-port; bidirectional; energy storage

#### 1. Introduction

Due to global issues like the greenhouse effect and energy shortage, renewable energy generation has developed rapidly in recent years [1–3]. Renewable energy generation is greatly affected by natural environmental factors, output power of which exhibits intermittence and randomness [4,5]. DC microgrid and energy storage systems, like batteries and supercapacitors, are usually used to smooth the fluctuating and stochastic output power of the renewable energy generation system [6,7]. A DC/DC converter with the capability of bidirectional energy conversion is the key device to connect batteries and the DC bus of the DC microgrid.

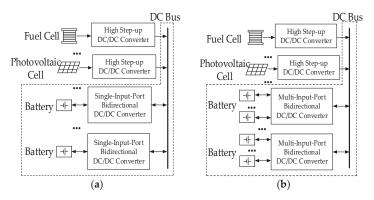

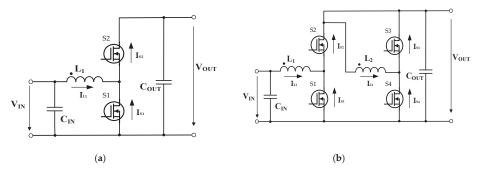

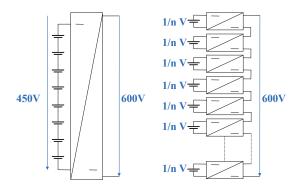

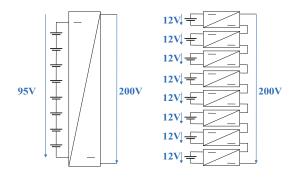

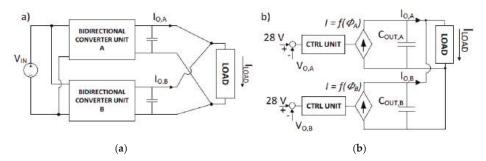

In recent years, many studies have been conducted on bidirectional DC/DC converters [8,9]. Many battery cells were connected in series to achieve high voltage [10]; however, a charge equalization circuit needs to be introduced to solve the problem of unbalanced battery charging [11]. On the contrary, many batteries can also be connected in parallel to achieve high reliability [12], but the output voltage of these batteries is low, and a high voltage gain converter is required in such an application [13,14]. Coupled inductors, switch capacitors, or voltage multiple cells can be used to improve the voltage conversion ratio [15–19]; however, most of the above converters are single input and single output, which means a large number of converters have to be used to connect each battery energy storage unit to the DC bus respectively [20,21], as Figure 1a shows.

Figure 1. A DC microgrid with various battery energy storage systems. (a) traditional converters; (b) proposed converter.

In [22–24], some multi-input-port bidirectional converters have been presented; however, these converters have some common disadvantages, such as a large number of devices, large size, and high cost. A multi-input-port bidirectional DC/DC converter is proposed in this paper, many battery energy storage units can be connected to the DC bus by this converter together, as Figure 1b shows. Both in charging and discharging mode, the power flow to every battery can be controlled easily. Apparently, the cost of the whole system can be reduced.

The paper is organized as follows. The working principle, performance analysis, and extension of the proposed converter are described in Sections 2–4, respectively. In Section 5, the efficacy of the proposed converter is verified experimentally using a 200 W prototype.

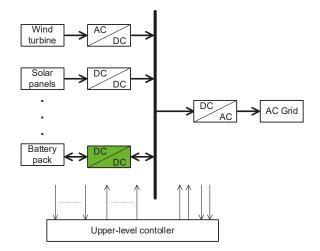

#### 2. Operation Principle of the Proposed Multi-Input-Port Bidirectional DC/DC Converter

The operation principle of the proposed converter will be presented in this section based on a topology with two input ports shown in Figure 2. To simplify the analysis, the following assumptions are made:

- 1. The currents  $i_{L1}$  and  $i_{L2}$  of the inductors  $L_1$  and  $L_2$  are both continuous.

- 2. All devices are ideal, regardless of the influence of parasitic parameters.

- 3. The switches  $S_1$  and  $S_2$  are regulated by an interleaved control strategy with the duty cycle greater than 0.5. While the switches  $Q_1$  and  $Q_2$  are controlled by an interleaved control strategy with the duty cycle less than 0.5. The operation principle of the converter can be analyzed based on the discharging or charging modes.

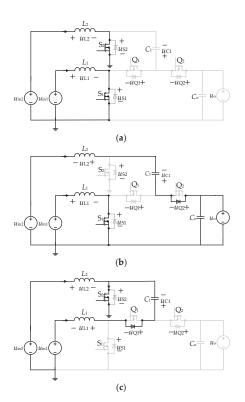

Figure 2. A multi-input-port bidirectional DC/DC converter for energy storage systems in a DC microgrid.

#### 2.1. Discharging Mode (Boost)

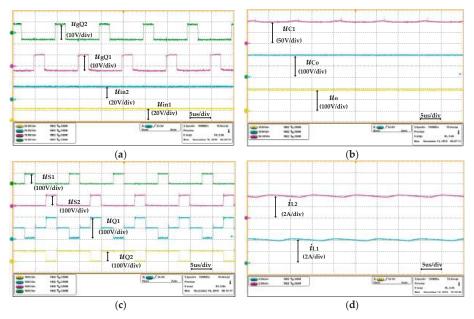

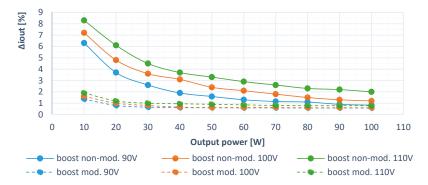

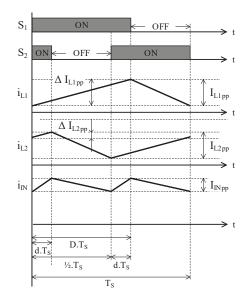

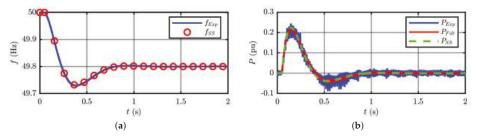

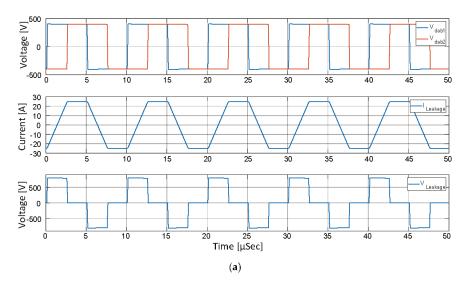

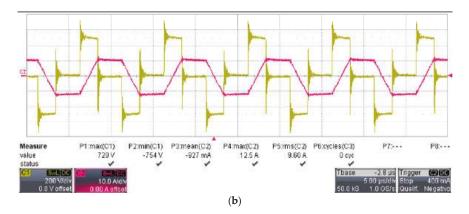

In this mode,  $S_1$  and  $S_2$  are interleaved with  $180^\circ$  phase shift to turn on, and  $Q_1$ ,  $Q_2$  are turned off. During a switching period  $T_s$ , there are three Sub-modes. The main waveforms of the converter working in steady state are shown in Figure 3, and the equivalent circuit of each Sub-mode is shown in Figure 4. The control signals of  $S_1$  and  $S_2$  are denoted by  $u_{gs1}$  and  $u_{gs2}$ , respectively.

**Figure 3.** The main waveforms in one switching period  $T_s$ .

Sub-mode 1 [ $t_0$ – $t_1$ ,  $t_2$ – $t_3$ ]: as Figure 4a shows, S<sub>1</sub> and S<sub>2</sub> are on. The voltages of the inductors  $L_1$  and  $L_2$  are equal to  $u_{in1}$  and  $u_{in2}$ , respectively. The inductor currents increase linearly at the rates of  $u_{in1}/L_1$  and  $u_{in2}/L_2$ , respectively. The current through the capacitor  $C_1$  is zero, while the capacitor voltage is unchanged.

Sub-mode 2  $[t_1-t_2]$ : as Figure 4b shows,  $S_1$  is on, and  $S_2$  is off. Same as Sub-mode 1, the voltage of the inductor  $L_1$  is still  $u_{in1}$ , and the current through it increases linearly at the rate of  $u_{in1}/L_1$ . However, the current through the inductor  $L_2$  decreases at the rate of  $(u_{in2} + u_{C1} - u_0)/L_2$ . The capacitor  $C_1$  is being discharged. The voltage of  $C_1$  decreases linearly, and the current of  $C_1$  is equal to  $i_{L2}$ .

Sub-mode 3  $[t_3-t_4]$ : as Figure 4c shows, S<sub>1</sub> is off, and S<sub>2</sub> is on. The current through the inductor  $L_1$  decreases at the rate of  $(u_{in1} - u_{C1})/L_1$ . The voltage of the inductor  $L_2$  is  $u_{in2}$ , and the current of  $L_2$  increases at the rate of  $u_{in2}/L_2$ . The capacitor  $C_1$  is being charged. The current of the capacitor  $C_1$  is equal to  $i_{L1}$ , and the voltage of  $C_1$  increases linearly.

Figure 4. The equivalent circuits in the discharging mode for (a) Sub-mode 1; (b) Sub-mode 2; (c) Sub-mode 3.

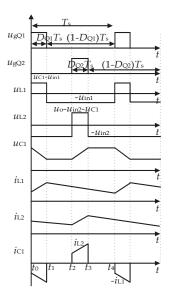

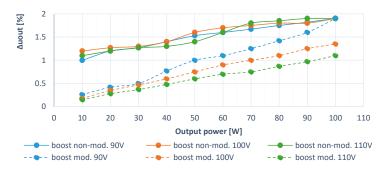

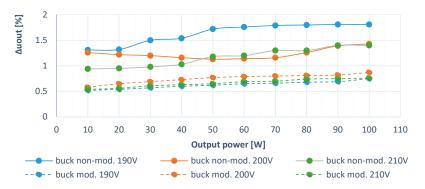

#### 2.2. Charging Mode (Buck)

In this mode,  $Q_1$  and  $Q_2$  are interleaved with 180° phase shift to turn on, and  $S_1$ ,  $S_2$  are off. During a switching period  $T_s$ , there are three Sub-modes. The main waveforms of the converter working in steady state are shown in Figure 5, and the equivalent circuit of each Sub-mode is shown in Figure 6. The control signals of  $Q_1$  and  $Q_2$  are denoted by  $u_{gQ1}$  and  $u_{gQ2}$ , respectively.

Sub-mode 1 [ $t_0-t_1$ ]: as Figure 6a shows,  $Q_1$  is on, and  $Q_2$  is off. The current through the inductor  $L_1$  increases at the rate of  $(u_{C1} - u_{in1})/L_1$ . The voltage of the inductor  $L_2$  is  $u_{in2}$ , and the current of  $L_2$  decreases at the rate of  $u_{in2}/L_2$ . The capacitor  $C_1$  is being discharged. The voltage of  $C_1$  decreases linearly and the current of  $C_1$  is equal to  $i_{L1}$ .

Sub-mode 2 [ $t_1$ – $t_2$ ,  $t_3$ – $t_4$ ]: as Figure 6b shows,  $Q_1$  and  $Q_2$  are off. The voltages of the inductors  $L_1$  and  $L_2$  are  $u_{in1}$  and  $u_{in2}$ , respectively. The inductor currents decrease linearly at the rates of  $u_{in1}/L_1$  and  $u_{in2}/L_2$ , respectively. The current through the capacitor  $C_1$  is zero, while the capacitor voltage is unchanged.

Sub-mode 3  $[t_2-t_3]$ : as Figure 6c shows,  $Q_1$  is off, and  $Q_2$  is on. The current of the inductor  $L_1$  decreases at the rate of  $u_{in1}/L_1$ . However, the current through the inductor  $L_2$  increases at the rate of  $(u_0 - u_{in2} - u_{C1})/L_2$ . The capacitor  $C_1$  is being charged. The current of the capacitor  $C_1$  is equal to  $i_{L2}$ , and the voltage of  $C_1$  increases linearly.

**Figure 5.** The main waveforms in one switching period  $T_s$ .

Figure 6. The equivalent circuits in the charging mode for (a) Sub-mode 1; (b) Sub-mode 2; (c) Sub-mode 3.

#### 3. Performance Analysis

#### 3.1. Voltage Conversion Ratio

Discharging Mode (Boost): According to the analysis of the above working principle, the operating characteristics of the proposed converter can be derived from the three Sub-modes in one switching cycle  $T_{s}$ , based on the voltage-second balance of the inductors  $L_1$  and  $L_2$ .

$$D_{\rm S1}u_{\rm in1} + (1 - D_{\rm S1})(u_{\rm in1} - u_{\rm C1}) = 0 \tag{1}$$

$$D_{S2}u_{in2} + (1 - D_{S2})(u_{in2} + u_{C1} - u_o) = 0$$

<sup>(2)</sup>

From Equations (1) and (2), Equations (3) and (4) can be derived:

$$u_{\rm C1} = \frac{u_{\rm in1}}{1 - D_{\rm S1}} \tag{3}$$

$$u_{\rm o} = \frac{u_{\rm in1}}{1 - D_{\rm S1}} + \frac{u_{\rm in2}}{1 - D_{\rm S2}} \tag{4}$$

According to Equation (4), it can be clearly seen that the voltage conversion ratio of the proposed converter is twice that of the traditional boost converter.

When the input voltages  $u_{in1}$ ,  $u_{in2}$ , and the duty cycle  $D_{S1}$ ,  $D_{S2}$  are the same, respectively, the voltage conversion ratio of the proposed converter can be derived:

$$M_{\rm Boost} = \frac{u_{\rm o}}{u_{\rm in}} = \frac{2}{1 - D_{\rm Boost}} \tag{5}$$

Charging Mode (Buck): According to the analysis of the above working principle, the operating characteristics of the proposed converter can be derived from the Sub-three modes in one switching cycle  $T_{s}$ , based on the voltage-second balance of the inductors  $L_1$  and  $L_2$ .

$$D_{Q1}(u_{C1} - u_{in1}) + (1 - D_{Q1})(-u_{in1}) = 0$$

(6)

$$D_{Q2}(u_{\rm o} - u_{\rm in2} - u_{C1}) + (1 - D_{Q2})(-u_{\rm in2}) = 0$$

<sup>(7)</sup>

From Equations (6) and (7), Equations (8) and (9) can be derived:

$$u_{\rm C1} = \frac{u_{\rm in1}}{D_{\rm Q1}} \tag{8}$$

$$u_{\rm o} = \frac{u_{\rm in1}}{D_{\rm Q1}} + \frac{u_{\rm in2}}{D_{\rm Q2}} \tag{9}$$

When the output voltages  $u_{in1}$ ,  $u_{in2}$ , and the duty cycle  $D_{Q1}$ ,  $D_{Q2}$  are the same, respectively, the voltage conversion ratio of the proposed converter can be derived:

$$M_{\rm Buck} = \frac{u_{\rm in}}{u_{\rm o}} = \frac{D_{\rm Buck}}{2} \tag{10}$$

According to Equation (10), it can be seen that the voltage conversion ratio of the proposed converter is half of that of the traditional buck converter.

#### 3.2. Relationship between the Currents of the Two Inductors

Discharging Mode (Boost): During a switching cycle  $T_s$ , in Sub-mode 3, the capacitor  $C_1$  is charged for  $(1 - D_{S1})T_s$  and the current of  $C_1$  is equal to  $i_{L1}$ . In Sub-mode 2, the capacitor  $C_1$  is discharged for

$(1 - D_{S2})T_s$ , and the current of  $C_1$  is equal to  $i_{L2}$ . In Sub-mode 1, the current of the capacitor  $C_1$  is zero. Due to the ampere-second balance of the capacitor  $C_1$ , the following can be derived:

$$I_{L1}(1 - D_{S1})T_s = I_{L2}(1 - D_{S2})T_s$$

<sup>(11)</sup>

$$I_{L1}(1 - D_{S1}) = I_{L2}(1 - D_{S2})$$

(12)

When the duty cycles  $D_{S1}$  and  $D_{S2}$  are equal, the two input currents are also equal. Thus, automatic current sharing is realized. The power of the two ports can be adjusted through controlling  $D_{S1}$  and  $D_{S2}$ , respectively.

Charging Mode (Buck): During a switching cycle  $T_s$ , in Sub-mode 1, the capacitor  $C_1$  is discharged for  $D_{Q1}T_s$ , and the current of  $C_1$  is equal to  $i_{L1}$ . In Sub-mode 3, the capacitor  $C_1$  is charged for  $D_{Q2}T_s$ , and the current of  $C_1$  is equal to  $i_{L2}$ . In Sub-mode 2, the current of the capacitor  $C_1$  is zero. Due to the ampere-second balance of the capacitor  $C_1$ , the following can be derived:

$$I_{L1}D_{Q1}T_{s} = I_{L2}D_{Q2}T_{s}$$

(13)

$$I_{L1}D_{Q1} = I_{L2}D_{Q2} \tag{14}$$

When the duty cycle  $D_{Q1}$  and  $D_{Q2}$  are equal, the two input currents are also equal. Thus, automatic current sharing is realized. The power of the two ports can be adjusted through controlling  $D_{Q1}$  and  $D_{Q2}$ , respectively.

#### 3.3. Voltage Stress of Switch

The voltage stresses of S<sub>1</sub>, S<sub>2</sub>, Q<sub>1</sub>, and Q<sub>2</sub> can be derived as follows:

1. Discharging Mode (Boost):

$$u_{\rm S1} = u_{\rm C1}$$

(15)

$$u_{\rm S2} = u_{\rm Q2} = u_{\rm o} - u_{\rm C1} \tag{16}$$

$$u_{\rm Q1} = u_{\rm o} \tag{17}$$

2. Charging Mode (Buck):

$$u_{\rm S1} = u_{\rm C1}$$

(18)

$$u_{\rm S2} = u_{\rm Q2} = u_{\rm o} - u_{\rm C1} \tag{19}$$

$$u_{\rm Q1} = u_{\rm o} \tag{20}$$

#### 3.4. Current Stress of Switch

Discharging Mode (Boost): To begin with the time of  $S_1$  turning on, in the following cycle  $T_s$ , the inductor currents  $i_{L1}$ ,  $i_{L2}$  can be represented as

$$i_{L1} = \begin{cases} I_{L1} - \frac{u_{in1}D_{S1}T_s}{2L_1} + \frac{u_{in1}}{L_1}t, & 0 < t \le D_{S1}T_s \\ I_{L1} + \frac{u_{in1}D_{S1}T_s}{2L_1} - \frac{u_{C1}-u_{in1}}{L_1}t, & D_{S1}T_s < t \le T_s \end{cases}$$

(21)

$$i_{L2} = \begin{cases} I_{L2} + \frac{1 - D_{S2}}{2L_2} u_{in2} T_s + \frac{u_{in2}}{2L_2} t, & 0 < t \le (D_{S2} - \frac{1}{2}) T_s \\ I_{L2} + \frac{u_{in2} D_{S2} T_s}{2L_2} - \frac{u_o - u_{C1} - u_{in2}}{L_2} [t - (D_{S2} - \frac{1}{2}) T_s], & (D_{S2} - \frac{1}{2}) T_s < t \le \frac{T_s}{2} \\ I_{L2} - \frac{u_{in2} D_{S2} T_s}{2L_2} + \frac{u_{in2}}{L_2} (t - \frac{T_s}{2}), & \frac{T_s}{2} < t \le T_s \end{cases}$$

(22)

Energies 2020, 13, 2810

According to the three Sub-modes of the circuit, in a switching cycle, the currents through  $S_1$  and  $S_2$  at every stage can be derived as follows:

$$i_{S1} = \begin{cases} i_{L1}, & 0 < t \le D_{S1}T_s \\ 0, & D_{S1}T_s < t \le T_s \end{cases}$$

(23)

$$i_{S2} = \begin{cases} i_{L2}, & 0 < t \le (D_{S2} - \frac{1}{2})T_{s} \\ 0, & (D_{S2} - \frac{1}{2})T_{s} < t \le \frac{T_{s}}{2} \\ i_{L2}, & \frac{T_{s}}{2} < t \le D_{S2}T_{s} \\ i_{L1} + i_{L2}, & D_{S2}T_{s} < t \le T_{s} \end{cases}$$

(24)

From Equations (21)–(24), the currents through  $S_1$ ,  $S_2$ ,  $Q_1$ , and  $Q_2$  can be derived as follows:

$$i_{\rm S1} = i_{\rm Q1} = I_{\rm L1} + \frac{u_{\rm in1}D_{\rm S1}T_{\rm s}}{2L_{\rm 1}}$$

(25)

$$i_{S2} = I_{L1} + \frac{u_{in1}D_{S1}T_s}{2L_1} + I_{L2} + \frac{D_{S2}-1}{2L_2}u_{in2}T_s$$

(26)

$$i_{\rm Q2} = I_{\rm L2} + \frac{u_{\rm in2} D_{\rm S2} T_{\rm s}}{2L_2} \tag{27}$$

Charging Mode (Buck): To begin with the time of  $Q_1$  turning on, in the following cycle  $T_s$ , the inductor currents  $i_{L1}$  and  $i_{L2}$  can be denoted by

$$i_{L1} = \begin{cases} \frac{u_{C1} - u_{in1}}{L_1} t, & 0 < t \le D_{Q1} T_s \\ I_{L1} + \frac{(u_{C1} - u_{in1})D_{Q1} T_s}{2L_1} - \frac{u_{in1}}{L_1} (t - D_{Q1} T_s), & D_{Q1} T_s < t \le T_s \end{cases}$$

(28)

$$i_{L2} = \begin{cases} I_{L2} + \frac{(u_o - u_{C1} - u_{in2})D_{Q2}T_s}{2L_2} - \frac{u_{in2}}{L_2}(\frac{1}{2} - D_{Q2})T_s - \frac{u_{in2}}{L_2}t, & 0 < t \le \frac{1}{2}T_s \\ I_{L2} - \frac{(u_o - u_{C1} - u_{in2})D_{Q2}T_s}{2L_2} + \frac{(u_o - u_{C1} - u_{in2})}{L_2}(t - \frac{1}{2}T_s), & \frac{1}{2}T_s < t \le (\frac{1}{2} + D_{Q2})T_s \\ I_{L2} + \frac{(u_o - u_{C1} - u_{in2})D_{Q2}T_s}{2L_2} - \frac{u_{in2}}{L_2}[t - (\frac{1}{2} + D_{Q2})T_s], & (\frac{1}{2} + D_{Q2})T_s < t \le T_s \end{cases}$$

(29)

According to the three Sub-modes of the circuit, in a switching cycle, the currents through  $Q_1$  and  $Q_2$  at each stage can be derived as follows:

$$i_{Q1} = \begin{cases} i_{L1}, & 0 < t \le D_{Q1} T_s \\ 0, & D_{Q1} T_s < t \le T_s \end{cases}$$

(30)

$$i_{Q2} = \begin{cases} 0, & 0 < t \le \frac{1}{2}T_{s} \\ i_{L2}, & \frac{1}{2}T_{s} < t \le (\frac{1}{2} + D_{Q2})T_{s} \\ 0, & (\frac{1}{2} + D_{Q2})T_{s} < t \le T_{s} \end{cases}$$

(31)

`

From Equations (28)–(31), the currents through  $S_1$ ,  $S_2$ ,  $Q_1$ , and  $Q_2$  can be derived as follows:

$$i_{\rm S1} = i_{\rm Q1} = I_{L1} + \frac{u_{\rm in1}(1 - D_{\rm Q1})T_{\rm s}}{2L_1}$$

(32)

$$i_{\rm Q2} = I_{\rm L2} + \frac{u_{\rm in2}(1 - D_{\rm Q2})T_{\rm s}}{2L_2}$$

(33)

$$i_{S2} = I_{L1} + \frac{u_{in1}(1 - D_{Q1})T_s}{2L_1} + I_{L2} - \frac{u_{in2}(1 - D_{Q2})T_s}{2L_2} + \frac{u_{in2}}{L_2}(\frac{1}{2} - D_{Q1})T_s$$

(34)

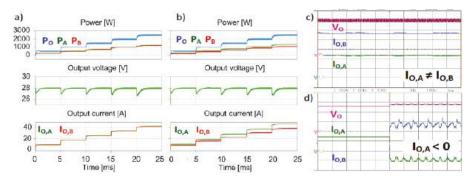

#### 3.5. Power Flow

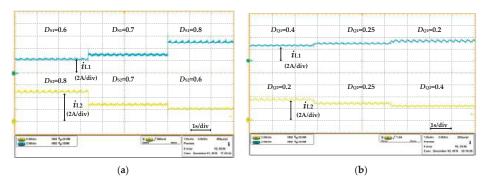

Discharging Mode (Boost): The inductor current  $i_{L1}$  increases as the duty cycle  $D_{S1}$  increases, and the inductor current  $i_{L2}$  decreases as the duty cycle  $D_{S2}$  decreases. Since the two input voltages  $u_{in1}$ ,  $u_{in2}$  are equal, the ratio of the power of the two ports is equal to the ratio of the two inductor currents. Therefore, when  $D_{S1} < D_{S2}$ ,  $i_{L1} < i_{L2}$ ,  $i_{L1}/i_{L2} < 1$ ; when  $D_{S1} = D_{S2}$ ,  $i_{L1} = i_{L2}$ ,  $i_{L1}/i_{L2} = 1$ ; when  $D_{S1} > D_{S2}$ ,  $i_{L1} > i_{L2}$ ,  $i_{L1}/i_{L2} > 1$ . Making  $D_{S1}$ : 0.5–0.8 as the *x*-axis,  $D_{S2}$ : 0.8–0.5 as the *y*-axis, and  $i_{L1}/i_{L2}$  as the *z*-axis, the following three-dimensional figure can be obtained as Figure 7 shows.

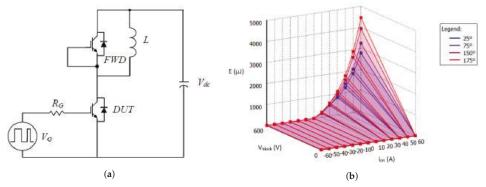

**Figure 7.** *i*<sub>L1</sub>/*i*<sub>L2</sub> 3D graph (Discharging Mode (Boost)).

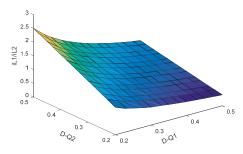

Charging Mode (Buck): The inductor current  $i_{L1}$  increases as the duty cycle  $D_{Q1}$  decreases, and the inductor current  $i_{L2}$  decreases as the duty cycle  $D_{Q2}$  increases. Since the two output voltages  $u_{in1}$ ,  $u_{in2}$  are equal, the ratio of the power of the two ports is equal to the ratio of the two inductor currents. Therefore, when  $D_{Q1} < D_{Q2}$ ,  $i_{L1} > i_{L2}$ ,  $i_{L1}/i_{L2} > 1$ ; when  $D_{Q1} = D_{Q2}$ ,  $i_{L1} = i_{L2}$ ,  $i_{L1}/i_{L2} = 1$ ; when  $D_{Q1} > D_{Q2}$ ,  $i_{L1} < i_{L2}$ ,  $i_{L1}/i_{L2} < 1$ . Making  $D_{Q1}$ : 0.5–0.2 as the *x*-axis,  $D_{Q2}$ : 0.2–0.5 as the *y*-axis, and  $i_{L1}/i_{L2}$  as the *z*-axis, the following three-dimensional figure can be obtained as Figure 8 shows.

Figure 8.  $i_{L1}/i_{L2}$  3D graph (Charging Mode (Buck)).

#### 3.6. Comparison of the Proposed Converter with Other Converters

Some quantitative comparisons between some existing multi-input-port topologies, and the proposed converter are given in Table 1. As can be seen, compared to [22–24], the number of devices of the proposed converter is less, which means fewer losses and a lower cost.

|                   | [22] | [23] | [24] | Proposed |

|-------------------|------|------|------|----------|

| No. of ports      | 3    | 4    | 3    | 3        |

| No. of switches   | 12   | 4    | 6    | 4        |

| No. of diodes     | 0    | 4    | 0    | 0        |

| No. of inductors  | 6    | 4    | 2    | 2        |

| No. of capacitors | 3    | 5    | 2    | 2        |

Table 1. Comparison of the converters.

## 4. Extension of the Topology

4.1. Topology of the N-Input-Port Bidirectional DC/DC Converter

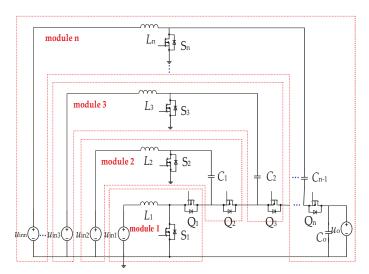

Based on the topology of the two-input-port bidirectional DC/DC converter shown in Figure 2, the n-input-port bidirectional DC/DC converter topology can be derived as Figure 9 shows. To simplify, assumptions are made as follows:

- 1. Currents of the inductors  $i_{L1}$ ,  $i_{L2}$ , ..., and  $i_{L2}$  are all continuous.

- 2. All devices are ideal, regardless of the influence of parasitic parameters.

- 3. Discharging Mode (Boost): during a switching period  $T_s$ ,  $S_1$ ,  $S_2$ , ..., and  $S_n$  interleaved with 360°/n phase shift are turned on with the duty cycle greater than (1 1/n), and  $Q_1$ ,  $Q_2$ , ..., and  $Q_n$  are turned off. Charging Mode (Buck): during a switching period  $T_s$ ,  $Q_1$ ,  $Q_2$ , ..., and  $Q_n$  interleaved with 360°/n phase shift are turned on with the duty cycle less than 1/n, and  $S_1$ ,  $S_2$ , ..., and  $S_n$  are turned off.

Figure 9. An n-input-port bidirectional DC/DC converter for DC microgrid energy storage system.

#### 4.2. Voltage Conversion Ratio

Discharging Mode (Boost): Due to the voltage-second balance of the inductors  $L_1, L_2, ...$ , and  $L_n$ , it can be derived:

$$D_{\mathcal{S}(i-1)}u_{\mathrm{in}(i-1)} = (1 - D_{\mathcal{S}(i-1)})(u_{\mathcal{C}(i-1)} - u_{\mathcal{C}(i-2)} - u_{\mathrm{in}(i-1)})$$

(35)

$$D_{\rm Si}u_{\rm ini} = (1 - D_{\rm Si})(u_{\rm o} - u_{\rm C(i-1)} - u_{\rm ini})$$

(36)

$$u_{Ci} = \sum_{p=1}^{i} \frac{u_{inp}}{1 - D_{Sp}} \ (1 \le i \le n - 1)$$

(37)

$$u_{\rm o} = \sum_{i=1}^{n} \frac{u_{\rm ini}}{1 - D_{\rm Si}} \tag{38}$$

When  $D_{S1} = D_{S2} = ... = D_{sn} = D_{Boost}$ , the ratio of the output voltage  $u_o$ , and each input voltage  $u_{ini}$  is the voltage gain  $M_i$  of each input port.

$$M_i = \frac{u_0}{u_{\text{in}i}} \tag{39}$$

$$\sum_{i=1}^{n} \frac{u_{\text{in}i}}{u_0} = 1 - D_{\text{Boost}} \tag{40}$$

$$\frac{1}{M_1} + \frac{1}{M_2} + \dots + \frac{1}{M_n} = 1 - D_{\text{Boost}}$$

(41)

When  $u_{in1} = u_{in2} = ... = u_{inn}$ ,

$$M_1 = M_2 = \dots = M_n = \frac{n}{1 - D_{Boost}}$$

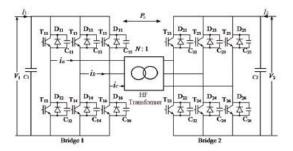

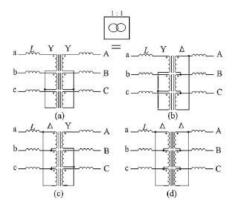

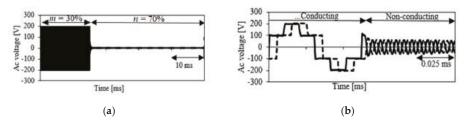

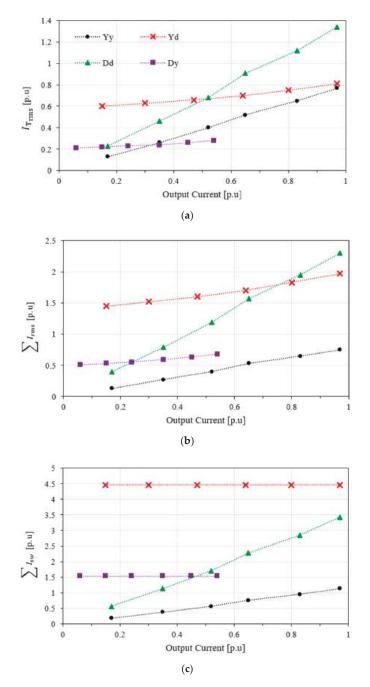

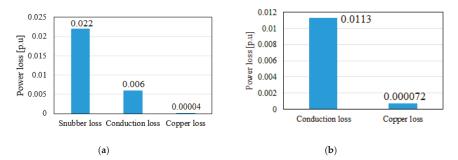

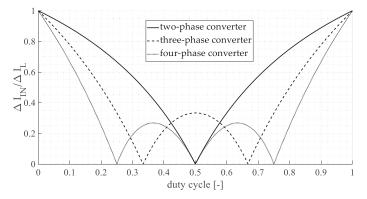

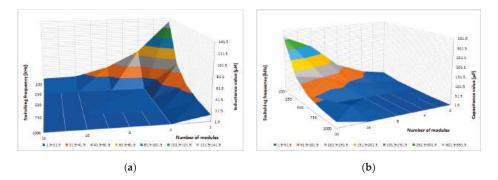

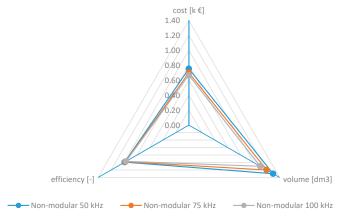

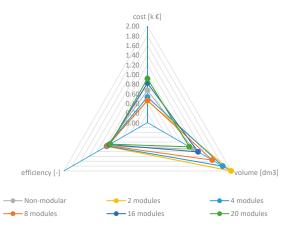

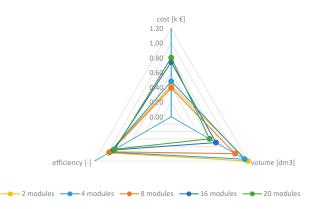

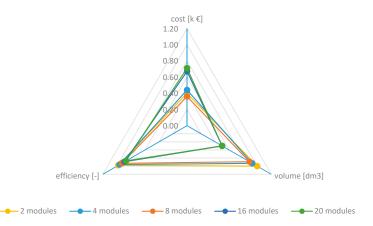

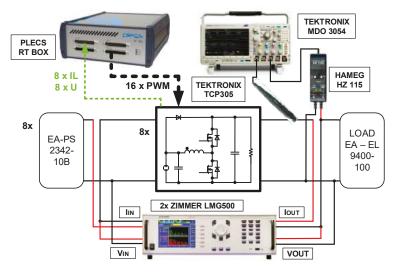

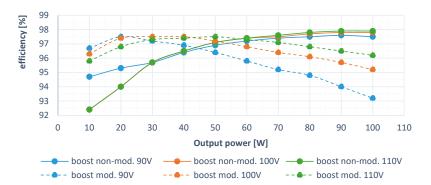

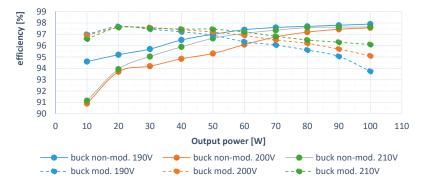

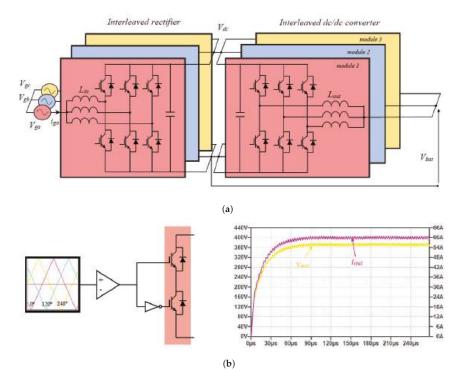

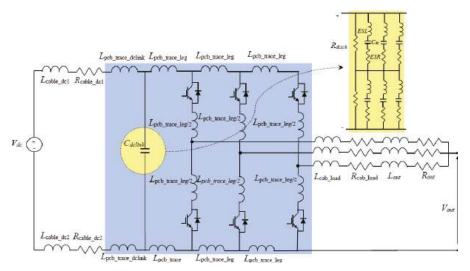

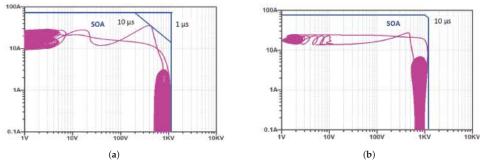

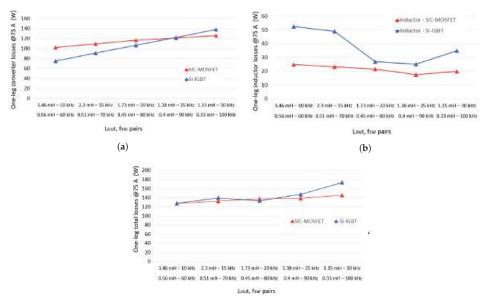

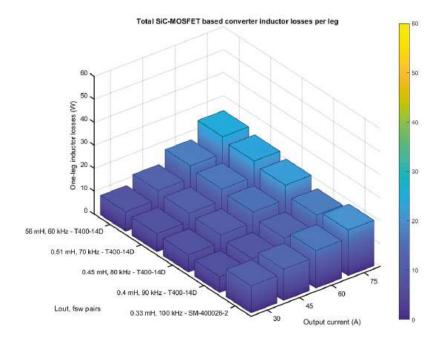

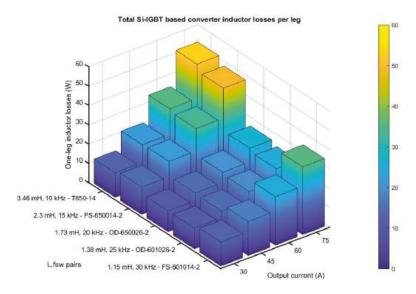

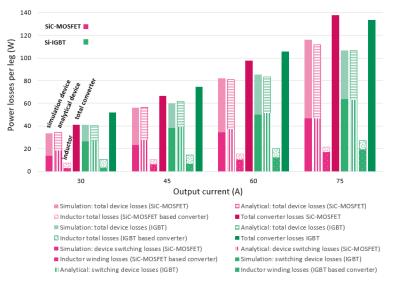

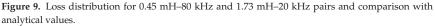

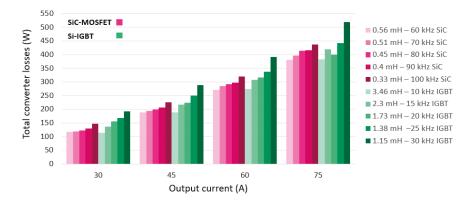

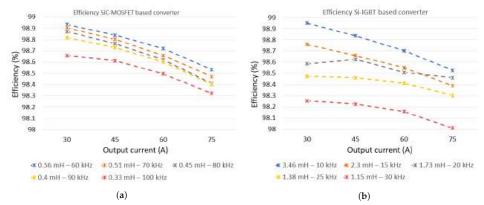

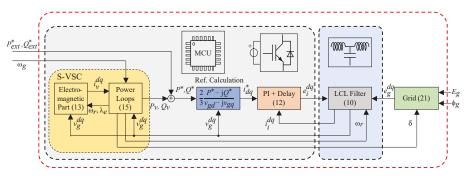

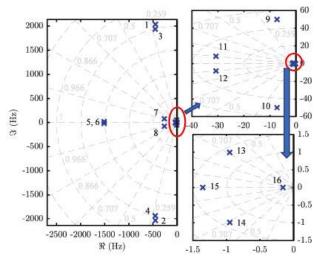

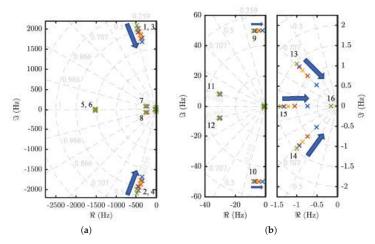

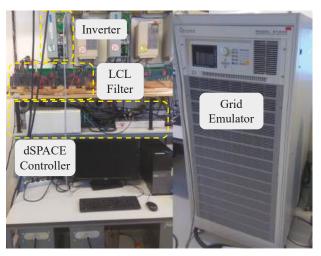

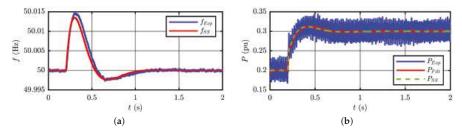

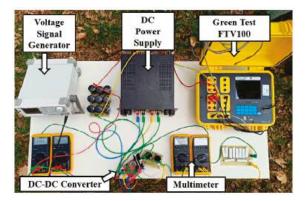

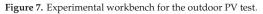

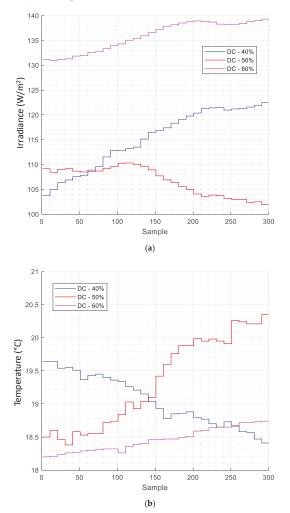

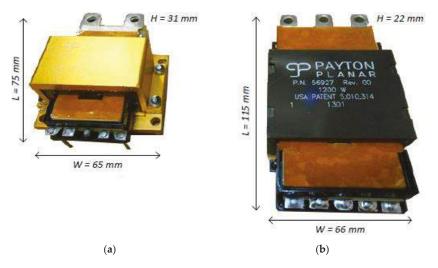

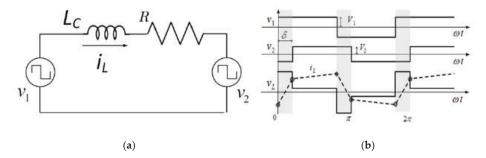

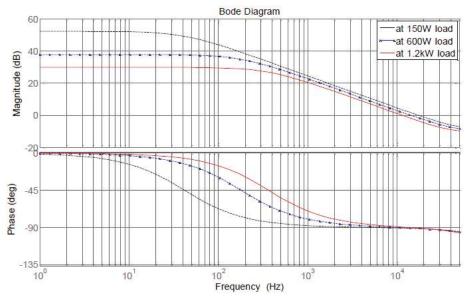

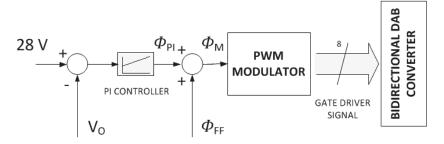

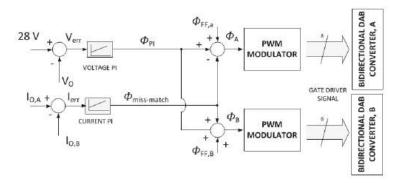

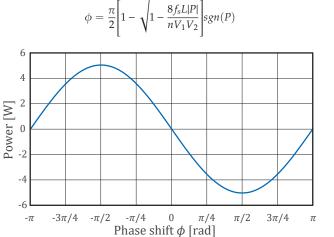

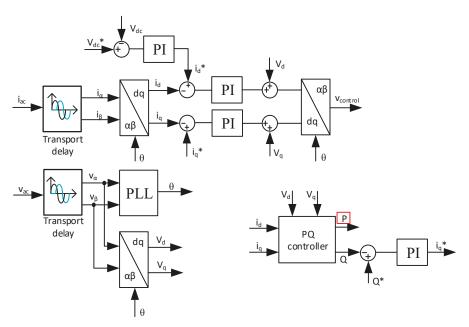

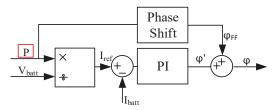

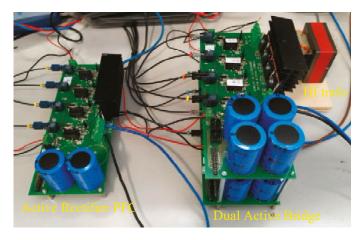

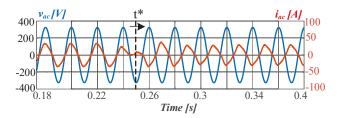

$$\tag{42}$$